TMS320F28335 DSP中文数据手册:全面特性与功能概览

TMS320F28335 DSP 数据手册是针对TI公司生产的TMS320F28335、TMS320F28334以及TMS320F28332系列数字信号控制器(DSC)的官方技术文档。这份手册主要关注于产品的特性和使用指南,包括其硬件设计、功能特性、内存映射和接口详细描述。

1. 特性部分(1.1)介绍了该系列DSP的主要功能,可能包括高处理能力、低功耗设计、以及专为实时应用优化的特性。用户可以在这里找到处理器性能指标、数字信号处理能力等关键信息。

2. 开始使用部分(1.2)指导用户如何启动和配置设备,可能包含电源管理、初始化步骤和基本操作流程,以便快速集成到项目中。

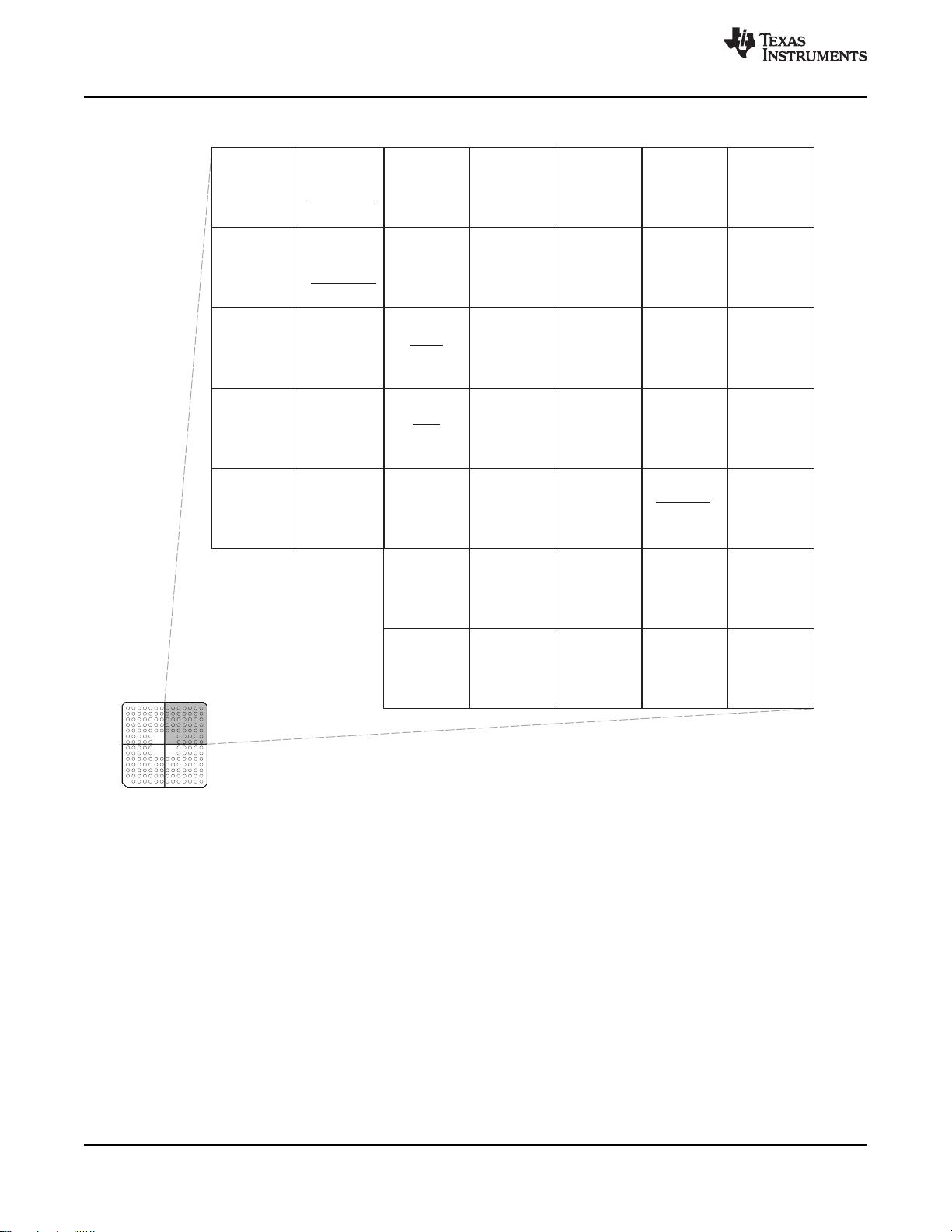

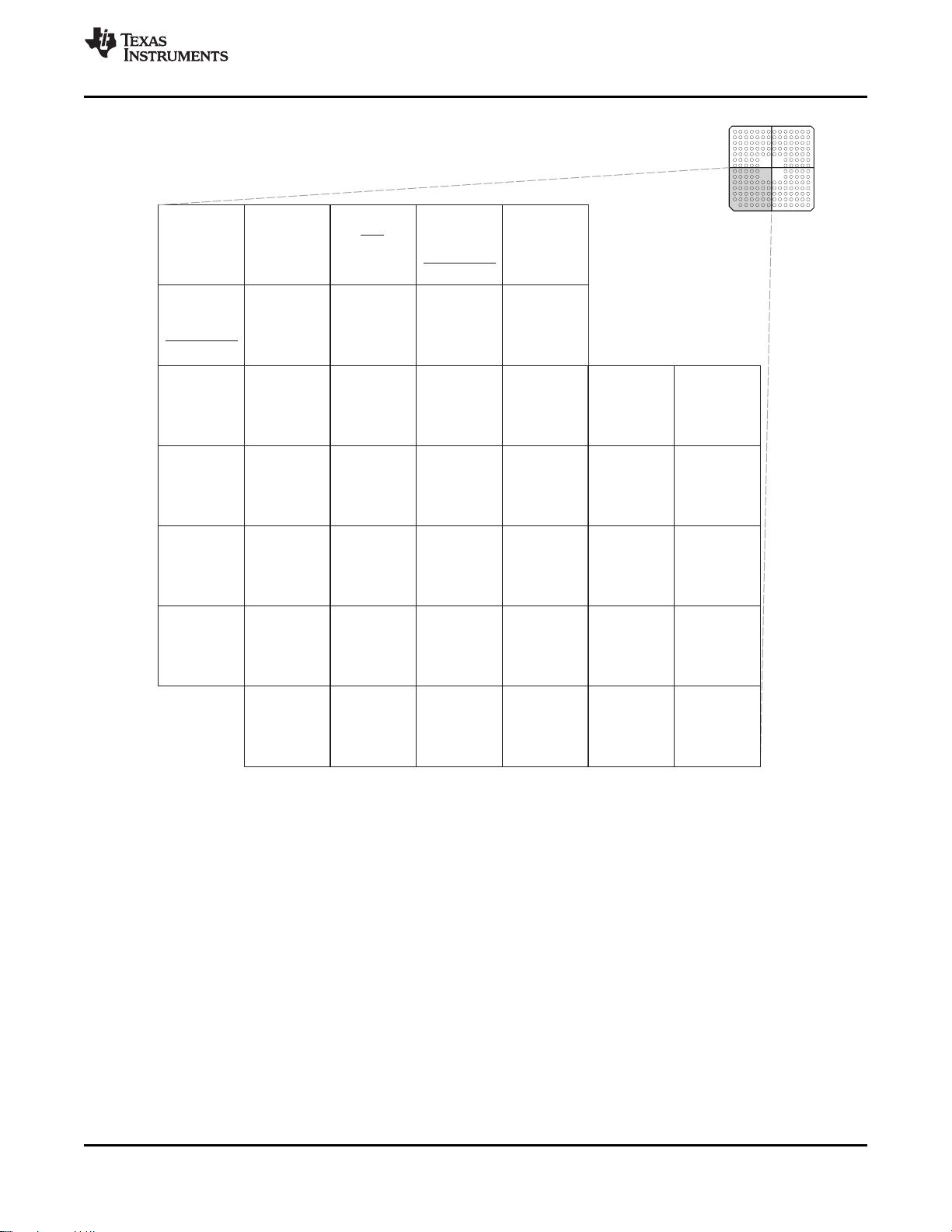

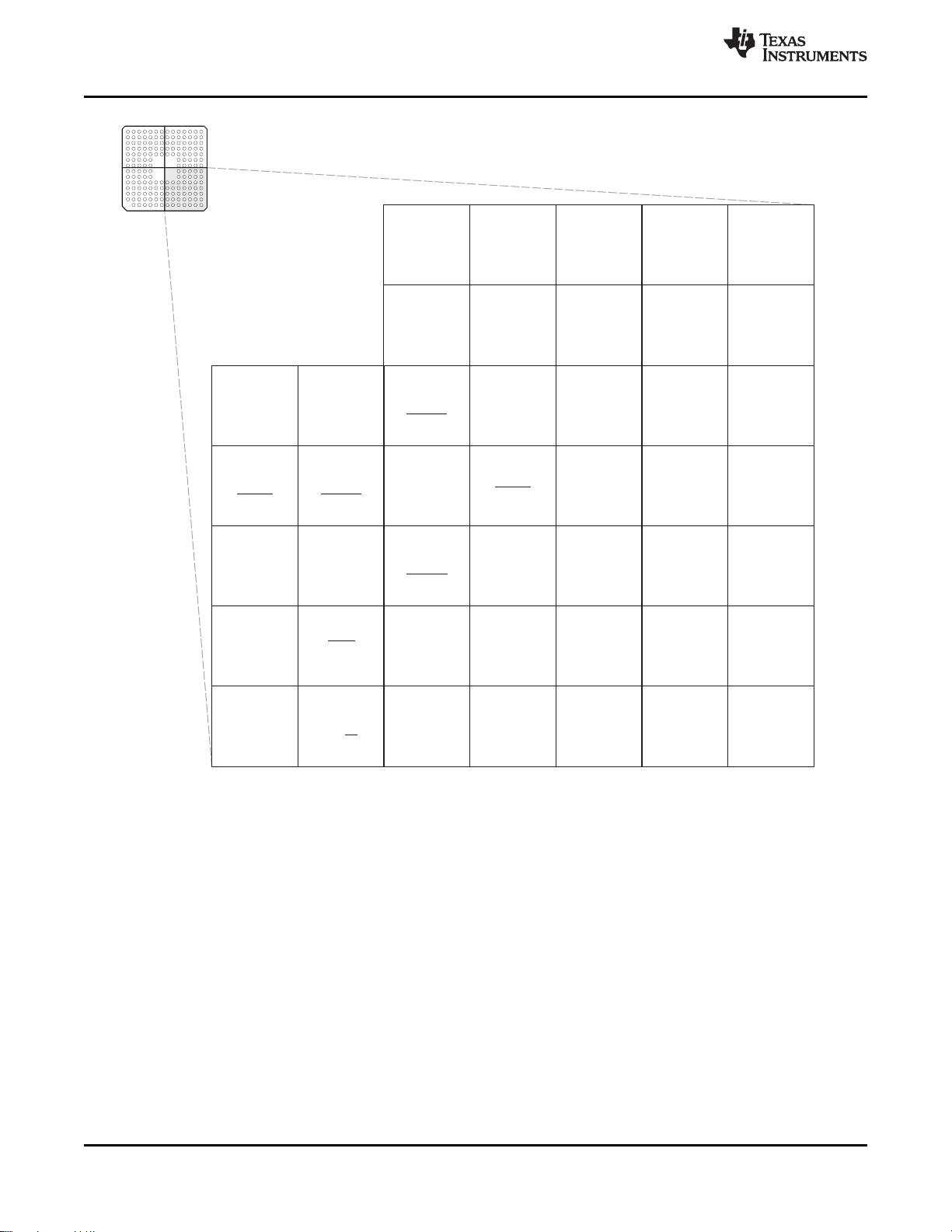

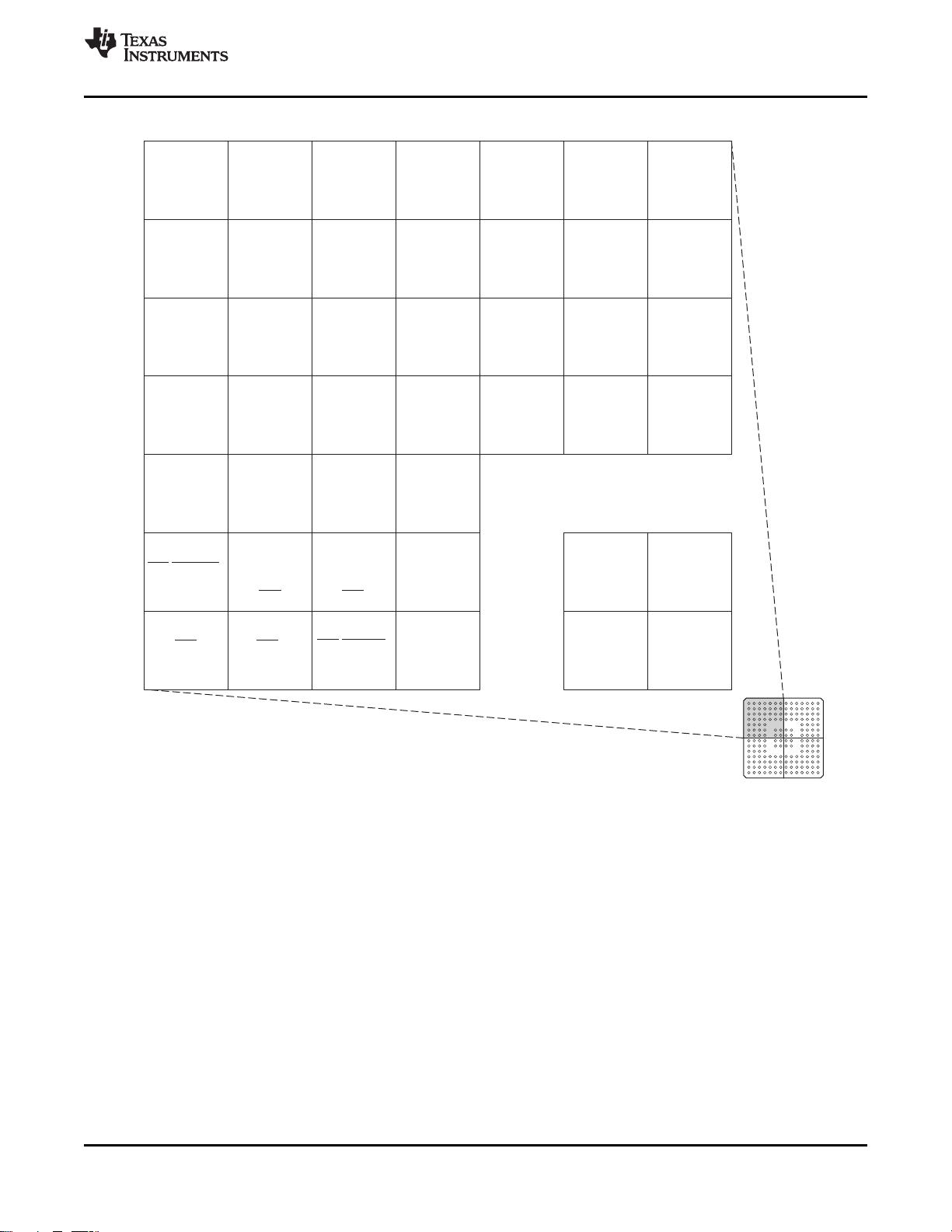

2.1 引脚分配和2.2 信号说明章节详细阐述了DSP的物理接口,包括输入/输出引脚的功能、电源和接地规范,以及重要的模拟和数字信号,有助于理解和连接硬件电路。

3. 功能概述(3.1-33)深入解析了TMS320F28335 DSP的核心组成部分和工作原理。内存映射部分解释了哈弗总线架构如何组织内部存储器,如C28xCPU的寄存器空间、不同等级的SARAM(静态随机访问存储器)以及闪存区域。此外,还涵盖了实时JTAG接口用于调试、外部接口XINTF(外部中断接口)、以及低功耗模式的管理。

- C28xCPU提供了强大的计算能力,支持多任务处理和高效算法实现。

- 外设总线支持多种外设连接,如定时器、计数器、I/O口等,便于系统扩展。

- 安全性功能包括外部中断系统、振荡器和锁相环(PLL)以及专门的安全机制,确保系统的可靠运行。

- 外设中断扩展块( PIE)允许灵活的中断管理和响应策略。

这份手册在2007年6月首次发布,并于2012年8月进行了修订,以反映最新的生产和设计信息。对于任何使用TMS320F28335 DSP的开发人员或工程师来说,它是必备的技术参考文档,提供了解决问题、优化性能和实现高效代码的关键资料。查阅时务必注意生产日期,因为后续的修改可能会包含新的改进和功能。访问TI官方网站ti.com.cn可获取最完整和最新的文档支持。

375 浏览量

2707 浏览量

123 浏览量

615 浏览量

454 浏览量

204 浏览量

225 浏览量

874 浏览量

hclo005

- 粉丝: 9

- 资源: 23

最新资源

- laravel-simple-order-system

- VulkanSharp:Vulkan API的开源.NET绑定

- 网络游戏-网络中的帧传送方法以及节点、帧传送程序.zip

- bc19-webapp

- bagging算法

- c语言课程设计-职工资源管理系统

- 类似WINDOWS进度复制文件夹例子-易语言

- CPSC471-Project

- uzkoogle

- CBEmotionView(iPhone源代码)

- crunchyroll-ext

- 2016年数学建模国赛优秀论文.zip

- 运输成本估算器:允许用户估算物品的运输成本

- Unrar调用模块 - RAR解压、测试、查看全功能版-易语言

- 鸿蒙轮播图banner.7z

- Mailican-crx插件