Cyclone V器件时钟网络与PLL详解:高级特性和资源概述

需积分: 0 131 浏览量

更新于2024-06-30

收藏 712KB PDF 举报

在Cyclone V器件的第1卷第4章中,着重讨论了时钟网络和锁相环(PLL)的高级特性。Cyclone V系列作为一款先进的FPGA(现场可编程门阵列)产品,其时钟系统设计复杂且高效,对于实现多任务并行处理至关重要。

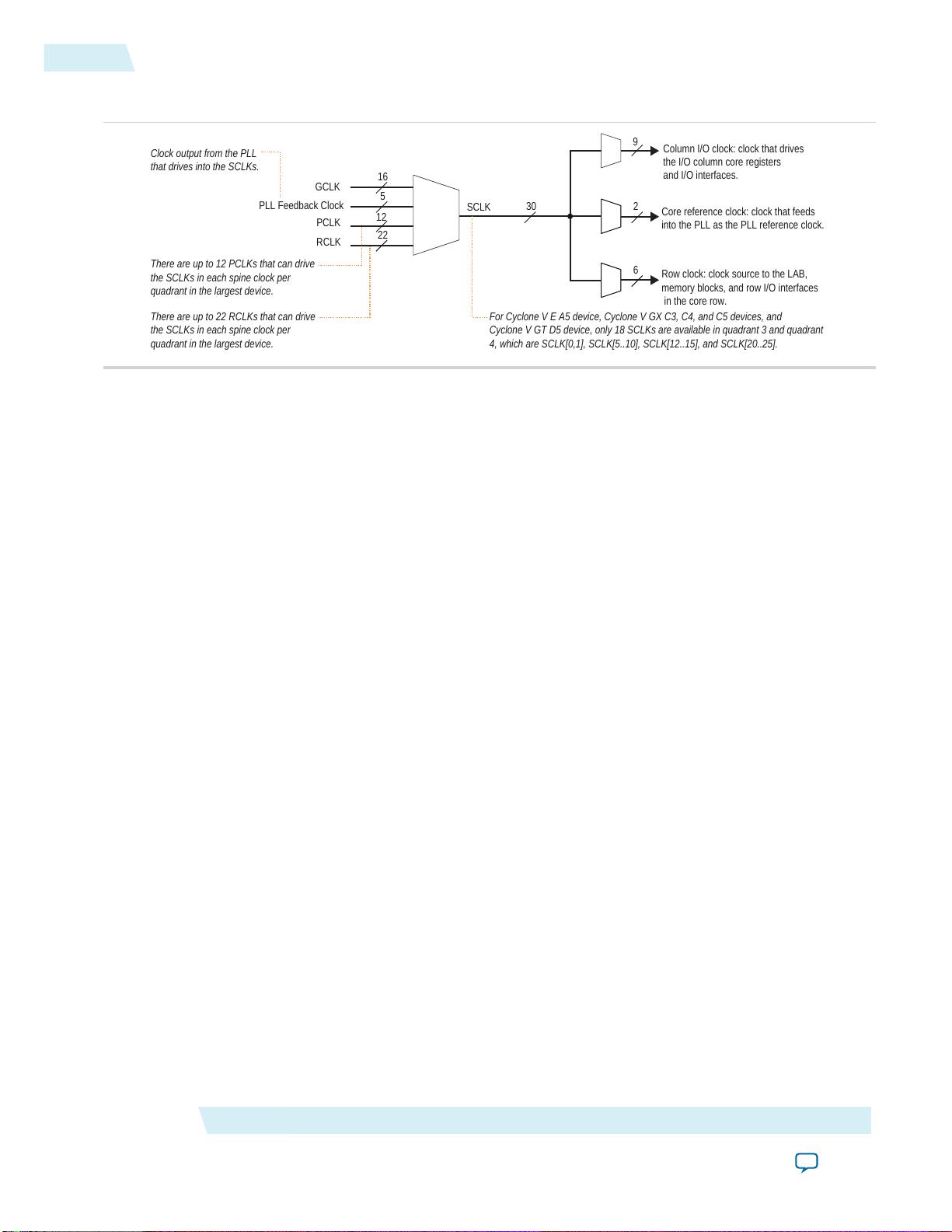

首先,Cyclone V的时钟网络被划分为三个层次:全局时钟(GCLK)、局域时钟(RCLK)以及外设时钟(PCLK)网络。这种多层次的结构确保了设备内部信号的精准同步和灵活配置。全局时钟网络负责提供核心时钟信号,用于连接整个芯片的不同部分;局域时钟网络则是局部区域内的时钟管理,可以减少信号传播延迟;外设时钟网络则针对特定外设提供定制化的时钟,提高系统性能和效率。

Cyclone V器件支持极为丰富的时钟资源,每个器件象限最多可以有50个独立的GCLK、RCLK和PCLK时钟源,总计可达到16个GCLKs、22个RCLKs和12个PCLKs(仅限于象限1和象限4)。这样的高密度时钟资源使得设计者能够在大规模并行处理应用中灵活地分配和调度时钟。

值得一提的是,Quartus II软件内置了PLL功能,无需额外的外部硬件即可启用和利用PLL的时钟倍频和分频能力,这大大简化了设计流程。此外,Cyclone V还遵循ISO 9001:2008质量管理体系标准,保证产品的制造和性能符合高质量要求。

然而,需要注意的是,尽管Cyclone V提供了强大的时钟网络功能,但设计过程中可能遇到某些已知问题,这些信息可以在Cyclone V器件手册的已知问题章节中找到。设计者在利用这些资源时,需要关注最新的文档更新,以确保设计的稳定性和兼容性。

Cyclone V的时钟网络和PLL特性是该器件设计的核心优势,它们通过高度灵活的架构和集成的PLL功能,支持复杂的系统级时钟管理,显著提升了FPGA在实时和高性能应用中的性能。在实际应用中,理解并有效利用这些时钟资源是提高设计效能的关键。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-04 上传

2022-08-04 上传

2022-08-04 上传

2022-08-04 上传

2022-08-04 上传

2022-08-04 上传

顾露

- 粉丝: 19

- 资源: 313

最新资源

- Accern-0.1.4.dev5-py2.py3-none-any.whl.zip

- FDFD_V1_viscoacousticwave_thirdyeq_频率域声波_FDFD_粘滞声波有限差分模拟.zip

- ce-site-v3:此回购适用于我的网站的第3版

- meteorjs-simple-todos:MeteorJS 框架的试用

- offshore-wind-farms-using-MAS,java源码项目,java发号器

- bbb-playback

- 单片机C语言实例249-直流电机调速.zip

- 基于Javaweb+ssm+vue的网上奶茶店系统.zip

- 二抽取代码MATLAB-img-stego:在C#中使用GUI进行盲图像隐写的示例应用程序

- FrontEcommerce-源码.rar

- 任贤齐演唱会双微方案.zip运营、文案策划资料打包下载

- QuirkbotCODE-Electron:基于Electron构建的QuirkbotCODE跨平台应用程序

- itunes:测试余烬是

- 基于MATLAB的卷积码的编译码与性能分析

- conference-2018-workshop:车间材料

- Python库 | eupy-1.0.1.zip