Volume 2: Chapter 4 of Cyclone V devices covers the configuration of transceiver protocols. The dedicated transceiver physical coding sublayer (PCS) and physical medium attachment sublayer (PMA) circuits in Cyclone V devices support various communication protocols.

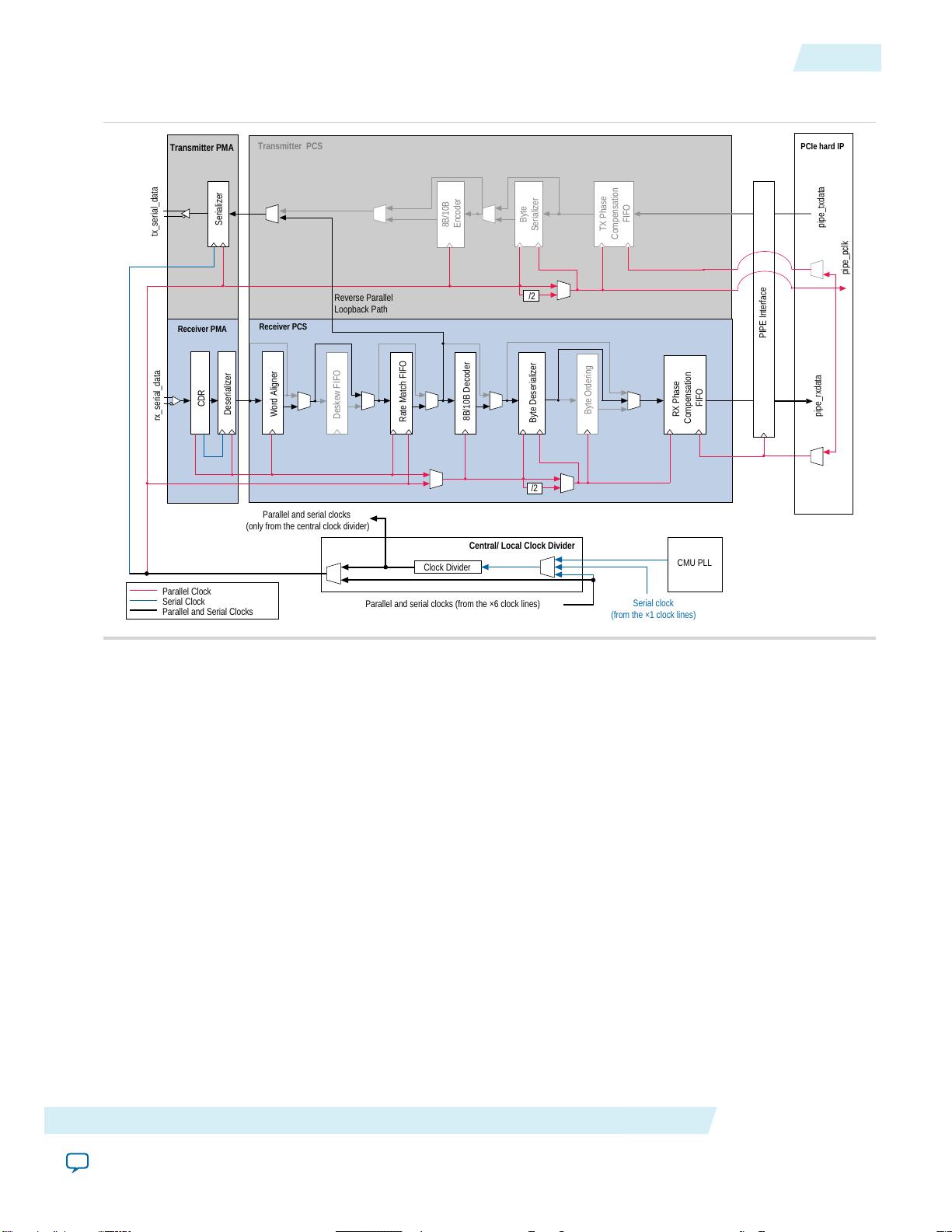

The table in this chapter outlines the PCS functionality of the Cyclone V device, including the receiver data path, transmitter data path, and the supported data rates in Gbps. The PCS supports various protocols such as PIPE connected to PCIe Hard IP, PCIe Gen1 and Gen2, custom single or dual width modes with rate matching FIFO, Gigabit Ethernet, Serial Digital Interface (SDI), SATA, SAS, and more. The PCS functionality also includes phase compensation FIFOs, byte deserializers, byte aligners, and 8B/10B decoders and encoders for various protocols.

The Cyclone V devices provide versatile support for a range of communication protocols, enabling a wide range of applications such as PCIe connectivity, high-speed data transmission, and storage interface support. The configurable and customizable nature of the PCS functionality allows for tailored implementations of the protocols based on specific application requirements.

Overall, the Chapter 4 of Volume 2 of Cyclone V devices provides detailed insight into the transceiver protocol configuration, highlighting the flexibility and support for various communication standards, making Cyclone V devices suitable for diverse and demanding applications in the field of communication and data transmission.