CDM模型:半导体器件静电敏感度与ESD测试解析

需积分: 5 141 浏览量

更新于2024-08-04

2

收藏 737KB PDF 举报

"本文主要介绍了半导体器件的静电放电(ESD)测试中的带电器件模型(CDM),以及静电敏感度分级的相关知识。CDM模型不同于人体模型(HBM)和机器模型(MM),它是模拟器件自身带电后对地放电的情况,常见于微电子器件的制造、封装、测试等环节。随着自动化水平提升,CDM模型的ESD事件成为导致器件失效的主要因素之一。文章详细阐述了CDM模型的工作原理,包括器件摩擦带电、放电过程和影响因素,如封装类型和引脚布局。此外,还对比了CDM与其他模型(HBM、MM)的放电波形和电流特性,强调了CDM放电的快速性和高强度,这使得一般的保护电路难以及时响应。"

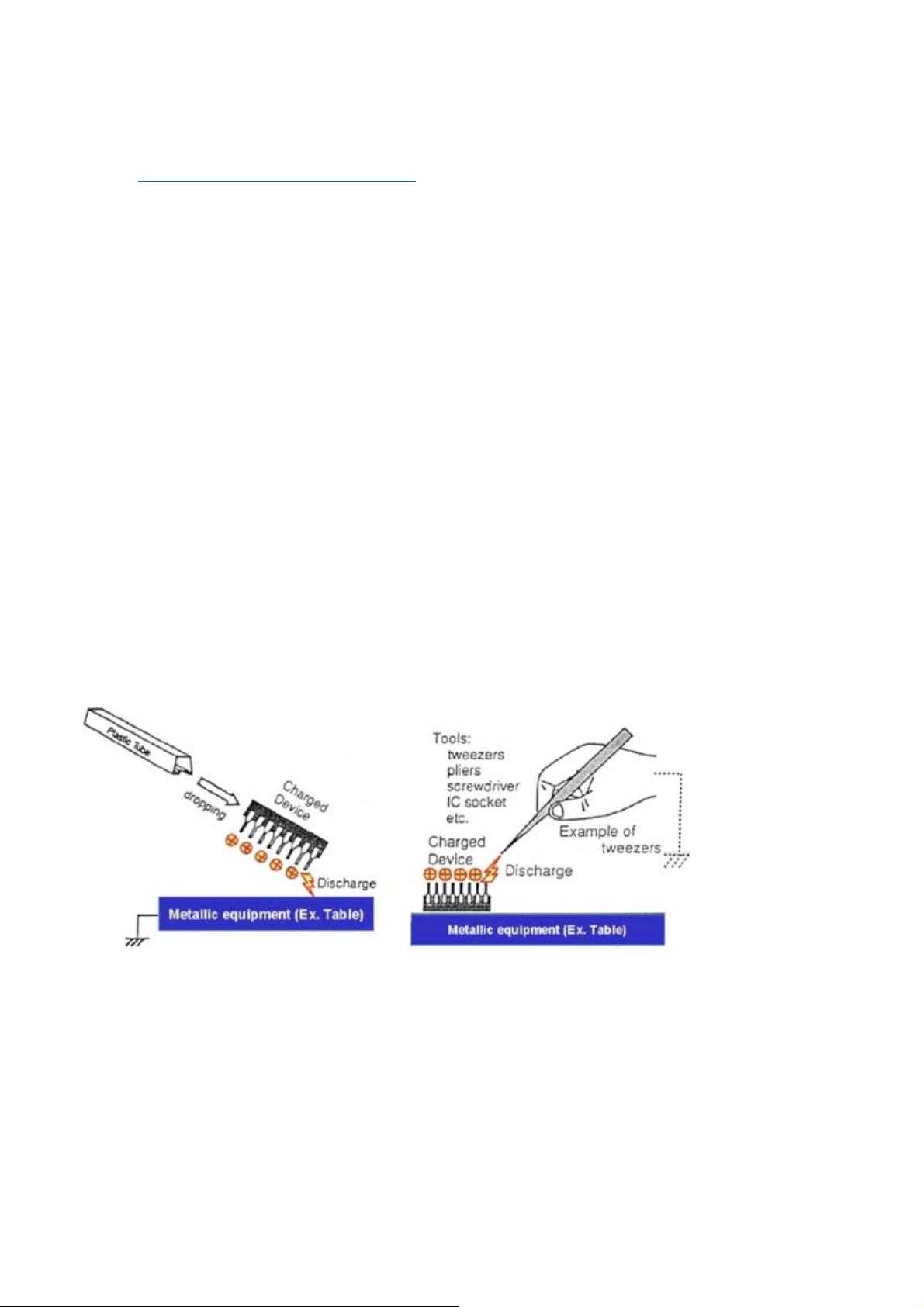

半导体器件的ESD测试是确保产品可靠性的重要环节,其中CDM模型因其独特性备受关注。带电器件模型(CDM)假设器件在生产过程中因摩擦等原因积累了电荷,当器件的引脚与接地物体接触时,会发生快速放电,这种放电现象可能导致器件内部结构的损伤。与HBM(人体模型)和MM(机器模型)不同,CDM不涉及外部电荷来源,而是关注器件自身的带电状态。

CDM模型的放电速度非常快,通常在几纳秒内完成,这使得它产生的峰值电流极大,可达5至20安培,并且放电时间极短,一般保护电路往往来不及启动。由于这些特性,CDM模型对器件的静电敏感度要求更高。封装形式对器件的CDM敏感度有很大影响,例如,小型封装的IC往往比双列直排封装的IC更容易受到CDM损害,而薄型小型封装或引脚阵列封装的IC则通常具有更低的CDM耐压能力。

为了评估和分类半导体器件的静电敏感度,行业通常会根据器件在CDM模型下的耐受阈值进行分级。这些分级标准有助于指导生产和储存条件,以减少ESD事件对器件的影响。例如,根据IEC61000-4-2标准,器件可能会被分为多个等级,每个等级对应不同的放电电压容忍度。

CDM测试对于理解并预防微电子器件在生产、处理和使用过程中可能出现的静电损伤至关重要。设计者和制造商需要充分理解CDM模型,优化封装和工艺,以提高器件的ESD防护性能,从而降低产品失效的风险。

323 浏览量

323 浏览量

128 浏览量

2023-02-20 上传

2023-02-20 上传

170 浏览量

2984 浏览量

耀程工

- 粉丝: 7

最新资源

- WebDrive v16.00.4368: 简易易用的Windows风格FTP工具

- FirexKit:Python的FireX库组件

- Labview登录界面设计与主界面跳转实现指南

- ASP.NET JS引用管理器:解决重复问题

- HTML5 canvas绘图技术源代码下载

- 昆仑通态嵌入版ASD操舵仪软件应用解析

- JavaScript实现最小公倍数和最大公约数算法

- C++中实现XML操作类的方法与应用

- 设计编程工具集:材料重量快速计算指南

- Fancybox:Jquery图片轮播幻灯弹窗插件推荐

- Splunk Fitbit:全方位分析您的活动与睡眠数据

- Emoji表情编码资源及数据库查询实现

- JavaScript实现图片编辑:截取、旋转、缩放功能详解

- QNMS系统架构与应用实践

- 微软高薪面试题解析:通向世界500强的挑战

- 绿色全屏大气园林设计企业整站源码与多技术项目资源