使用TimingDesigner优化FPGA设计中的时序管理

184 浏览量

更新于2024-08-28

收藏 383KB PDF 举报

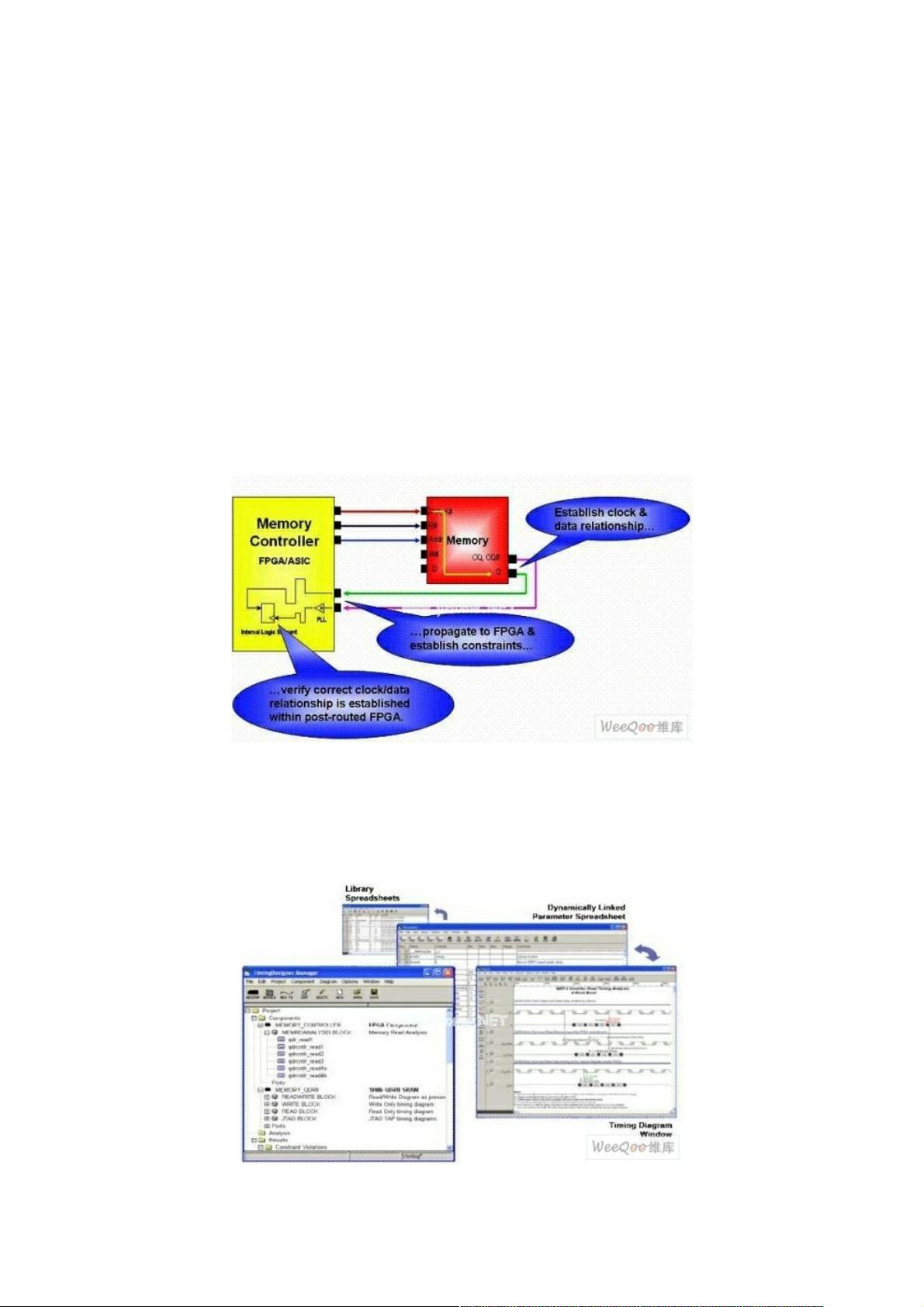

"着在设计FPGA与DDR或QDR存储器接口时,必须精确地管理时序以保证数据正确传输。DDR内存的读写操作依赖于时钟的上升沿和下降沿,因此,时序约束的设置至关重要。DDR接口设计中的关键时序参数包括时钟到数据的延迟(CDQ),数据到时钟的延迟(DQD),以及数据眼图的对齐,这些都需要通过精密的时序分析工具来调整。

TimingDesigner提供了强大的时序分析和约束管理功能,能够帮助设计者定义和验证这些关键参数。例如,它可以帮助确定适当的时钟偏移,使得数据在正确的时钟边缘被采样。此外,软件还允许用户模拟和优化时序路径,以应对不同工作条件下的变化,如温度和电源电压波动。

四、时序分析与优化

时序分析涉及到对整个设计中所有逻辑路径的延迟进行计算,包括组合逻辑延迟和时钟树延迟。在DDR接口设计中,必须确保数据在正确的时间到达接收端,同时考虑到信号完整性的影响,如反射、串扰和抖动。TimingDesigner能够仿真这些影响,提供详细的时序报告,帮助设计师识别可能的时序违反,并提供修复建议。

五、交互式时序图

TimingDesigner的交互式时序图功能使得设计团队能够直观地理解设计中的时序关系,这对于团队协作尤其重要。通过这些图形,设计者可以清晰地看到每个信号相对于时钟的相对位置,以及它们在实际操作中的行为,这有助于识别潜在的时序冲突并进行有效的优化。

六、物理设计考虑

物理设计层面,如布线的长度匹配、信号线的阻抗匹配以及封装引脚的布局,都会对时序产生显著影响。TimingDesigner的工具集可以集成到物理实现流程中,提供反馈,帮助优化布线策略以满足严格的时序约束。

七、总结

在高速FPGA设计中,有效地管理时序问题至关重要,因为任何微小的失误都可能导致整个系统的性能下降或失败。通过使用像TimingDesigner这样的高级工具,设计者可以早期发现并解决时序问题,从而提高设计效率,保证设计质量,并满足高带宽和低延迟的需求。这种工具的使用是现代FPGA设计不可或缺的一部分,它能够帮助设计团队克服复杂的时序挑战,成功实现高性能的系统设计。"

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-08 上传

2009-09-25 上传

2012-09-01 上传

2008-03-07 上传

2020-08-29 上传

2011-04-26 上传

weixin_38665629

- 粉丝: 4

- 资源: 958

最新资源

- GNU make中文手册

- 单片机声控智能小车,单片机控制电路主要由一片89C2051和一片89C52组成。89C2051主要实现对路面黑线的软件检测与纠错;89C52 则作为整个控制部分的核心,负责车速检测、电动机驱动、数据显示等功能。

- 数字集成电路的分类、特点、使用方法

- 电磁干扰与电磁兼容浅谈

- C#面向对象设计模式纵横谈

- 考研专用的计算机组成原理课件

- DWR中文文档!!!!

- PCI设备初始化编程的过程

- Freescale Codewarrior5.0快速入门

- 解释器模式基础,初学者好用的

- Eclipse – 整合开发工具(基础篇

- Verilog的基础知识

- c#窗体重构 窗体重构教程

- 软件设计考试复习题,考试必考

- C常用编程范例参考学习资料

- Elements of Information Theory.pdf