Altera时序分析与同源系统DDR时序约束实战指南

"Altera时序分析模型及同源系统的时序约束"

本文主要探讨了在FPGA设计中,特别是使用Altera FPGA时,如何理解和应用时序约束,特别是在高速接口设计中的关键点。作者强调了深入理解时序分析模型和同源系统时序约束的重要性,以解决实际工程中可能出现的问题。

2.1. FPGA输入时序等效模型

在FPGA输入时序分析中,通常使用一个等效模型来简化理解。这个模型包括上游设备的数据和时钟通过一个D触发器REG1,经过PCB布线的延迟到达FPGA的输入引脚。FPGA内部将这个输入等效为另一个D触发器REG2。其中,关键参数包括Tsu、Th和Tco,它们分别代表数据稳定在有效状态前的最小保持时间、数据稳定在有效状态后的最小建立时间,以及数据从输入引脚到达内部寄存器的时间。

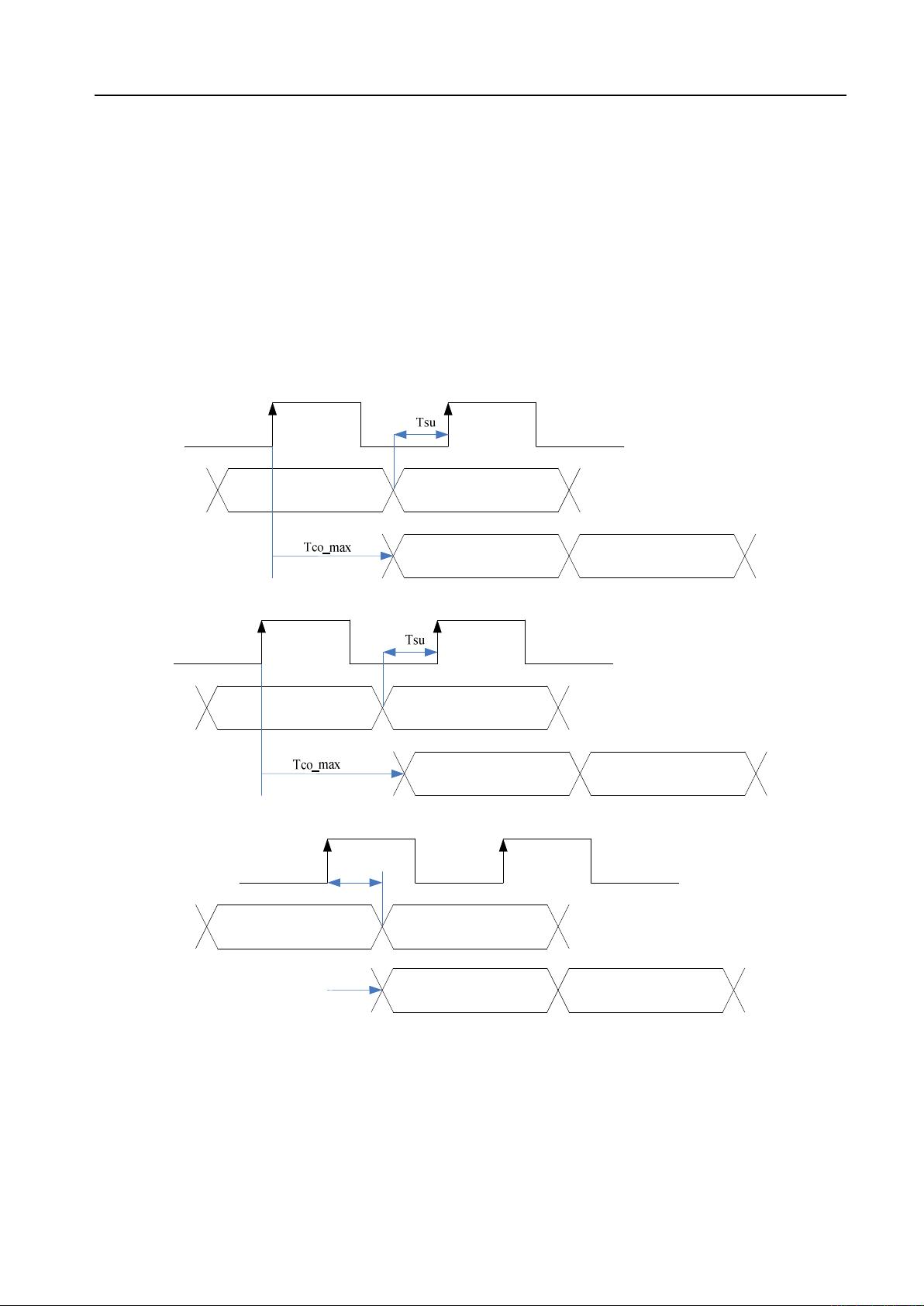

2.2. Tsu、Th和Tco的基本概念及关系

Tsu是保证数据在时钟边沿到来之前保持稳定至少的时间,以确保正确捕获。Th则是数据必须在时钟边沿之后保持稳定的时间,防止在内部逻辑处理中发生变化。Tco表示数据从外部输入到FPGA内部寄存器所需的时间,用于确定外部输入数据应何时到达FPGA引脚。

2.3. Input_delay和时序分析

Input_delay是FPGA输入端口的延迟,包括输入缓冲器和布线延迟。正确设置Input_delay对于满足时序约束至关重要,因为它直接影响到Tsu和Th的计算。

3.1. FPGA输出时序等效模型

输出时序等效模型考虑了FPGA内部寄存器到输出缓冲器,再到下游设备的数据路径。输出时序约束涉及到Output_delay,这是数据从FPGA内部寄存器到外部线路的延迟。

3.2. Output_delay和时序约束

Output_delay的设定决定了FPGA如何驱动下游设备,以确保数据在正确的时序窗口内到达。这涉及到输出数据的建立和保持时间,与输入时序约束相呼应。

4. 同源系统的DDR模式的输入输出时序约束

在DDR模式下,数据在时钟的上升沿和下降沿都被采样,因此时序约束更为复杂。FPGA的输出时钟必须精确控制,以保证与输入时钟的同步。此外,输出数据的时序约束需要考虑到数据的边缘对齐,以及可能存在的异常设计(exception design)。

4.1.1. FPGA输出时钟的设计

输出时钟的设计需要考虑到DDR模式的特性,确保时钟的上升沿和下降沿都能正确驱动数据。

4.1.2. FPGA输出时钟约束

时钟约束涉及到时钟路径的延迟,以确保时钟到达每个DDR数据路径的时刻都准确无误。

4.1.3. FPGA输出数据时序约束

输出数据的时序约束需保证在时钟边沿处数据稳定,同时考虑到数据的预置和清除时间。

4.1.4. FPGA输出时序约束——exception设计

在某些情况下,可能需要特殊的时序约束来处理异常情况,例如数据转换或特殊信号处理。

4.2.1. FPGA输入时钟生成

输入时钟通常需要通过PLL或DLL来产生,确保其与FPGA内部时钟同步,并满足DDR模式的要求。

4.2.2. FPGA输入数据时序约束

输入数据的时序约束涉及到数据与时钟的关系,确保在正确的时钟边沿捕获数据。

4.2.3. FPGA输入时序约束exception设计

在处理特定输入信号时,可能需要特殊的时序约束来处理非标准的情况。

5. FPGA输入输出约束实例

文章提供了一些实际的输入输出约束设置例子,帮助读者更好地理解和应用这些理论知识。

总结,理解Altera的时序分析模型和同源系统的时序约束对于高效、可靠的FPGA设计至关重要。通过深入学习这些概念和实践经验,工程师能够更好地解决高速接口设计中的时序问题,确保设计的性能和稳定性。

147 浏览量

2023-05-27 上传

2023-04-27 上传

2023-08-18 上传

2023-07-13 上传

2023-10-03 上传

2023-09-07 上传

2024-10-07 上传

kcul

- 粉丝: 11

- 资源: 10

最新资源

- 天池大数据比赛:伪造人脸图像检测技术

- ADS1118数据手册中英文版合集

- Laravel 4/5包增强Eloquent模型本地化功能

- UCOSII 2.91版成功移植至STM8L平台

- 蓝色细线风格的PPT鱼骨图设计

- 基于Python的抖音舆情数据可视化分析系统

- C语言双人版游戏设计:别踩白块儿

- 创新色彩搭配的PPT鱼骨图设计展示

- SPICE公共代码库:综合资源管理

- 大气蓝灰配色PPT鱼骨图设计技巧

- 绿色风格四原因分析PPT鱼骨图设计

- 恺撒密码:古老而经典的替换加密技术解析

- C语言超市管理系统课程设计详细解析

- 深入分析:黑色因素的PPT鱼骨图应用

- 创新彩色圆点PPT鱼骨图制作与分析

- C语言课程设计:吃逗游戏源码分享