other

peripheral devices; thus, the same register can be used

for

both

input

and

output

functions.

2.2.2

Master-Slave Relation

Communication between

two

devices on

the

bus is in

the

form

of

a

master-slave relationship. At any point in time, there is one device

that

has control

of

the

bus. This controlling device is termed

the

"bus

mas·

ter".

The master device controls the bus when communicating

with

another device on

the

bus, termed

the

"slave".

A typical example

of

this

relationship is

the

processor, as master, fetching an instruction

from

memory

(which is always a slave). Another example is

the

disk, as

master,

transferring

data

to

memory, as slave. Master-slave relation·

ships are dynamic. The processor,

for

example, may pass bus control

to

a disk. The disk,

as

master, could then communicate

with

a slave

memory bank.

Since the UNIBUS is used by

the

processor and all 1/0 devices, there is

a

priority

structure

to

determine which device gets control

of

the

bus.

Every device on the

UNIBUS which is capable

of

becoming bus master

is

assigned a priority. When two devices, which are capable

of

becoming

a bus master, request use

of

the

bus simultaneously,

the

device with

the

higher

priority

will receive control.

2.2.3

Interlocked Communication

Communication on the

UNIBUS is interlocked so

that

for

each control

signal

issued by

the

master device, there

must

be

a response

from

the

slave in order

to

complete

the

transfer. Therefore, communication is

independent

of

the

physical bus length (as

far

as

timing

is concerned)

and the response

time

of

the master and slave devices. This asynchron·

ous operation

precludes

the

need

for

synchronizing with, and waiting

for,

clock pulses. Thus, each device is allowed

to

operate at its

maximum

possible speed.

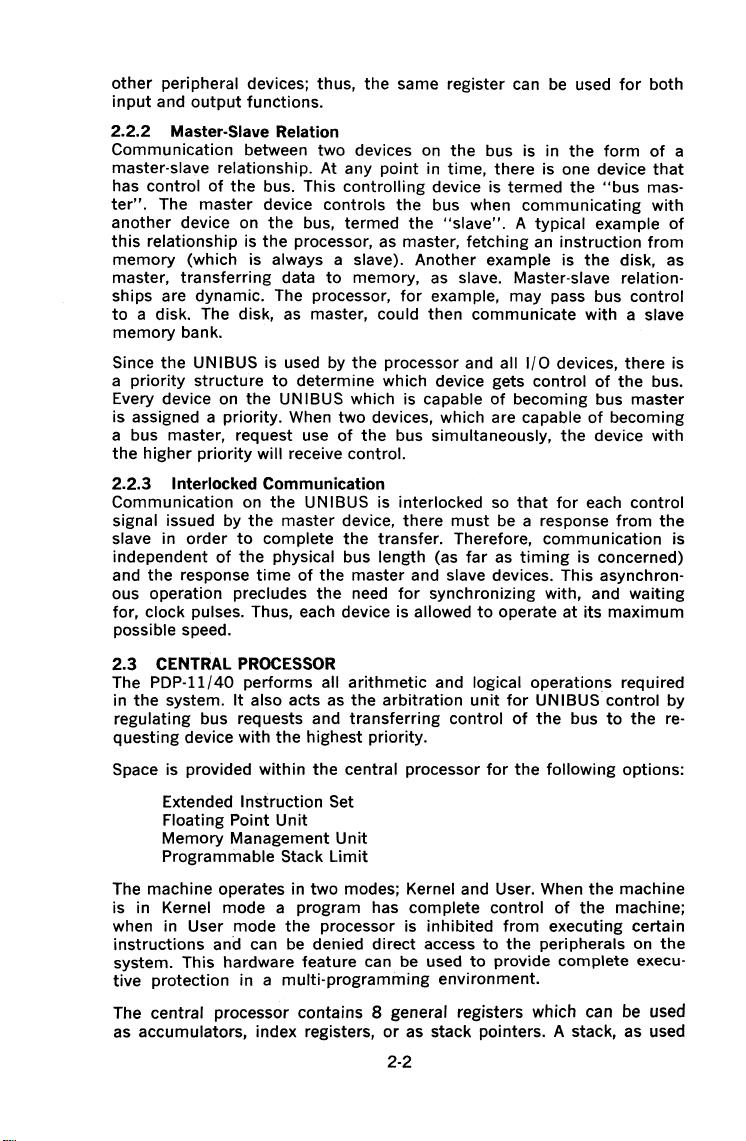

2.3

CENTRAL

PROCESSOR

The

PDP·ll/40

performs all

arithmetic

and logical operations required

in

the

system.

It

also acts as

the

arbitration

unit

for

UNIBUS control by

regulating bus requests and transferring control

of

the

bus

to

the

re·

questing device with

the

highest priority.

Space is provided

within

the

central processor

for

the

following options:

Extended

Instruction Set

Floating

Point

Unit

Memory Management

Unit

Programmable Stack

Limit

The machine operates in

two

modes; Kernel and User. When

the

machine

is in

Kernel mode a program has complete control

of

the machine;

when in User mode

the

processor is inhibited

from

executing certain

instructions

and can

be

denied direct access

to

the peripherals on

the

system. This hardware feature can be used

to

provide complete execu·

tive protection in a multi-programming environment.

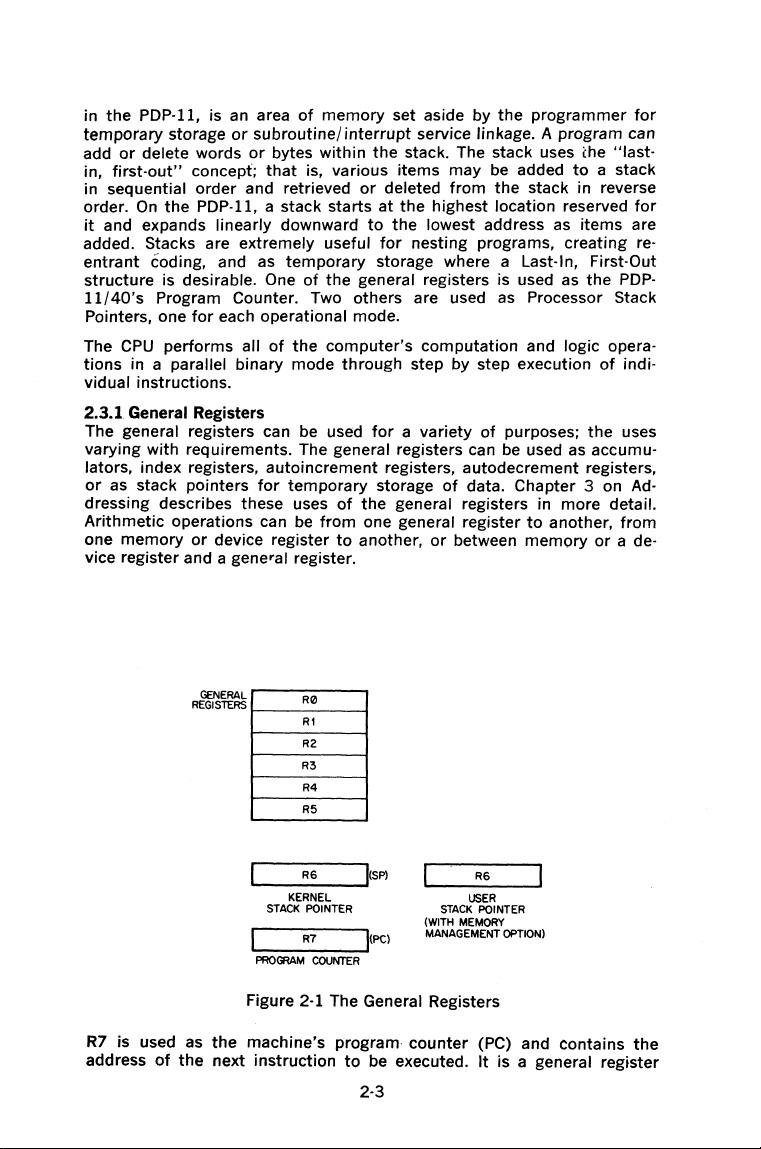

The

central processor contains 8 general registers which can be used

as

accumulators, index registers,

or

as stack pointers. A stack, as used

2·2