DSP中断与ADC配置在南京理工大学作业中的应用

版权申诉

"这篇文档是南京理工大学李彧晟老师教授的DSP应用技术课程的作业,主要涉及了数字信号处理器(DSP)的中断系统配置和ADC(模数转换器)及EPWM(增强型脉宽调制)参数初始化的相关程序代码。作业要求学生分析并摘录与中断设置相关的程序语句,以便理解中断处理机制在DSP系统中的实现。"

在数字信号处理器(DSP)的应用中,中断系统是一个关键部分,它使得处理器能够及时响应外部事件。文档中提到的中断设置主要分布在以下几个方面:

1. **全局中断的开启和关闭**:

- `DINT` 语句用于禁止CPU中断和全局中断,确保在配置中断系统时不会受到外部中断的干扰。

- `EINT` 语句则用于开启全局中断,允许系统再次响应中断请求。

2. **初始化中断控制器**:

- `InitPieCtrl()` 函数初始化PIE(Programmable Interrupt Engine,可编程中断引擎)控制寄存器,这是TI公司的TMS320F2833x DSP系列中断管理的核心。

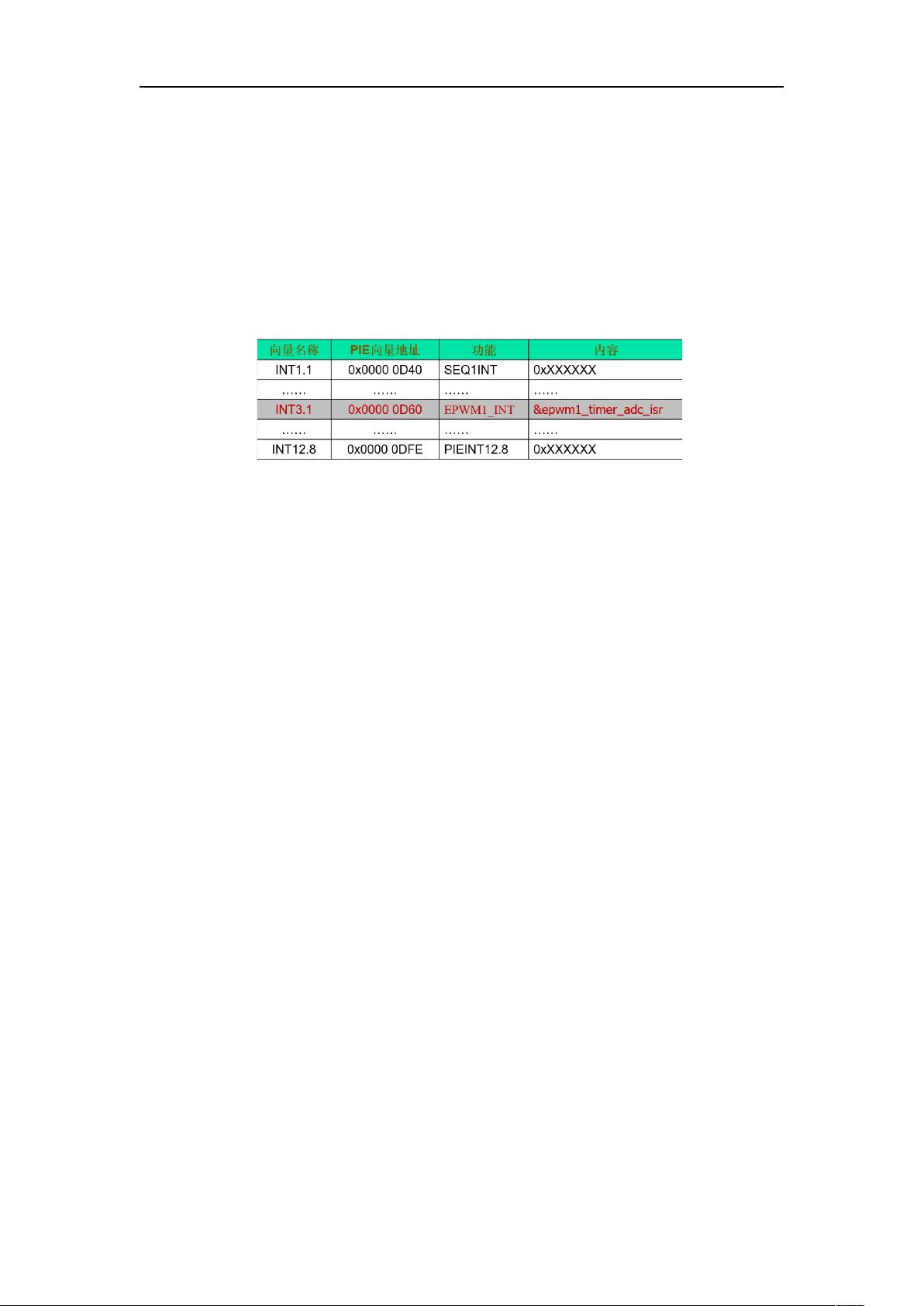

- `InitPieVectTable()` 初始化PIE向量表,设置中断服务例程的地址,其中`PieCtrlRegs.PIECTRL.bit.ENPIE=1` 开启PIE中断功能。

3. **中断源的配置**:

- `PieCtrlRegs.PIEIER3.bit.INTx1=1` 使能了第三组的第一个中断,即EPWM1_INT中断。

- `IER|=M_INT3` 打开了CPU的第三组中断,允许CPU响应来自PIE的中断请求。

4. **ADC(模数转换器)参数设置**:

- `InitAdcParameters()` 函数中,`AdcRegs.ADCST.bit.INT_SEQ1_CLR=1` 清除SEQ1中断标志位,避免不必要的中断触发。

- `AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1=0` 禁用了INT-SEQ1对CPU的中断请求,意味着在SEQ1序列结束时不触发中断。

- `AdcRegs.ADCTRL2.bit.INT_MOD_SEQ1=0` 设置为每个SEQ1序列结束后不置位INT-SEQ1,防止连续中断。

5. **EPWM(增强型脉宽调制)参数设置**:

- `InitEPwm1Parameters()` 函数内,`EPwm1Regs.ETSEL.bit.INTEN=1` 使能了ePWMx_INT中断,当特定事件发生时,能够触发中断。

- `EPwm1Regs.ETPS.bit.INTPRD=ET_3RD` 设置在第三个事件周期产生中断,这可能指的是PWM周期的某个特定时刻。

6. **中断服务例程**:

- `interrupt void epwm1_timer_adc_isr(void)` 是EPWM1定时器ADC中断服务例程,这里并未给出具体代码,但通常会包含处理中断事件的逻辑,例如读取ADC转换结果、更新PWM输出等。

通过这些设置,学生可以了解如何在实际应用中配置和使用DSP的中断系统,以及如何与ADC和EPWM模块协同工作。中断系统的有效配置和管理对于实时性和高效性至关重要,尤其是在需要快速响应外部事件的系统中。

2021-09-14 上传

2022-11-16 上传

2021-06-25 上传

2023-06-10 上传

2023-02-24 上传

2024-01-07 上传

2023-05-30 上传

2023-05-31 上传

2023-05-31 上传

在路上-正出发

- 粉丝: 2w+

- 资源: 125

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章