Verilog_HDL详解:硬件描述语言入门及应用

需积分: 13 101 浏览量

更新于2024-07-21

收藏 1.43MB PPT 举报

"硬件描述语言Verilog_HDL是用于电子设计自动化领域的编程语言,它允许工程师用代码来描述数字系统的硬件行为和结构。本资源主要介绍了Verilog的基础知识,包括语句、实例以及其在电路设计中的应用。"

在硬件描述语言Verilog_HDL中,设计者可以更高效地进行逻辑设计,降低设计成本,缩短设计周期,并通过仿真在设计阶段发现并修复错误。Verilog_HDL基于C语言的语法,易于学习和使用,支持多层次的抽象,广泛应用于集成电路设计。

Verilog_HDL的发展历程始于20世纪80年代,经过多次版本更新,如1995年的IEEE1364-1995标准和2001年的IEEE1364-2001,已成为业界两大主要的硬件描述语言之一,另一个是VHDL。

入门Verilog_HDL时,首先要了解的是模块和端口。模块是设计的基本单元,它描述了设计的功能和结构,而端口则是模块与其他模块通信的接口。例如,定义一个半加器模块,可以用代码定义输入和输出端口,以及内部的逻辑运算。

在门级描述中,Verilog_HDL提供了内置门原语,如AND、OR、NOT等,可以直接描述电路的门级结构。此外,还可以使用开关级原语,如NMOS、PMOS等,模拟晶体管级别的设计,以实现更精细的电路建模。

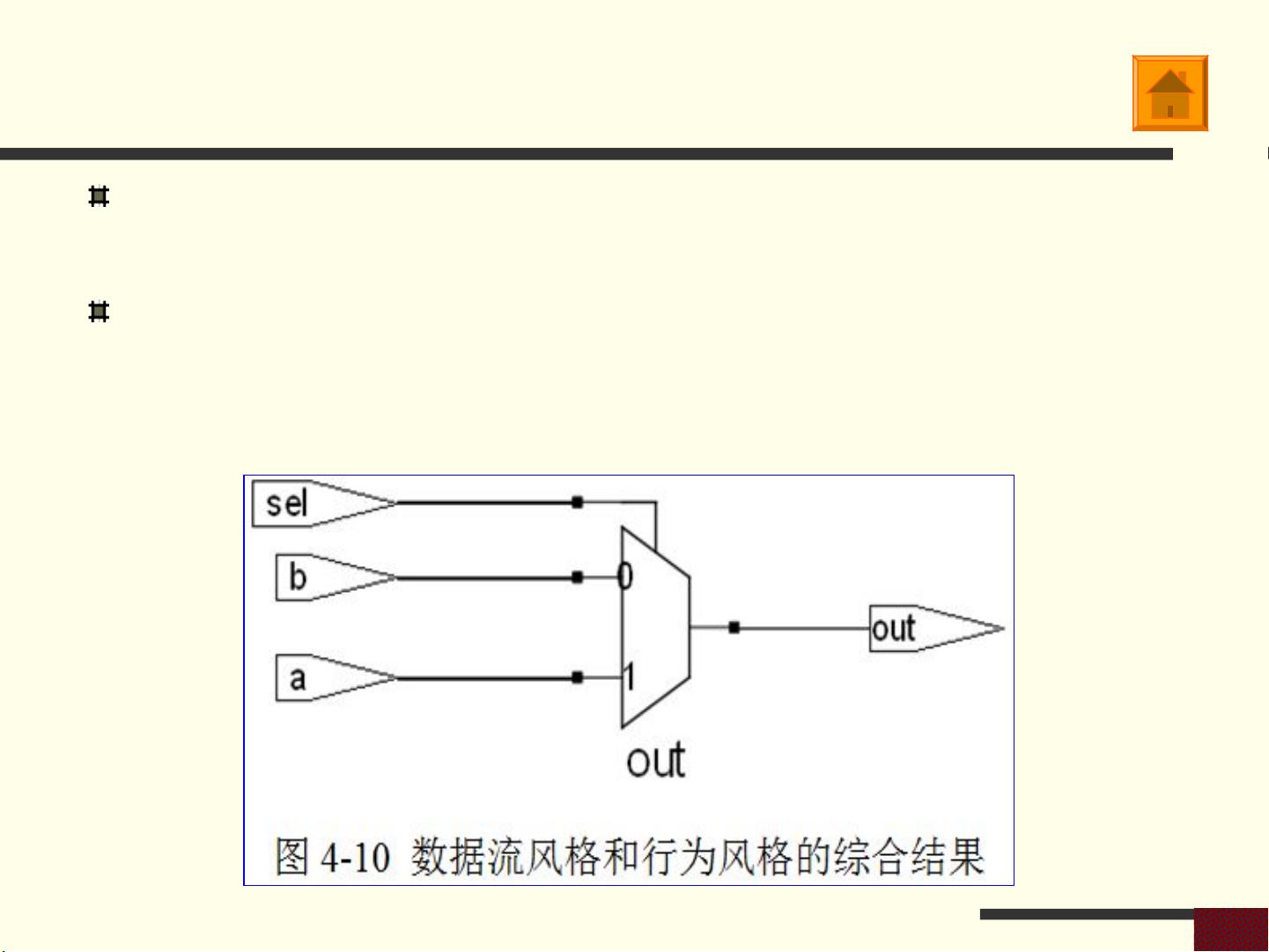

Verilog_HDL支持多种建模风格,包括数据流建模、行为级建模和门级建模。数据流建模侧重于数据在系统中的流动,行为级建模关注系统的功能行为,而门级建模则直接对应实际的逻辑门电路。通过这些不同的建模方式,设计者可以根据需要选择合适的抽象层次来描述系统。

语句的综合是Verilog_HDL中的关键步骤,它将高级的硬件描述转化为可实现的电路逻辑。这一过程通常由综合工具自动完成,将Verilog代码转换成等效的FPGA或ASIC布局布线输入。

Verilog_HDL是一种强大的设计工具,它涵盖了从概念验证到物理实现的整个设计流程。学习和掌握Verilog_HDL,对于从事集成电路设计、嵌入式系统开发和 FPGA 编程的专业人士至关重要。通过深入理解和实践,设计者能够利用Verilog_HDL高效地创建复杂的数字系统。

275 浏览量

108 浏览量

168 浏览量

105 浏览量

186 浏览量

2022-09-22 上传

popezha

- 粉丝: 0

- 资源: 1

最新资源

- 高志东

- MP4 Player3.10.2.zip

- STM32F4系列标准库 V1.9版(最新版)

- BrownG_HodgesK_RokuClient

- AndroidKiller.zip已调试好编译模块

- leetcode耗时-codeReview:使用帕森问题练习代码的地方

- 课程设计 新生报到查询系统

- 大专自我鉴定总结

- Data-karyawan

- s-ance:C#POO

- BinaryCalculator:一个对二进制字符串进行运算的简单计算器 - MEN WMI @ AMU 项目

- 学士学位DIM-Symfony-And-PHP

- 可重复使用的计算机视觉工具:supervision

- PHPStripper-开源

- Hazinash

- 大数据应用领域盘点共3页.pdf.zip