Verilog实现60进制计数器与时序逻辑分频

需积分: 13 105 浏览量

更新于2024-09-02

收藏 590KB DOC 举报

"本次实验主要涉及硬件与可编程语言中的时序逻辑电路,重点是理解和应用集成计数器以及二分频电路的原理。实验中,学生需要使用QuartusⅡ软件进行Verilog语言编程,实现60进制计数器的功能,并进行仿真和硬件测试。此外,还要求设计分频器和扫描电路,以便于在LED和七段数码管上显示计数值。"

实验内容详细解析:

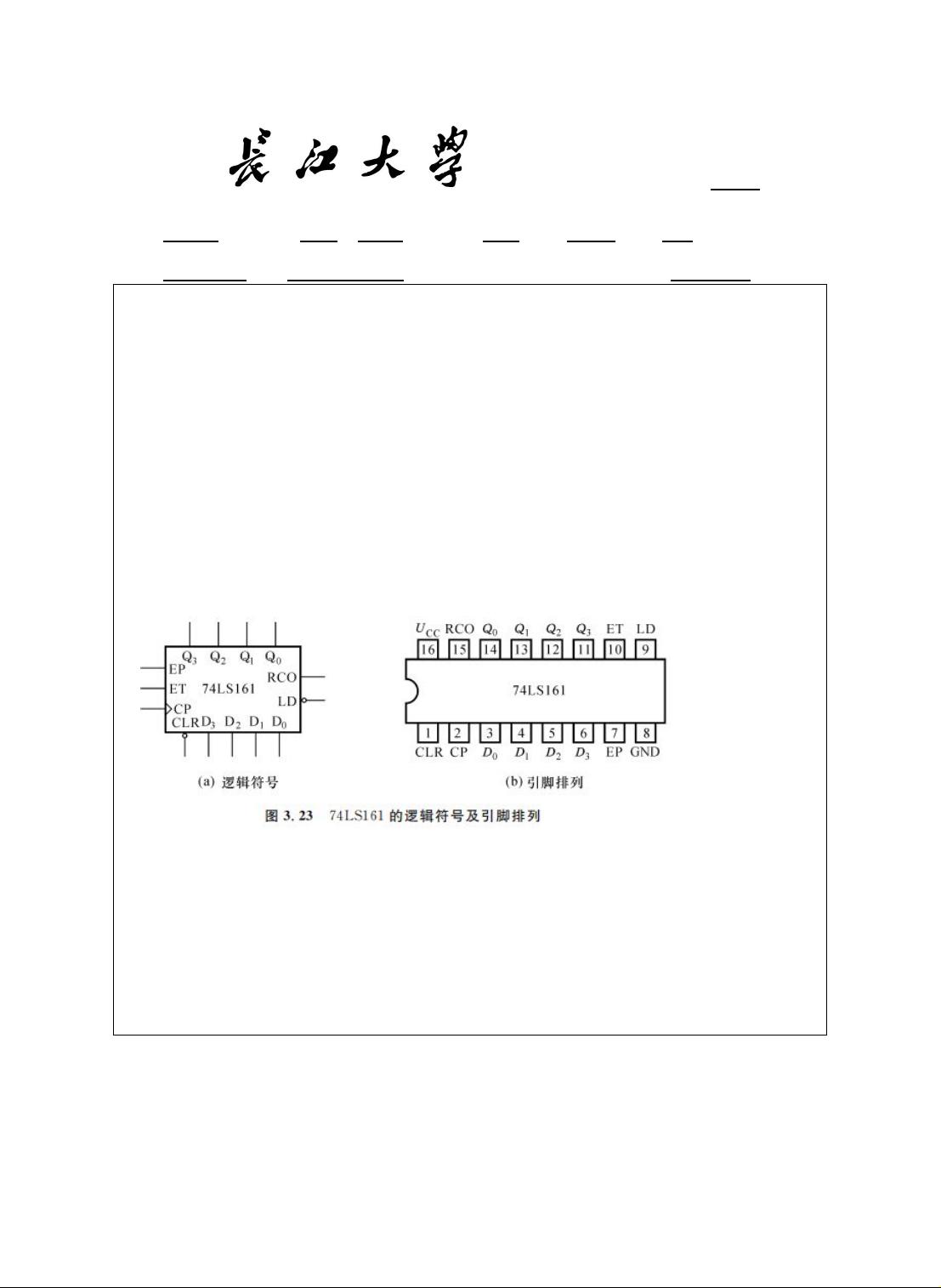

1. **74LS161集成计数器**:74LS161是一款4位二进制加法计数器,适用于构建各种计数逻辑。其逻辑功能和引脚布局是实验的基础,通过这个器件,学生可以学习到如何构建和控制数字计数系统。

2. **二分频电路**:二分频是将输入时钟频率减半的过程,常用于时序逻辑电路中。通过74LS76或74LS74触发器,当J=K=1时,JK触发器会翻转其输出状态,实现二分频。对于D触发器,通过连接D输入到触发器的反向输出,同样可以达到二分频的效果。

3. **Verilog编程**:实验要求使用Verilog语言编程实现60进制计数器。Verilog是一种硬件描述语言,用于描述数字系统的结构和行为,包括计数器、分频器等时序逻辑电路。

4. **分频**:设计一个分频器,将50MHz的系统时钟分频为1Hz,这对于许多数字系统来说是必要的,因为它们通常需要低频信号来驱动显示或其他控制功能。

5. **扫描显示**:如果使用8个LED和2个七段数码管显示60进制计数器的结果,需要一个扫描显示机制。这涉及到在足够快的速率下切换显示,以使人类观察者看到连续的数字而不是闪烁。

6. **系统功能模块的级联**:实验中展示了如何通过级联不同功能模块(计数器、分频器和扫描模块)来构建完整的60进制计数器系统,这体现了硬件描述语言和FPGA设计中的模块化思想。

实验总结:

1. **时序逻辑电路特点**:时序逻辑电路的输出不仅取决于当前输入,还依赖于电路的先前状态,因此具有记忆功能。

2. **计数器的应用**:计数器不仅是数字计数的基础,还可用于分频和定时,同步计数器和异步计数器是两种常见的类型。

通过这个实验,学生不仅加深了对时序逻辑电路的理解,还掌握了Verilog编程、QuartusⅡ软件的使用,以及数字系统设计的基本技巧。这些技能对于未来在硬件设计和嵌入式系统开发领域的工作至关重要。

2011-04-21 上传

2018-08-26 上传

2020-11-06 上传

2022-11-14 上传

2010-10-13 上传

2021-09-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

rabber12

- 粉丝: 0

- 资源: 1

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全