时序逻辑电路解析与设计

需积分: 35 65 浏览量

更新于2024-07-18

2

收藏 2.07MB PDF 举报

"时序逻辑电路是数字电路的基础部分,主要讨论了时序逻辑电路的特点、分析方法、常用电路、设计方法以及如何用可编程逻辑器件实现同步时序逻辑电路,同时还涵盖了时序逻辑电路中的竞争-冒险现象。"

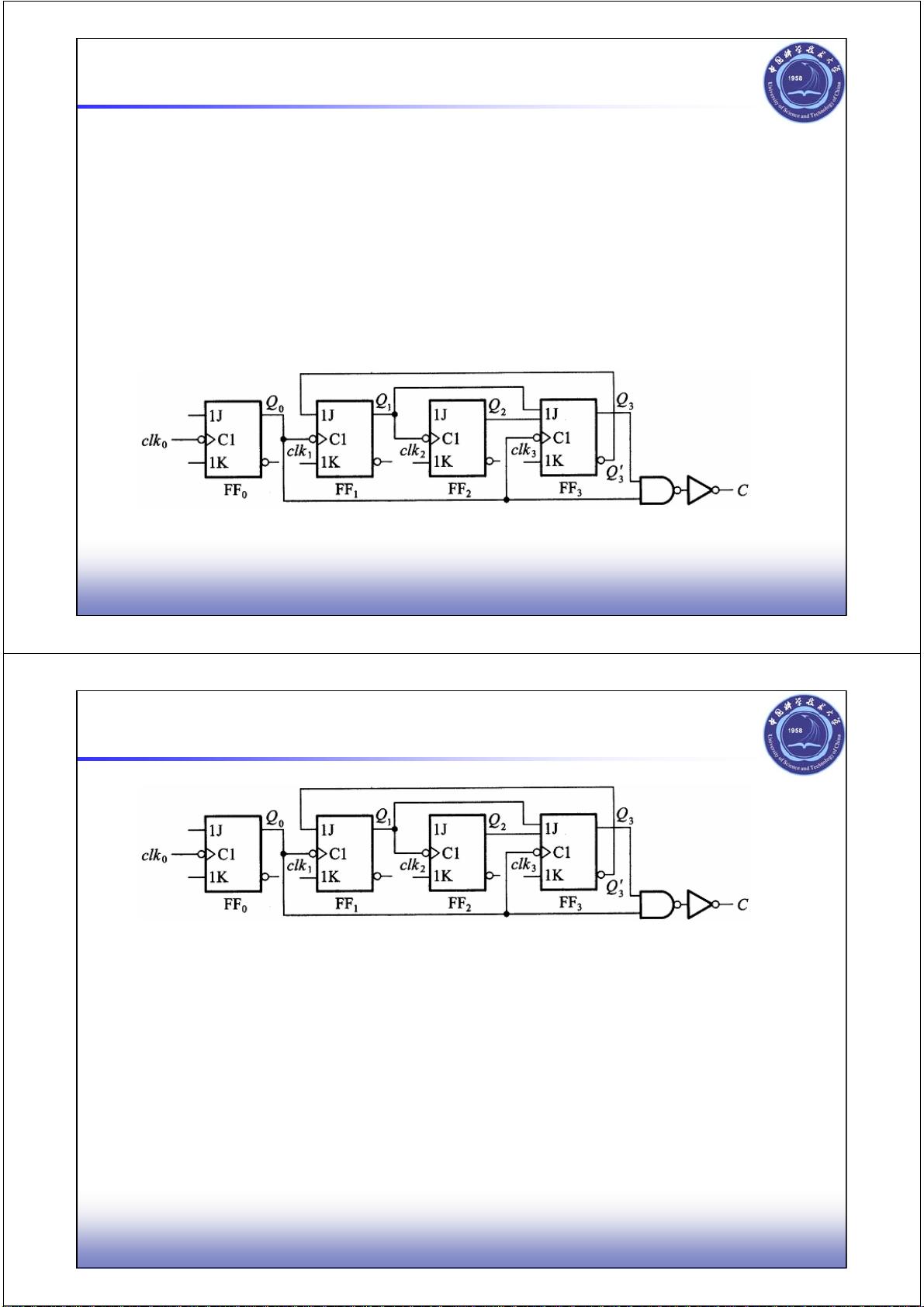

时序逻辑电路是数字电路的一种,与组合逻辑电路不同,它在任何时刻的输出不仅仅取决于当前输入,还依赖于电路的先前状态。这种特性使得时序逻辑电路能够处理和记忆信息,是构建计数器、寄存器、移位寄存器等复杂数字系统的关键组件。

时序逻辑电路的主要特点可以概括如下:

1. **逻辑功能特点**:时序逻辑电路的输出不仅由当前输入信号决定,还受电路内部状态的影响。这使得它们能实现记忆和顺序处理功能。

2. **电路结构特点**:时序逻辑电路通常由两部分组成,即**组合电路**和**存储电路**。存储电路用于保持状态,而组合电路则根据输入信号和存储电路的输出计算新的输出。存储电路的输出会反馈到组合电路的输入,形成一个闭环系统。

时序逻辑电路的描述方法主要包括:

1. **结构框图**:时序逻辑电路的结构可以用一个框图表示,其中包含输入变量、输出变量、存储电路的输入和输出信号。存储电路的输出被馈送到组合逻辑电路,共同决定电路的最终输出。

2. **功能描述**:时序逻辑电路的功能通常通过三个方程组来描述:

- **输出方程**:定义电路的输出与输入和当前状态之间的关系。

- **驱动方程**:描述存储电路的下一状态如何由当前输入和当前状态决定。

- **状态方程**:表示存储电路的状态如何更新。

时序逻辑电路的分析和设计方法包括理解和解耦这些方程,以及利用各种时序逻辑电路元件如触发器、计数器和移位寄存器等来实现特定功能。

此外,时序逻辑电路中可能存在的**竞争-冒险现象**是指由于电路中不同路径的延迟差异,导致在某些特定条件下输出出现短暂的不期望的毛刺。这种现象需要通过优化布线、添加滤波器或者采用高速设计技术来消除。

最后,随着可编程逻辑器件(如FPGA和CPLD)的发展,同步时序逻辑电路可以通过配置这些器件来快速实现,大大简化了设计流程并提高了灵活性。

时序逻辑电路是数字系统设计的核心,它们在数据处理、计算机内存、通信系统等众多领域都有广泛的应用。理解并掌握时序逻辑电路的设计和分析方法对于任何从事数字电子学或相关领域的工程师来说都是至关重要的。

2010-12-08 上传

2022-06-28 上传

2021-11-24 上传

225 浏览量

223 浏览量

w7513118

- 粉丝: 0

- 资源: 4

最新资源

- Apress.Pro.LINQ.Language.Integrated.Query.in.C#2008

- 阵列感应测井资料处理方法研究.pdf

- vb操作填空题答案看看就会

- 使用 ADOBE FLEX 3 开发 Adobe AIR 1.1 应用程序.pdf

- MFC教程课件,荣希学

- C++入门经典(3rd) .pdf

- JAVA基础。入门单词

- 数据结构课程设计 关于二叉树

- IDC机房方案,共四部分。

- cisco 4500 serial

- TCP-IP详解卷1 5.pdf

- TCP-IP详解 卷14.pdf

- EJB3.0实例教程

- OFDM-Based Broadband Wireless Networks:Design and Optimization

- C#实用书籍C# 语言规范

- 《TCP-IP详解卷1》