Xilinx UltraScale+ 100Gb以太网设计指南

下载需积分: 0 | PDF格式 | 5.71MB |

更新于2024-06-18

| 51 浏览量 | 举报

"Xilinx 100Gb以太网中文手册(pg203)"

Xilinx 100Gb以太网中文手册是针对Xilinx UltraScale+ FPGA平台的一个详细技术指南,主要介绍了集成的100G以太网子系统v3.1的相关信息。手册覆盖了从功能概述、IP核配置、内部逻辑接口到引脚端口的使用等多个方面,旨在帮助开发者理解和应用这一高级网络接口。

手册的第1章“简介”中,列出了功能特性总结,包括IP核的许可和订购信息。它强调了该IP核在高性能网络应用中的重要性,以及其在统计信息收集、可测试性、标准遵循等方面的特性。

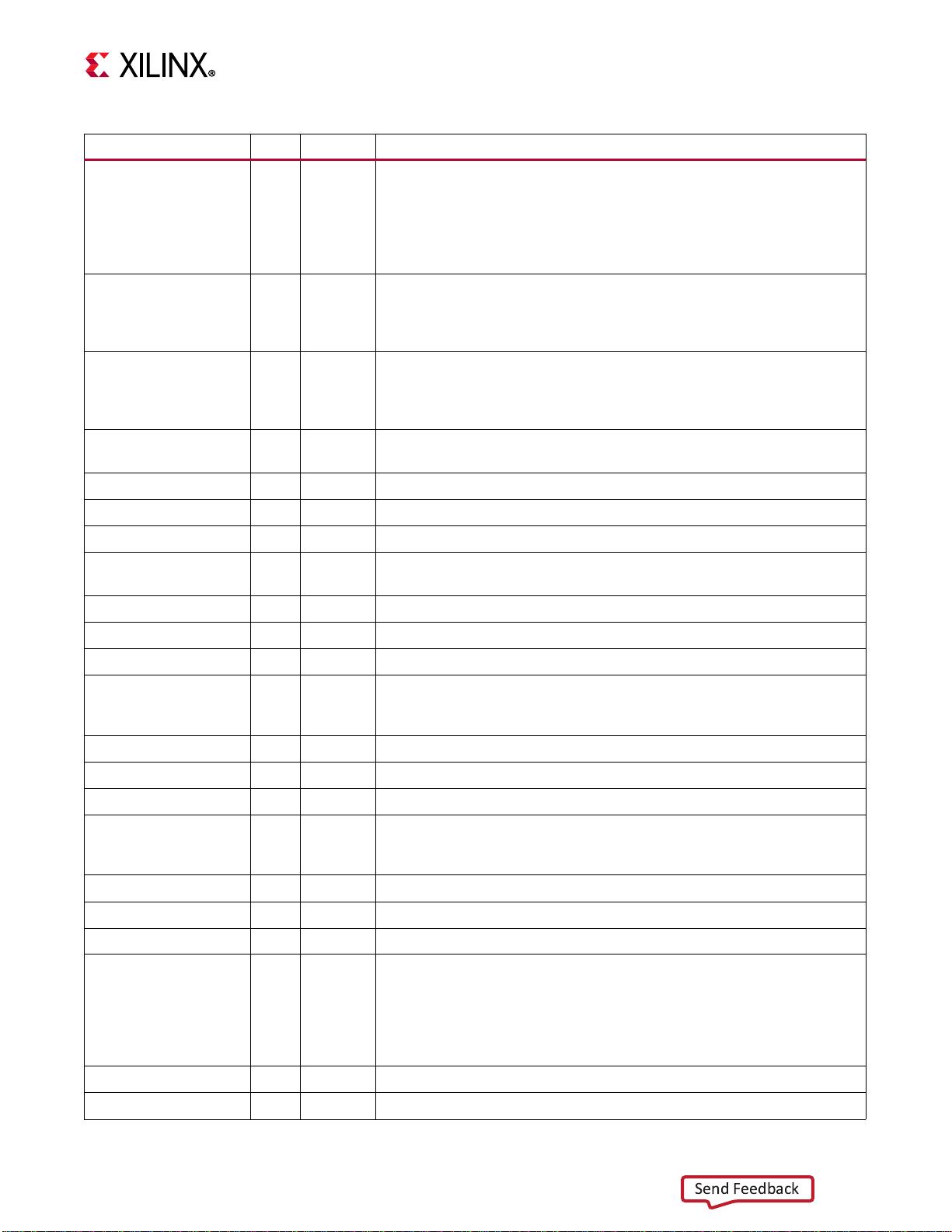

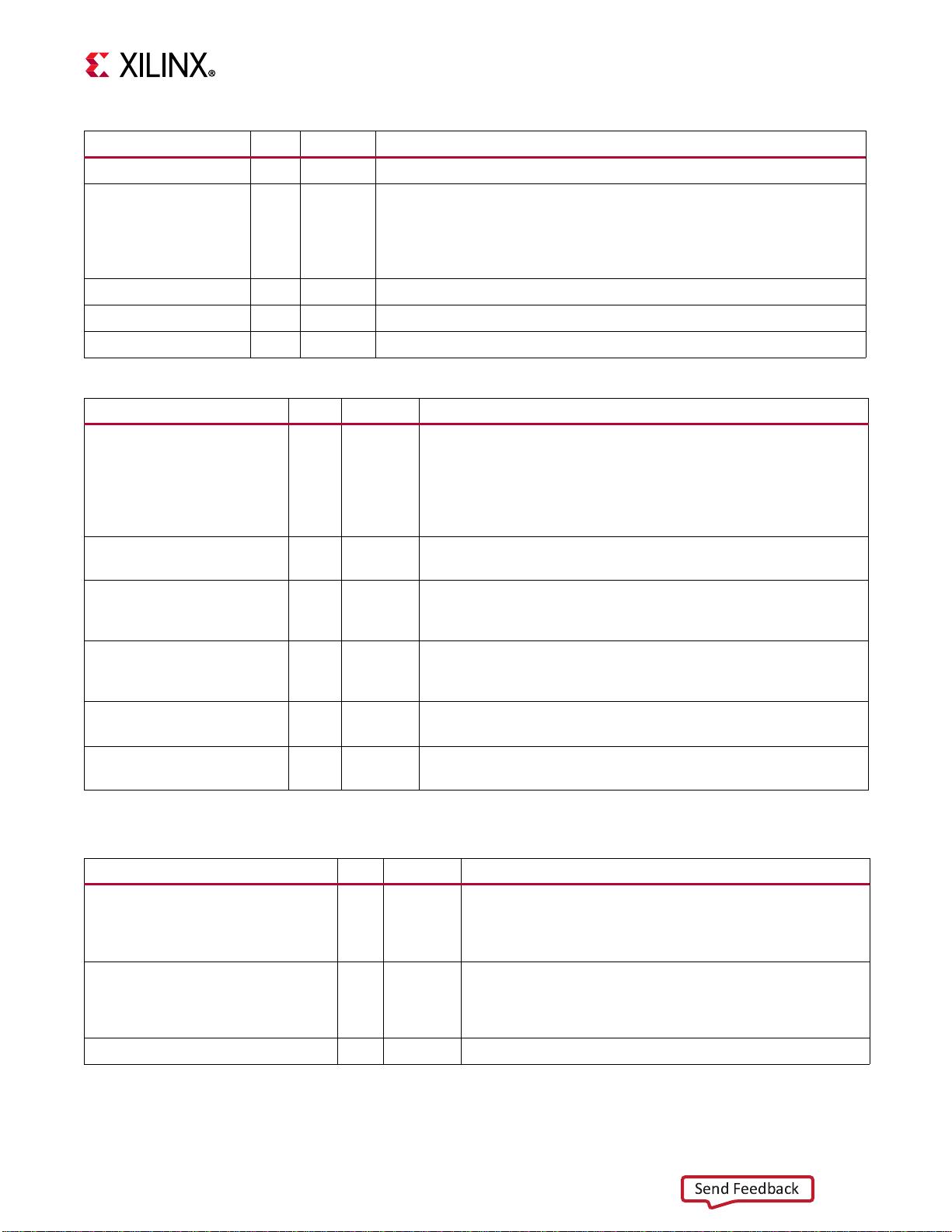

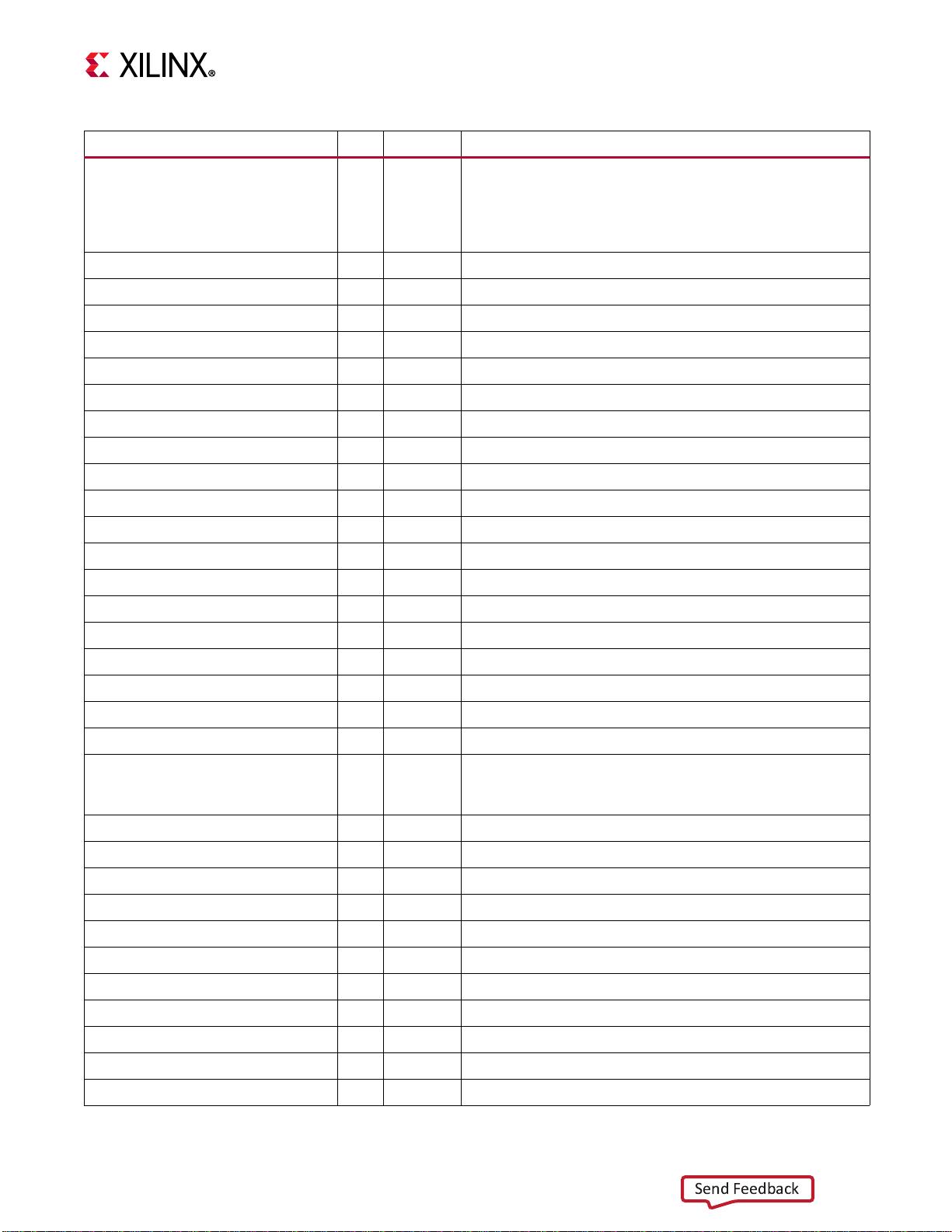

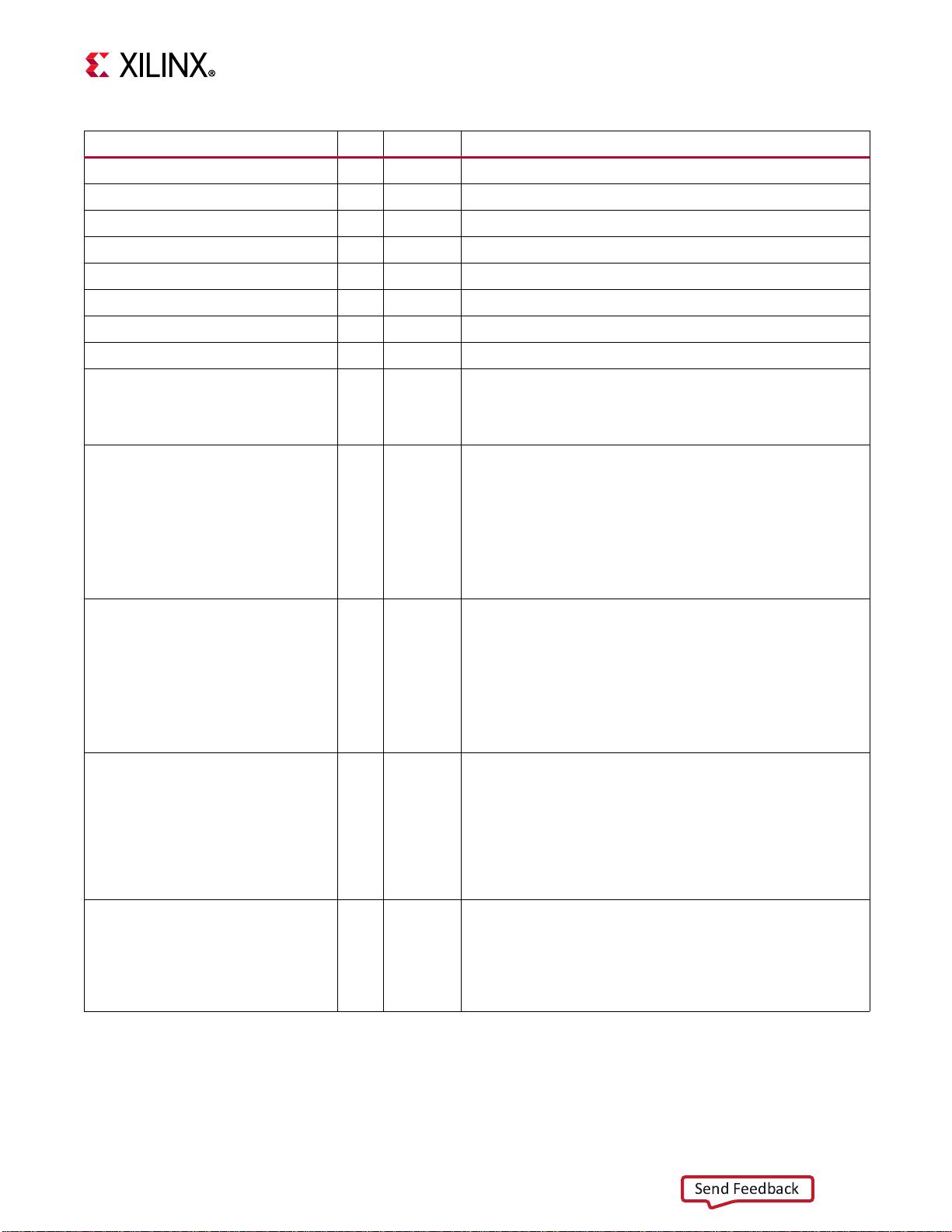

第2章“产品规格”详细阐述了IP核的典型操作方法,如统计数据的收集、可测试性功能、暂停操作,以及关于标准、性能和资源使用情况的详细说明。本章还提供了端口描述和属性描述,以便用户了解如何连接和配置各个接口。

第3章“用核设计”深入探讨了设计中的关键组件和操作,包括时钟和复位管理,以及CMAC(核心媒体访问控制器)的GTM映射。此外,还详细解释了协议层(如PCS)、Ethernet MAC、1588v2时间戳、收发器选择规则、动态重新配置端口等功能的工作原理。

第4章“设计流程步骤”为用户提供了从自定义和生成IP核,到约束设置、仿真、综合与实现的完整设计流程。这有助于开发者正确地将IP核集成到他们的FPGA设计中。

第5章“设计示例”提供了实际操作指导,包括用户接口、操作模式、传输事务流程、DRP操作、AXI4-Lite接口实现,以及RS-FEC(前向纠错)和OTN(光传输网络)接口的使用方法。此外,还包括了核初始化顺序、不同模式的用例和设计示例的仿真及综合实现过程。

附录部分涵盖了适用于Integrated 100G Ethernet的特定操作模式、RS-FEC引擎的使用、RX OTN接口的实现、TX OTN接口的软核功能、自动协商和链路训练的详细信息,以及从UltraScale到UltraScale+ FPGA平台的增强功能和升级指南。

这个手册对于理解和使用Xilinx UltraScale+ Integrated 100G Ethernet Subsystem v3.1的开发者来说是极其宝贵的参考资料,涵盖了从基本概念到高级特性的全面知识。通过这个手册,用户可以有效地集成和优化100Gb以太网功能,实现高效、可靠的网络通信解决方案。

相关推荐

wjh776a68

- 粉丝: 1121

- 资源: 21

最新资源

- 简约现代客厅模型

- 印花税统计excel模版下载

- neuros_system_rpi2:Raspberry Pi 2的基本神经系统配置

- 生成 MPSK BER VS SNR:生成 MPSK BER VS SNR-matlab开发

- fundamentos-nodejs-2021:到2021年火箭座位基础上的基础设施建设

- SWAT_Tools

- 内存虚拟硬盘C++源码

- angular-ui-bootstrap-floating-row:如果该区域可见,则允许一行浮动在页面顶部或它所属的位置的指令

- GIT_Collab_Branching_-WE

- angular6-rails5.2:描述如何将Rails 5.2和Angular6与Angular Ivy支持集成在一起

- React-Learning

- 使用Arduino和BitVoicer服务器进行语音识别-项目开发

- 工作计划及日志记录excel模板下载

- Alligator-Studio:工作室设计网络

- Tesis-2021

- 展台效果图3D设计

已收录资源合集

已收录资源合集