Verilog语法详解与测试模块编写

需积分: 5 101 浏览量

更新于2024-06-22

收藏 683KB PPT 举报

"夏闻宇Verilog-PPT.ppt 是一份关于Verilog语言的详细讲解,涵盖了测试模块的编写、高级语法特性和设计流程。该资料旨在帮助学习者复习和掌握编写复杂测试文件的技巧,进行完整的设计测试与验证。"

在Verilog中,测试模块的编写是验证数字逻辑设计的关键步骤。它包括了设置激励信号,模拟待验证设计的输入,然后比较实际输出与预期输出来确保设计功能的正确性。这份资料深入探讨了这一过程,强调了以下几个核心知识点:

1. **测试模块编写**:学习如何编写测试平台,这包括创建激励信号来驱动设计,以及定义期望的输出信号以便进行比较。简单的测试平台可能只包含基本的激励生成,而复杂的测试平台则可能涉及到更精细的时序控制和多事件的同步。

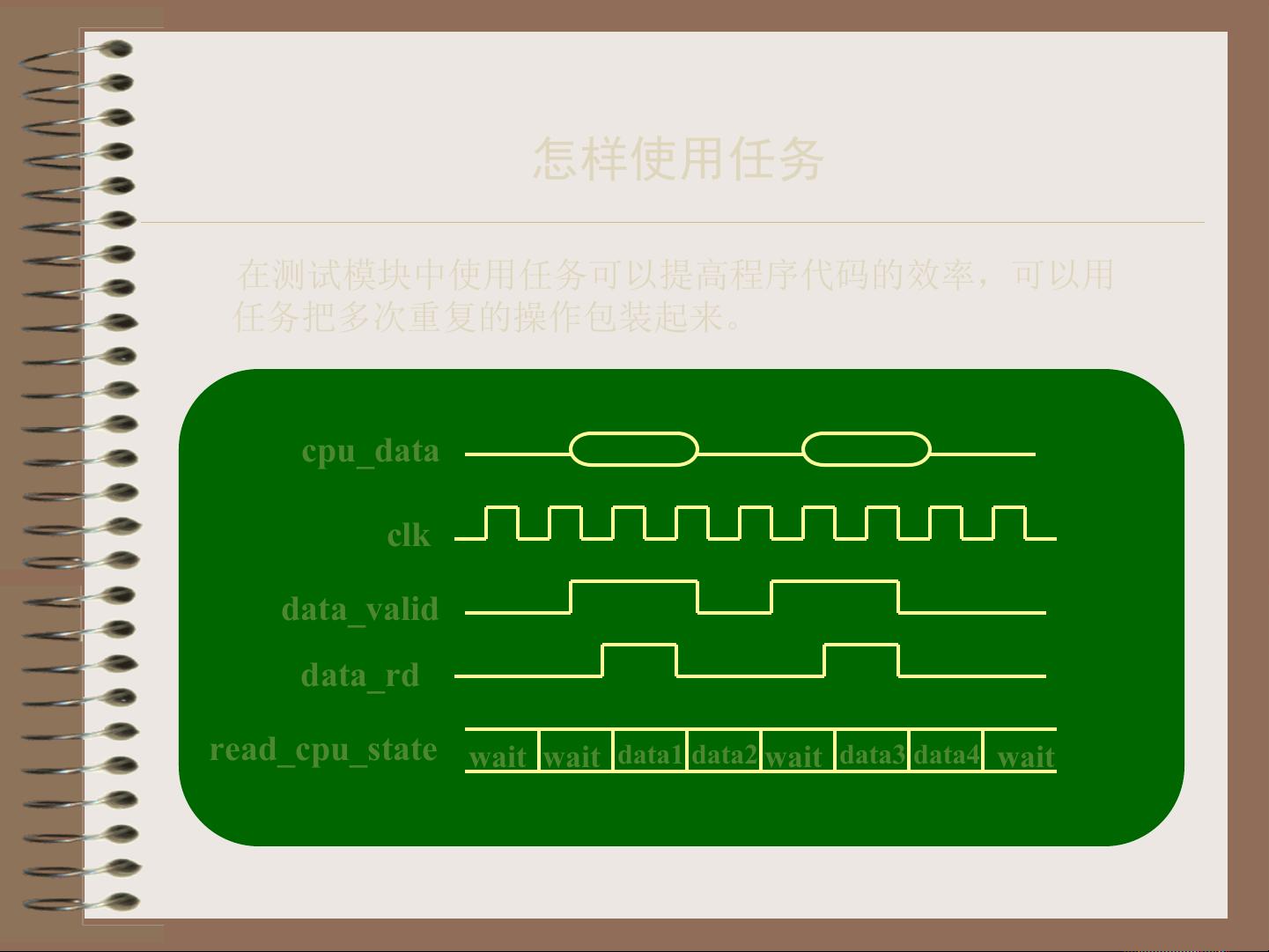

2. **高级语法**:除了基础的Verilog语法,还涵盖了函数、任务、文件、存储器模型、双向总线、用户定义协议(UDP)以及综合指令等高级特性。函数和任务是组织代码和提高复用性的工具,文件操作可用于数据输入输出,存贮器模型用于建立内存结构,双向总线处理双向通信,UDP定义自定义的数据传输协议,综合指令则影响硬件实现。

3. **并行块**:`fork…join`结构是Verilog中实现并发操作的关键,它可以表示多个事件在同一时刻启动并同时执行。例如,`initial`语句中的`fork`块可以并行执行多个任务,如循环或任务,提供了一种灵活的时间控制机制。

4. **设计流程**:Verilog设计通常包括输入文件(如设计文件、库文件和厂家元件)、编译器进行语法和逻辑检查,然后通过仿真器进行功能验证。输入文件包含激励信号和期望的输出信号,而输出文件则是仿真结果。

学习和掌握这些知识点,对于理解和编写高效的Verilog测试代码至关重要,能够帮助设计者确保数字电路在硬件实现前满足其功能需求。通过实例和实践,可以进一步加深对这些概念的理解,从而提升设计验证的能力。

289 浏览量

301 浏览量

374 浏览量

2024-12-27 上传

2025-01-02 上传

2021-10-01 上传

TrustZone_

- 粉丝: 2w+

- 资源: 32

最新资源

- 哥伦布蓝衣队 新标签页 壁纸收藏-crx插件

- SRDebugger 1.11.0 插件

- first-spring-mvc:ihavenoideawhatimdoing.jpg

- Linux系统安装详细视频教程

- SLitraniSim:内置在rootSLitrani中的简单Quartz和PMT检测器

- 一维_用matlab编写的FDTD一维程序_

- 横向滚动鼠标插件Horwheel特效代码

- 基于MPC控制器的自行车行驶转弯控制真实场景模拟matlab仿真

- Spark-Parquet

- Color Terror-crx插件

- JDK1.8-win64 -安装包

- confTool培训

- html5点击购物车弹出商品清单特效代码

- Python爬虫~已爬取目标网站所有文章,后续如何只获取新文章项目源码有详细注解,适合新手一看就懂.rar

- Watterson信道_短波信道_watterson信道_

- react-github-search-user-api