FPGA实现VME总线主模块设计与验证

"FPGA的VME主模块开发——基于FPGA实现VME总线控制器与TMS320C6701通讯"

本文详细介绍了如何利用FPGA技术开发一个VME(Versa Module Eurocard)总线的主模块,以实现与TMS320C6701 DSP的通信。VME总线是一种广泛应用于军事、医疗、运输和工业控制系统的异步并行总线标准,尽管已有多年历史,但其在高性能背板总线市场上的地位依然稳固。

VME总线接口控制芯片对于构建VME系统至关重要,然而国内尚未有成熟的产品。因此,该论文提出了一种创新方法,即通过FPGA来设计VME总线控制器的主模块,替代专门的接口控制芯片或国外产品。这种方法不仅节约成本,还具有高度的灵活性和可定制性。

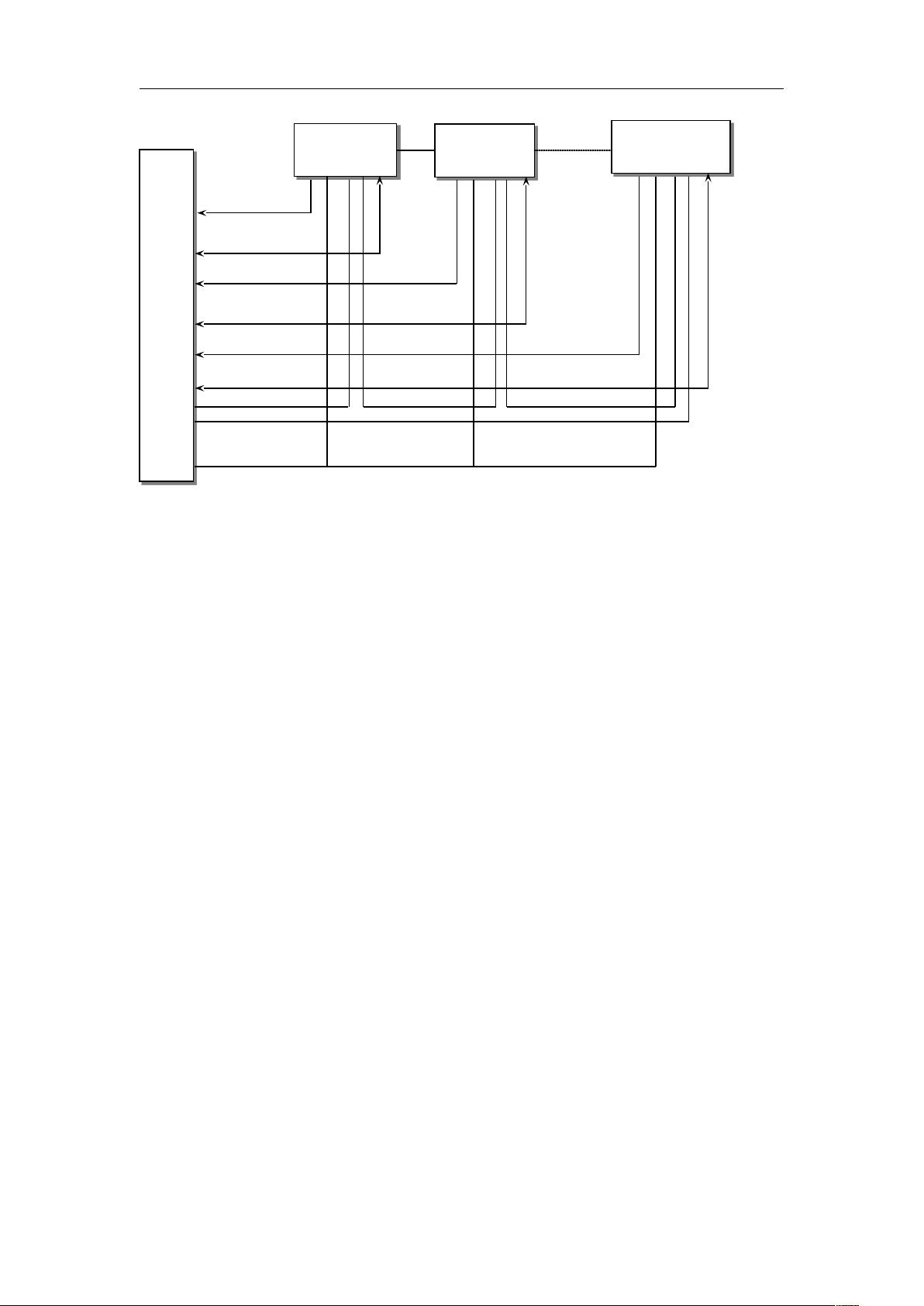

设计过程中,首先对VME开发资料、VME标准、VME桥片手册及相关文献进行了深入研究,这是理解VME标准并进行RTL(寄存器传输级)描述的基础。接着,采用正向设计方法,将模块划分为若干子模块,并逐一实现和验证。每个子模块在通过仿真验证后,整合到整体设计中进行联合仿真。

在FPGA实现阶段,由于VME标准定义的总线控制芯片功能繁多,包括众多微特性,直接用FPGA模拟全部功能难度较大、耗时且资源占用多。因此,项目聚焦于实际项目所需的功能模块,完成从行为级描述到功能仿真的全过程,包括翻译、物理映射和后仿真。

论文的重点在于VME状态机的设计,以及块数据传输机制的实现,这两点对于高效、可靠的总线通信至关重要。同时,FPGA仿真和验证是确保设计正确性的关键步骤,通过搭建FPGA验证平台并与应用硬件平台连接,进行了硬件层面的验证,确保了设计的可行性。

关键词:VME总线、状态机、块数据传输、FPGA仿真和验证

这篇论文提供了一个实用的FPGA实现VME主模块的方法,对于需要自主开发VME系统或利用FPGA技术进行接口设计的工程师来说,具有很高的参考价值。

116 浏览量

2021-07-13 上传

136 浏览量

221 浏览量

115 浏览量

179 浏览量