54 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 1, JANUARY 2003

A New Successive Approximation Architecture for

Low-Power Low-Cost CMOS A/D Converter

Chi-Sheng Lin and Bin-Da Liu, Senior Member, IEEE

Abstract—A new 6-bit 250 MS/s analog-to-digital converter

(ADC) is proposed for low-power low-cost CMOS integrated

systems. This design is based on an improved successive ap-

proximation ADC with a mixed-mode subtracter that minimizes

the overall power consumption and system complexity. The

experimental results indicate that this ADC works up to 250 MS/s

with power consumption less than 30 mW at 3.3 V. Moreover, the

operating voltage is scaled down to 0.8 V using a slight adjustment.

The ADC occupies only 0.1 mm

2

with the TSMC 0.35- m single

ploy quadruple metal (SPQM) CMOS technology. This design is

suitable for standard CMOS technology with low-power low-cost

VLSI implementation. It is well applied when embedded into

system-on-chip (SoC) circuit designs.

Index Terms—ADC, low voltage, parallel-like, successive

approximation.

I. INTRODUCTION

H

IGH performance CMOS analog-to-digital converters

(ADCs) are key components in mixed-signal integrated

circuits. Recent ADC applications are used increasingly in

digital data reading fields, such as hard disk drives, digital

videodiscs and local-area networks [1], [2]. High sampling

speed is required in all of these applications, resolution as low

as 6-bit, however, is sufficient.

Among these low-resolution high-speed CMOS ADC design

techniques, the flash architecture is one of the best solutions

for high-speed low-latency operations [3]. However, with the

number of bits

, the flash architecture requires com-

parators and the power, area and input capacitance are propor-

tional to

. Folding CMOS ADC is another good architec-

ture for high-speed operations and simple hardware design. This

is a technique for reducing the number of comparators used in

the flash architecture [4]. However, their performance degrades

with process variation [3].

In portable system designs, a low-voltage operation plays one

of the key design factors. The voltage limitations of this tech-

nology dictate that the ADC operates at the same low voltage

as the digital circuitry. In the literature, many low-voltage

CMOS ADC integrated circuits have been proposed [5], [6].

However, most of them are more complex circuit designs or

require higher power consumption. Consequently, they are not

suitable for portable system designs.

Manuscript received April 3, 2002; revised August 5, 2002. This work was

supported in part by the Chip Implementation Center, National Science Council

and by the Program of Promoting Academic Excellence, Ministry of Education,

under Grant EX-91-E-FA09-5-4, Taiwan, R.O.C.

The authors are with the Department of Electrical Engineering, Na-

tional Cheng Kung University, Tainan 70101, Taiwan, R.O.C. (e-mail:

bdliu@cad.ee.ncku.edu.tw).

Digital Object Identifier 10.1109/JSSC.2002.806257

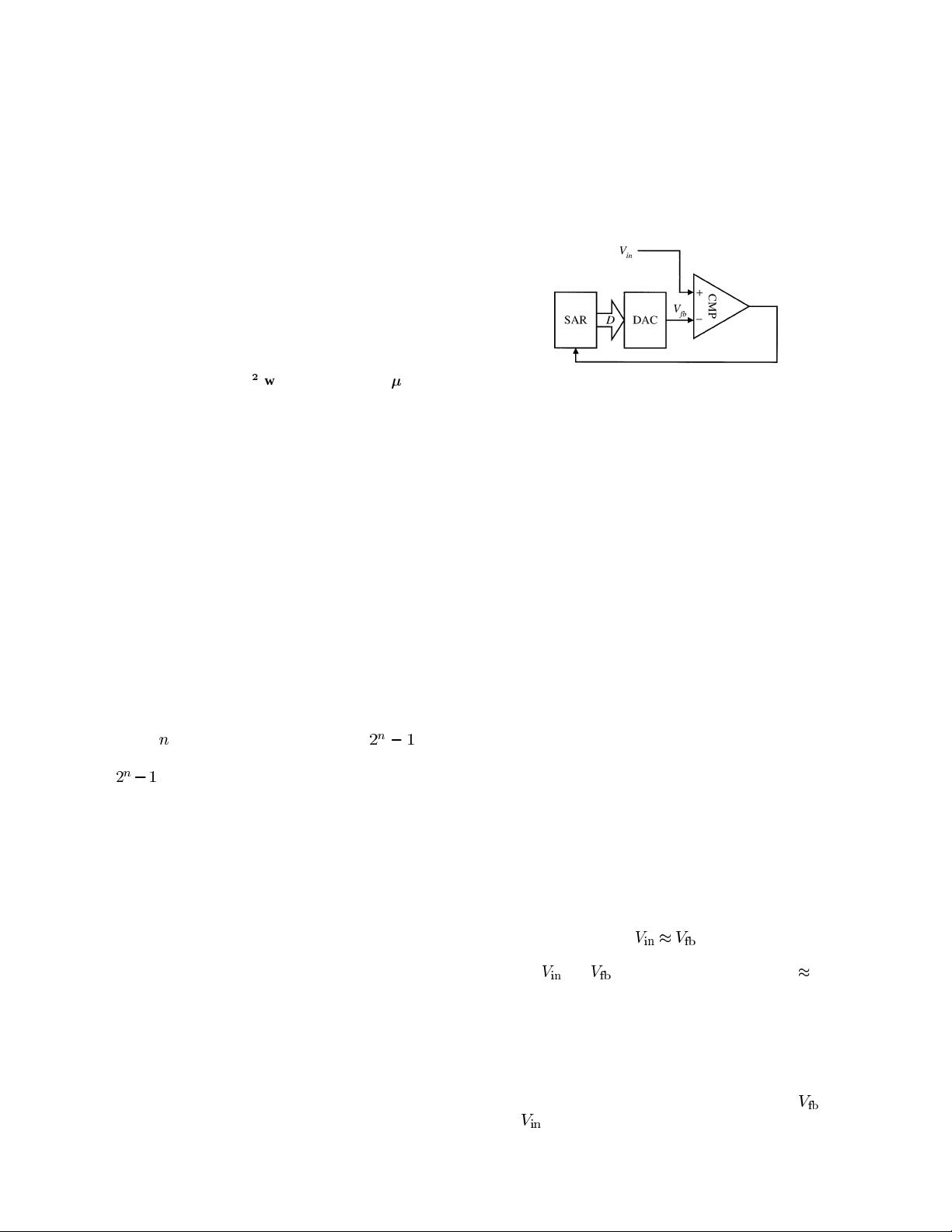

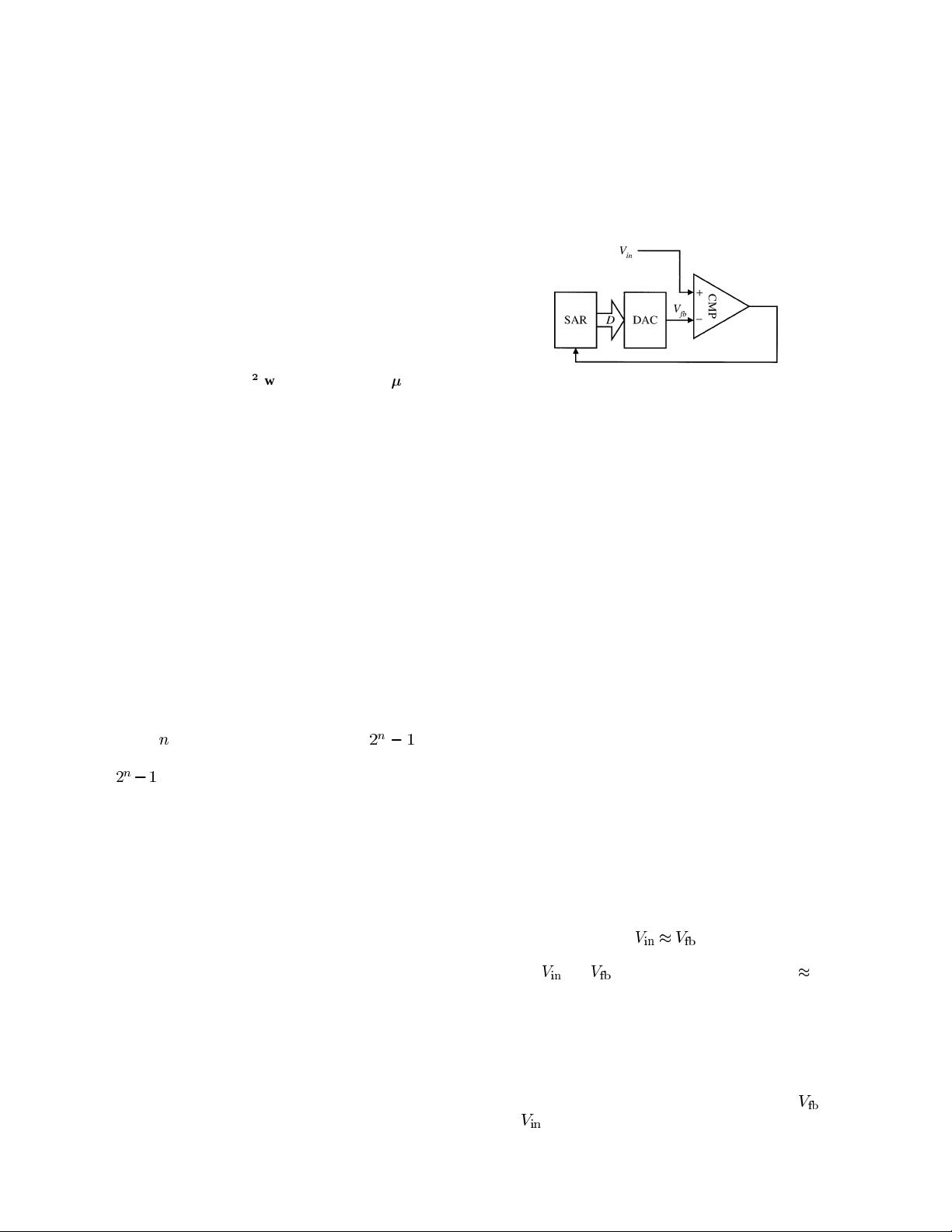

Fig. 1. Circuit diagram of a general successive approximation ADC.

In this paper, a novel circuit for low-power low-cost 6-bit

CMOS ADC is presented. A basic successive approximation

ADC (SA-ADC) will first be introduced and followed by an im-

proved successive approximation ADC (ISA-ADC) with stan-

dard CMOS technology. Based on the ISA-ADC architecture, a

parallel-like ISA-ADC architecture for high-speed low-resolu-

tion applications is developed.In addition, the adjustable feature

of the proposed circuit for scaling down the operating voltage

will be shown. The proposed converter has a simple hardware

design and low-accuracy comparator and therefore, is suitable

for low-power low-cost standard CMOS technology VLSI im-

plementation.

II. B

ASIC ARCHITECTURES OF SUCCESSIVE

APPROXIMATION ADC

The architecture of a general SA-ADC usually consists of

a rail-to-rail analog comparator, a digital-to-analog converter

(DAC)andasuccessiveapproximationregister (SAR), as shown

in Fig. 1 [7]. In general, the SAR is designed into the digital

circuitry. The DAC required in the ADC is designed based on

a R-2R ladder. Thus, both of them are suitable for the stan-

dard CMOS technology VLSI implementation. However, real-

izing a high-speed, high-accuracy and rail-to-rail MOS com-

parator concurrently remains a problem because of MOS device

mismatches [8], [9] and threshold voltage limitations [10]. The

input signals of this comparator is expressed by

(1)

where both

and are the comparator inputs and denotes

the comparator operation. This high-speed, offset compensated

and rail-to-rail comparator plays one of the key components for

SA-ADC designs.

To solve this problem, another SA-ADC architecture was de-

veloped to simplify the comparator requirement, as shown in

Fig. 2 [11]. This architecture employs an additional analog sub-

tracter to generate the differential value between the

signal

and the

signal, this way a comparator based on this archi-

tecture is applicable to compare the differential voltage level

0018-9200/03$17.00 © 2003 IEEE