没有合适的资源?快使用搜索试试~ 我知道了~

首页外星人M17R4笔记本电路图纸解:详细配置与特性

外星人M17R4笔记本电路图纸解:详细配置与特性

需积分: 50 21 下载量 77 浏览量

更新于2024-07-21

1

收藏 2.16MB PDF 举报

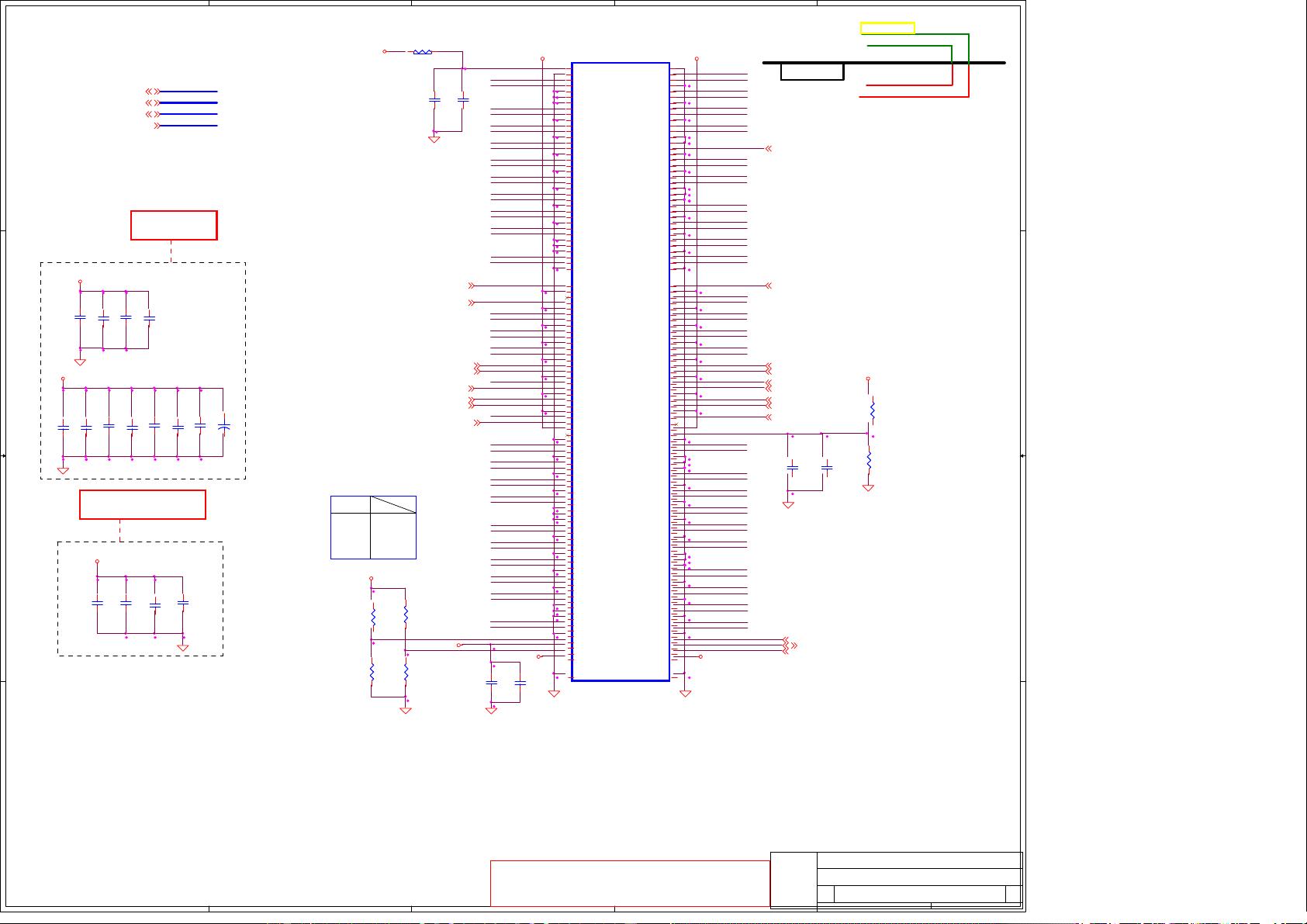

本文档详细展示了外星人(Alienware)M17r4笔记本电脑的电路图,由Compal Electronics, Inc.制造。电路图的标题表明了这款高端型号的内部构造,包括高速接口如100MHz频率的连接、5GB/s的数据传输速度,以及采用的最新技术如DMI x4代2和PCIe(FDI x8)等。SPI接口的出现可能涉及存储设备或专用芯片的通信。

文档的保密性标识强调了图纸中的信息为Del

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

CPU

JDIMM2 (H8)A6

J

D

IMM1 (H4)A2

JDIMM3 (H5.2)A0

J

D

IMM4 (H9.2)A4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWINGS AND SPECIFICATIONS CONTAINS CONFIDENTIAL,

TRADE SECRET, AND OTHER PROPRIETARY INFORMATION

OF DELL. ("DELL"). THIS DOCUMENT MAY NOT BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN

AUTHORIZATION OF DELL. IN ADDITION, NEITHER THIS

SHEET NOR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT

DELL'S EXPRESS WRITTEN CONSENT.

DELL CONFIDENTIAL/PROPRIETARY

SA1

1

0

0

1

DIMM1

DIMM2

DIMM3

DIMM4

Link Done

Layout Note:

P

lace near JDIMM1

Layout Note:

Place near JDIMM1.203,204

All VREF traces should

h

ave 10 mil trace width

M1 Circuit

M

3

Circuit (Processor Generated SO-DIMM VREF_DQ)

SA0

1

1

0

0

+DIMM0_VREF

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D10

DDR_A_D11

DDR_A_D18

DDR_A_D19

DDR_A_D21

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D32

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D45

DDR_A_D46

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_MA2

DDR_A_MA1

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

PCH_SMBDATA

PCH_SMBCLK

DDR_A_MA15

+VREF_CA

DDR_A_D23

DDR_A_D31

DDR_A_D17

DDR_A_D9

DDR_A_D13

DDR_A_D20

DDR_A_D16

DDR_A_D25

DDR_A_D30

DDR_A_D24

DDR_A_D14

DDR_A_D15

DDR_A_D12

DDR_A_D22

DDR_A_D39

DDR_A_D54

DDR_A_D33

DDR_A_D38

DDR_A_D47

DDR_A_D44

DDR_A_D48

DDR3_DRAMRST#

DDR_A_MA0

DDR_A_D63

DDR_CS4_DIMMC#

DDR_CKE5_DIMMC

M_CLK_DDR5

M_CLK_DDR#5

M_ODT4

M_ODT5

DDR_CS5_DIMMC#

DDR_CKE4_DIMMC

M_CLK_DDR4

M_CLK_DDR#4

M_THERMAL#

DRAMRST_CNTRL_PCH

DRAMRST_CNTRL_PCH

+1.5V

+1.5V

+3VS

+0.75VS

+0.75VS

+V_DDR_REFA

+1.5V

+3VS

+1.5V

+1.5V

+0.75VS

+1.5V

+V_DDR_REFB

+1.5V

+V_DDR_REFA

+V_DDR_REFA

+V_DDR_REFB

DDR_A_DQS#[0..7]6,13

DDR_A_DQS[0..7]6,13

DDR_A_D[0..63]6,13

DDR_A_MA[0..15]6,13

DDR_CKE4_DIMMC6

DDR_A_BS26,13

M_CLK_DDR46

M_CLK_DDR#46

DDR_A_WE#6,13

DDR_A_BS06,13

DDR_CS5_DIMMC#6

DDR_A_CAS#6,13

M_THERMAL# 12,13,14,47

PCH_SMBDATA 5,12,13,14,17,37,38,39

PCH_SMBCLK 5,12,13,14,17,37,38,39

DDR3_DRAMRST# 6,12,13,14

DDR_CKE5_DIMMC 6

M_CLK_DDR5 6

M_CLK_DDR#5 6

DDR_A_BS1 6,13

DDR_A_RAS# 6,13

DDR_CS4_DIMMC# 6

M_ODT4 6

M_ODT5 6

DRAMRST_CNTRL_PCH6,17

+V_DDR_REFA_R 9

+V_DDR_REFB_R 9

Title

S

i

ze Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMA

12 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMA

12 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMA

12 71Friday, March 02, 2012

Compal Electronics, Inc.

RD5

1K_0402_1%~D

RD5

1K_0402_1%~D

1

2

CD22

2.2U_0603_6.3V6K~D

CD22

2.2U_0603_6.3V6K~D

1

2

RD16

1K_0402_1%~D

RD16

1K_0402_1%~D

1

2

CD4

1U_0402_6.3V6K~D

CD4

1U_0402_6.3V6K~D

1

2

RD35

10K_0402_5%~D

RD35

10K_0402_5%~D

1

2

CD10

10U_0603_6.3V6M~D

CD10

10U_0603_6.3V6M~D

1

2

CD21

0.1U_0402_16V4Z~D

CD21

0.1U_0402_16V4Z~D

1

2

CD6

1U_0402_6.3V6K~D

CD6

1U_0402_6.3V6K~D

1

2

G

D

S

QC6

BSS138_SOT23~D

G

D

S

QC6

BSS138_SOT23~D

2

1

3

RD3

1K_0402_1%~D

RD3

1K_0402_1%~D

1

2

RD7

10K_0402_5%~D

RD7

10K_0402_5%~D

1

2

G

D

S

QC7

BSS138_SOT23~D

G

D

S

QC7

BSS138_SOT23~D

2

1

3

RD1

1K_0402_1%~D

RD1

1K_0402_1%~D

1

2

RD4

1K_0402_1%~D

RD4

1K_0402_1%~D

1

2

RC84

1K_0402_1%~D

@

RC84

1K_0402_1%~D

@

1

2

CD9

10U_0603_6.3V6M~D

CD9

10U_0603_6.3V6M~D

1

2

CD16

0.1U_0402_16V4Z~D

CD16

0.1U_0402_16V4Z~D

1

2

RD36

10K_0402_5%~D

@

RD36

10K_0402_5%~D

@

1

2

RD2 0_0402_5%~D@

RD2 0_0402_5%~D@

1

2

CD11

10U_0603_6.3V6M~D

CD11

10U_0603_6.3V6M~D

1

2

CD2

0.1U_0402_16V4Z~D

CD2

0.1U_0402_16V4Z~D

1

2

CD12

10U_0603_6.3V6M~D

CD12

10U_0603_6.3V6M~D

1

2

CD1

2.2U_0603_6.3V6K~D

CD1

2.2U_0603_6.3V6K~D

1

2

RC85

1K_0402_1%~D

@

RC85

1K_0402_1%~D

@

1

2

JDIMM1

TYCO_2-2013287-1

JDIMM1

TYCO_2-2013287-1

VREF_DQ

1

VSS

3

DQ0

5

DQ1

7

VSS

9

DM0

11

VSS

13

DQ2

15

DQ3

17

VSS

19

DQ8

21

DQ9

23

VSS

25

DQS1#

27

DQS1

29

VSS

31

DQ10

33

DQ11

35

VSS

37

DQ16

39

DQ17

41

VSS

43

DQS2#

45

DQS2

47

VSS

49

DQ18

51

DQ19

53

VSS

55

DQ24

57

DQ25

59

VSS

61

DM3

63

VSS

65

DQ26

67

DQ27

69

VSS

71

CKE0

73

VDD

75

NC

77

BA2

79

VDD

81

A12/BC#

83

A9

85

VDD

87

A8

89

A5

91

VDD

93

A3

95

A1

97

VDD

99

CK0

101

CK0#

103

VDD

105

A10/AP

107

BA0

109

VDD

111

WE#

113

CAS#

115

VDD

117

A13

119

S1#

121

VDD

123

TEST

125

VSS

127

DQ32

129

DQ33

131

VSS

133

DQS4#

135

DQS4

137

VSS

139

DQ34

141

DQ35

143

VSS

2

DQ4

4

DQ5

6

VSS

8

DQS0#

10

DQS0

12

VSS

14

DQ6

16

DQ7

18

VSS

20

DQ12

22

DQ13

24

VSS

26

DM1

28

RESET#

30

VSS

32

DQ14

34

DQ15

36

VSS

38

DQ20

40

DQ21

42

VSS

44

DM2

46

VSS

48

DQ22

50

DQ23

52

VSS

54

DQ28

56

DQ29

58

VSS

60

DQS3#

62

DQS3

64

VSS

66

DQ30

68

DQ31

70

VSS

72

CKE1

74

VDD

76

A15

78

A14

80

VDD

82

A11

84

A7

86

VDD

88

A6

90

A4

92

VDD

94

A2

96

A0

98

VDD

100

CK1

102

CK1#

104

VDD

106

BA1

108

RAS#

110

VDD

112

S0#

114

ODT0

116

VDD

118

ODT1

120

NC

122

VDD

124

VREF_CA

126

VSS

128

DQ36

130

DQ37

132

VSS

134

DM4

136

VSS

138

DQ38

140

DQ39

142

VSS

144

VSS

145

DQ40

147

DQ41

149

VSS

151

DM5

153

VSS

155

DQ42

157

DQ43

159

VSS

161

DQ48

163

DQ49

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SA0

197

VDDSPD

199

DQ44

146

DQ45

148

VSS

150

DQS5#

152

DQS5

154

VSS

156

DQ46

158

DQ47

160

VSS

162

DQ52

164

DQ53

166

VSS

168

DM6

170

VSS

172

DQ54

174

DQ55

176

VSS

178

DQ60

180

DQ61

182

VSS

184

DQS7#

186

DQS7

188

VSS

190

DQ62

192

DQ63

194

VSS

196

EVENT#

198

SDA

200

SA1

201

SCL

202

VTT

203

VTT

204

GND1

205

GND2

206

CD13

10U_0603_6.3V6M~D

@

CD13

10U_0603_6.3V6M~D

@

1

2

CD17

1U_0402_6.3V6K~D

CD17

1U_0402_6.3V6K~D

1

2

CD18

1U_0402_6.3V6K~D

CD18

1U_0402_6.3V6K~D

1

2

CD7

10U_0603_6.3V6M~D

CD7

10U_0603_6.3V6M~D

1

2

RC82 0_0402_5%~D@

RC82 0_0402_5%~D@

1

2

+

CD14

330U_SX_2VY~D

+

CD14

330U_SX_2VY~D

1

2

CD20

1U_0402_6.3V6K~D

CD20

1U_0402_6.3V6K~D

1

2

CD3

1U_0402_6.3V6K~D

CD3

1U_0402_6.3V6K~D

1

2

CD15

2.2U_0603_6.3V6K~D

CD15

2.2U_0603_6.3V6K~D

1

2

CD19

1U_0402_6.3V6K~D

CD19

1U_0402_6.3V6K~D

1

2

CD5

1U_0402_6.3V6K~D

CD5

1U_0402_6.3V6K~D

1

2

RD6

10K_0402_5%~D

@

RD6

10K_0402_5%~D

@

1

2

RC83 0_0402_5%~D@

RC83 0_0402_5%~D@

1

2

CD8

10U_0603_6.3V6M~D

CD8

10U_0603_6.3V6M~D

1

2

RD15

1K_0402_1%~D

RD15

1K_0402_1%~D

1

2

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

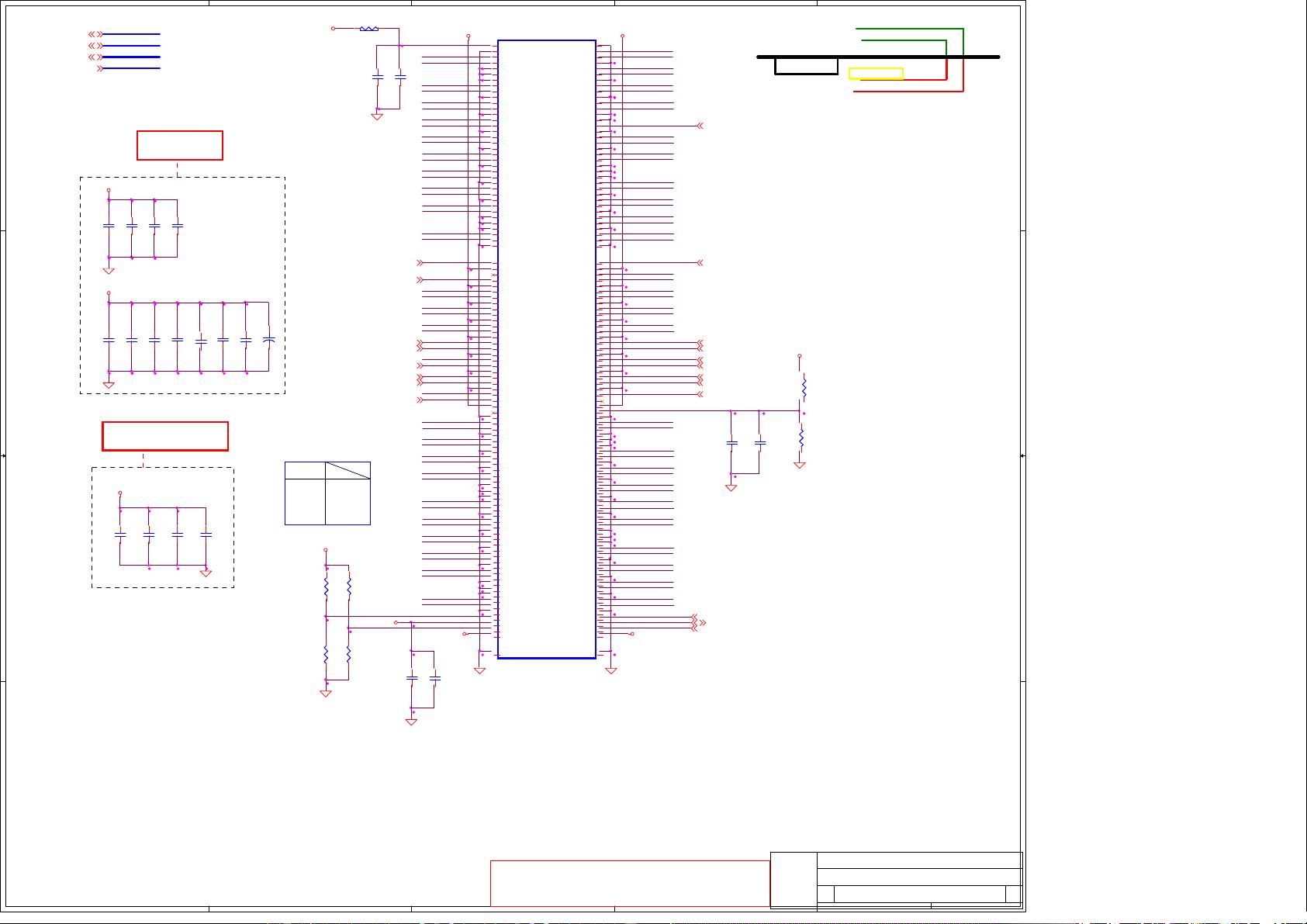

Layout Note:

Place near JDIMMB.203,204

Note:

Check voltage tolerance of

VREF_DQ at the DIMM socket

Layout Note:

Place near JDIMMB

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWINGS AND SPECIFICATIONS CONTAINS CONFIDENTIAL,

T

RADE SECRET, AND OTHER PROPRIETARY INFORMATION

OF DELL. ("DELL"). THIS DOCUMENT MAY NOT BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN

AUTHORIZATION OF DELL. IN ADDITION, NEITHER THIS

SHEET NOR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT

DELL'S EXPRESS WRITTEN CONSENT.

Link Done

SA0

0

0

1

1

1

SA1

0

0

DIMM4

DIMM3

DIMM2

DIMM1

1

CPU

JDIMM3 (H5.2)A0

JDIMM1 (H4)A2

J

D

IMM2 (H8)A6

JDIMM4 (H9.2)A4

DDR_B_MA7

DDR_B_D22

DDR_B_D20

DDR_B_D52

DDR_B_MA14

DDR_B_D27

DDR3_DRAMRST#

DDR_B_D37

DDR_B_D36

DDR_B_MA6

DDR_B_D23

DDR_B_D21

DDR_B_D44

DDR_B_DQS#3

DDR_B_D54

DDR_B_D53

DDR_B_D46

DDR_B_D14

DDR_B_MA4

DDR_B_D45

DDR_B_D38

DDR_B_BS1

DDR_B_DQS3

DDR_B_D7

DDR_B_D6

DDR_B_D55

DDR_B_D47

DDR_B_D15

DDR_B_D28

DDR_B_RAS#

DDR_B_MA2

DDR_B_D29

DDR_B_DQS#5

DDR_B_MA11

DDR_B_D30

DDR_B_D12

DDR_B_D60

DDR_B_D39

DDR_B_MA0

DDR_B_DQS5

DDR_B_D31

DDR_B_D58

DDR_B_D13

DDR_B_D59

DDR_B_BS2

DDR_B_MA12

DDR_B_MA9

DDR_B_D4

DDR_B_MA8

DDR_B_D5

DDR_B_MA5

DDR_B_DQS#0

DDR_B_MA3

DDR_B_DQS0

DDR_B_MA1

DDR_B_MA10

DDR_B_BS0

DDR_B_WE#

DDR_B_CAS#

DDR_B_MA15

DDR_B_MA13

DDR_B_D0

DDR_B_D1

DDR_B_D32

DDR_B_D33

DDR_B_D2

DDR_B_DQS#4

DDR_B_D3

DDR_B_DQS4

DDR_B_D8

DDR_B_D34

DDR_B_D9

DDR_B_D35

DDR_B_DQS#1

DDR_B_D40

DDR_B_D61

DDR_B_DQS1

DDR_B_D41

DDR_B_DQS#7

DDR_B_D10

DDR_B_DQS7

DDR_B_D11

PCH_SMBDATA

PCH_SMBCLK

DDR_B_D42

DDR_B_D62

DDR_B_D16

DDR_B_D43

DDR_B_D63

DDR_B_D17

DDR_B_D48

DDR_B_DQS#2

DDR_B_D49

DDR_B_DQS2

+VREF_CB

DDR_B_DQS#6

DDR_B_D18

DDR_B_DQS6

DDR_B_D19

DDR_B_D50

DDR_B_D24

DDR_B_D51

DDR_B_D25

DDR_B_D56

DDR_B_D57

DDR_B_D26

+DIMM1_VREF

M_ODT6

DDR_CKE7_DIMMD

M_ODT7

M_CLK_DDR7

M_CLK_DDR#7

DDR_CS6_DIMMD#

DDR_CKE6_DIMMD

M_CLK_DDR6

M_CLK_DDR#6

DDR_CS7_DIMMD#

M_THERMAL#

+1.5V

+0.75VS

+3VS

+3VS

+1.5V

+0.75VS

+1.5V

+1.5V

+0.75VS

+V_DDR_REFB

+1.5V

DDR_B_DQS#[0..7]6,14

DDR_B_DQS[0..7]6,14

DDR_B_D[0..63]6,14

DDR_B_MA[0..15]6,14

DDR_CKE6_DIMMD6

DDR_B_BS26,14

M_CLK_DDR66

M_CLK_DDR#66

DDR_B_BS06,14

DDR_B_WE#6,14

DDR_B_CAS#6,14

DDR_CS7_DIMMD#6

PCH_SMBDATA 5,11,13,14,17,37,38,39

PCH_SMBCLK 5,11,13,14,17,37,38,39

M_THERMAL# 11,13,14,47

DDR_CKE7_DIMMD 6

M_CLK_DDR7 6

M_CLK_DDR#7 6

DDR_B_BS1 6,14

DDR_B_RAS# 6,14

DDR_CS6_DIMMD# 6

M_ODT6 6

M_ODT7 6

DDR3_DRAMRST# 6,11,13,14

Title

S

i

ze Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMB

13 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMB

13 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMB

13 71Friday, March 02, 2012

Compal Electronics, Inc.

CD46

0.1U_0402_16V4Z~D

CD46

0.1U_0402_16V4Z~D

1

2

CD38

10U_0603_6.3V6M~D

@

CD38

10U_0603_6.3V6M~D

@

1

2

CD45

1U_0402_6.3V6K~D

CD45

1U_0402_6.3V6K~D

1

2

RD19

10K_0402_5%~D

RD19

10K_0402_5%~D

1

2

CD30

1U_0402_6.3V6K~D

CD30

1U_0402_6.3V6K~D

1

2

CD47

2.2U_0603_6.3V6K~D

CD47

2.2U_0603_6.3V6K~D

1

2

CD36

10U_0603_6.3V6M~D

CD36

10U_0603_6.3V6M~D

1

2

CD28

1U_0402_6.3V6K~D

CD28

1U_0402_6.3V6K~D

1

2

RD18

1K_0402_1%~D

RD18

1K_0402_1%~D

1

2

CD27

2.2U_0603_6.3V6K~D

CD27

2.2U_0603_6.3V6K~D

1

2

CD43

1U_0402_6.3V6K~D

CD43

1U_0402_6.3V6K~D

1

2

CD26

0.1U_0402_16V4Z~D

CD26

0.1U_0402_16V4Z~D

1

2

RD20

10K_0402_5%~D

@

RD20

10K_0402_5%~D

@

1

2

CD34

10U_0603_6.3V6M~D

CD34

10U_0603_6.3V6M~D

1

2

CD42

1U_0402_6.3V6K~D

CD42

1U_0402_6.3V6K~D

1

2

RD37

10K_0402_5%~D

@

RD37

10K_0402_5%~D

@

1

2

JDIMM2

TYCO_2-2013298-1

JDIMM2

TYCO_2-2013298-1

VREF_DQ

1

VSS

3

DQ0

5

DQ1

7

VSS

9

DM0

11

VSS

13

DQ2

15

DQ3

17

VSS

19

DQ8

21

DQ9

23

VSS

25

DQS1#

27

DQS1

29

VSS

31

DQ10

33

DQ11

35

VSS

37

DQ16

39

DQ17

41

VSS

43

DQS2#

45

DQS2

47

VSS

49

DQ18

51

DQ19

53

VSS

55

DQ24

57

DQ25

59

VSS

61

DM3

63

VSS

65

DQ26

67

DQ27

69

VSS

71

CKE0

73

VDD

75

NC

77

BA2

79

VDD

81

A12/BC#

83

A9

85

VDD

87

A8

89

A5

91

VDD

93

A3

95

A1

97

VDD

99

CK0

101

CK0#

103

VDD

105

A10/AP

107

BA0

109

VDD

111

WE#

113

CAS#

115

VDD

117

A13

119

S1#

121

VDD

123

TEST

125

VSS

127

DQ32

129

DQ33

131

VSS

133

DQS4#

135

DQS4

137

VSS

139

DQ34

141

DQ35

143

VSS

2

DQ4

4

DQ5

6

VSS

8

DQS0#

10

DQS0

12

VSS

14

DQ6

16

DQ7

18

VSS

20

DQ12

22

DQ13

24

VSS

26

DM1

28

RESET#

30

VSS

32

DQ14

34

DQ15

36

VSS

38

DQ20

40

DQ21

42

VSS

44

DM2

46

VSS

48

DQ22

50

DQ23

52

VSS

54

DQ28

56

DQ29

58

VSS

60

DQS3#

62

DQS3

64

VSS

66

DQ30

68

DQ31

70

VSS

72

CKE1

74

VDD

76

A15

78

A14

80

VDD

82

A11

84

A7

86

VDD

88

A6

90

A4

92

VDD

94

A2

96

A0

98

VDD

100

CK1

102

CK1#

104

VDD

106

BA1

108

RAS#

110

VDD

112

S0#

114

ODT0

116

VDD

118

ODT1

120

NC

122

VDD

124

VREF_CA

126

VSS

128

DQ36

130

DQ37

132

VSS

134

DM4

136

VSS

138

DQ38

140

DQ39

142

VSS

144

VSS

145

DQ40

147

DQ41

149

VSS

151

DM5

153

VSS

155

DQ42

157

DQ43

159

VSS

161

DQ48

163

DQ49

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SA0

197

VDDSPD

199

DQ44

146

DQ45

148

VSS

150

DQS5#

152

DQS5

154

VSS

156

DQ46

158

DQ47

160

VSS

162

DQ52

164

DQ53

166

VSS

168

DM6

170

VSS

172

DQ54

174

DQ55

176

VSS

178

DQ60

180

DQ61

182

VSS

184

DQS7#

186

DQS7

188

VSS

190

DQ62

192

DQ63

194

VSS

196

EVENT#

198

SDA

200

SA1

201

SCL

202

VTT

203

VTT

204

GND1

205

GND2

206

CD31

1U_0402_6.3V6K~D

CD31

1U_0402_6.3V6K~D

1

2

CD37

10U_0603_6.3V6M~D

CD37

10U_0603_6.3V6M~D

1

2

RD17

1K_0402_1%~D

RD17

1K_0402_1%~D

1

2

RD38

10K_0402_5%~D

RD38

10K_0402_5%~D

1

2

CD44

1U_0402_6.3V6K~D

CD44

1U_0402_6.3V6K~D

1

2

CD29

1U_0402_6.3V6K~D

CD29

1U_0402_6.3V6K~D

1

2

+

CD39

330U_SX_2VY~D

+

CD39

330U_SX_2VY~D

1

2

CD35

10U_0603_6.3V6M~D

CD35

10U_0603_6.3V6M~D

1

2

CD40

2.2U_0603_6.3V6K~D

CD40

2.2U_0603_6.3V6K~D

1

2

RD14 0_0402_5%~D@

RD14 0_0402_5%~D@

1

2

CD41

0.1U_0402_16V4Z~D

CD41

0.1U_0402_16V4Z~D

1

2

CD32

10U_0603_6.3V6M~D

CD32

10U_0603_6.3V6M~D

1

2

CD33

10U_0603_6.3V6M~D

CD33

10U_0603_6.3V6M~D

1

2

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

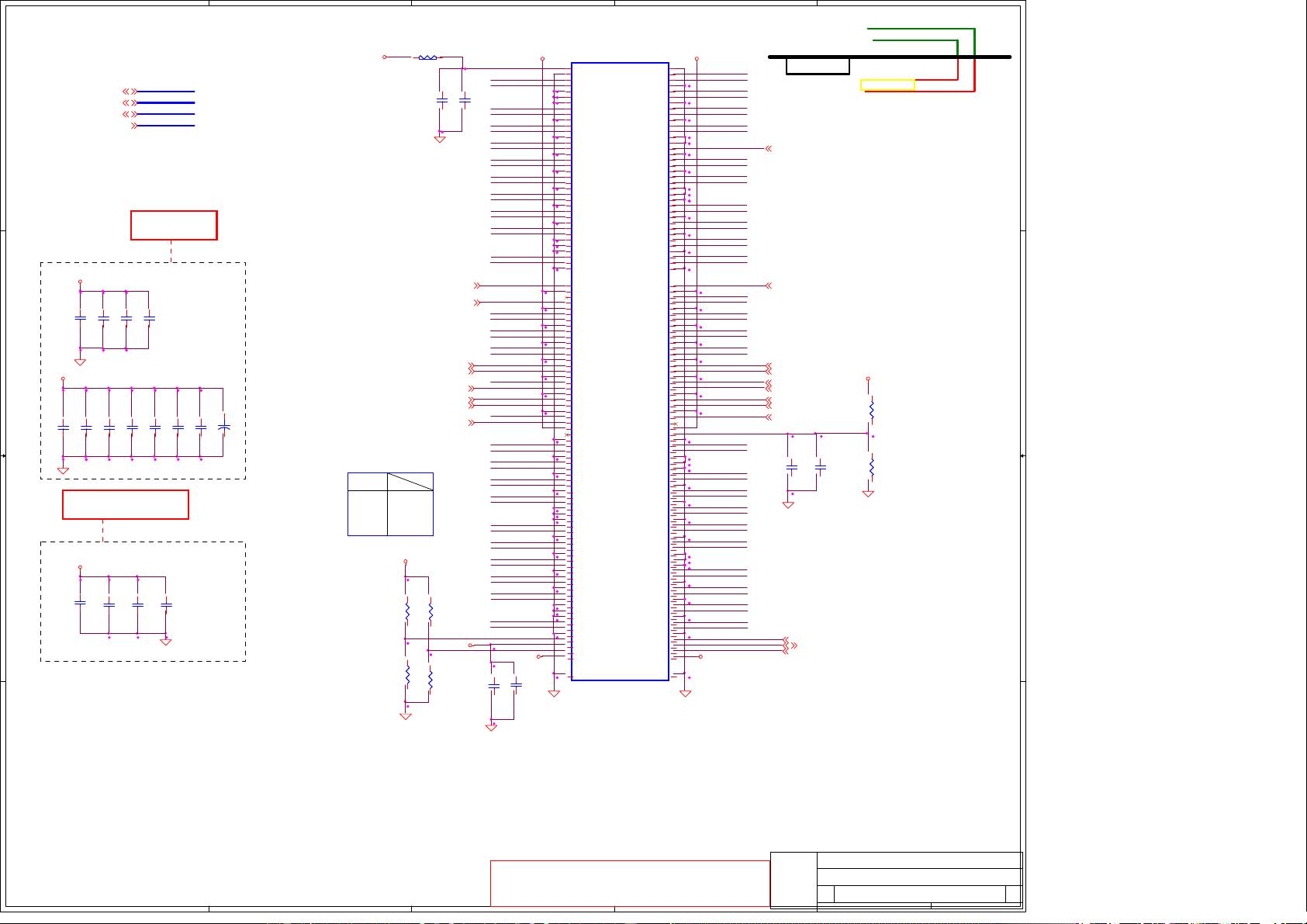

Layout Note:

Place near JDIMM1

Layout Note:

Place near JDIMM1.203,204

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWINGS AND SPECIFICATIONS CONTAINS CONFIDENTIAL,

T

RADE SECRET, AND OTHER PROPRIETARY INFORMATION

OF DELL. ("DELL"). THIS DOCUMENT MAY NOT BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN

AUTHORIZATION OF DELL. IN ADDITION, NEITHER THIS

SHEET NOR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT

DELL'S EXPRESS WRITTEN CONSENT.

DELL CONFIDENTIAL/PROPRIETARY

Link Done

1

0

0

SA0

SA1

1

1

DIMM2

DIMM3

DIMM4

0

0

1

DIMM1

JDIMM2 (H8)A6

JDIMM1 (H4)A2

JDIMM3 (H5.2)A0

CPU

JDIMM4 (H9.2)A4

+DIMM3_VREF

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D10

DDR_A_D11

DDR_A_D18

DDR_A_D19

DDR_A_D21

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D32

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D45

DDR_A_D46

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_MA2

DDR_A_MA1

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

PCH_SMBDATA

PCH_SMBCLK

DDR_A_MA15

+VREF_CC

DDR_A_D23

DDR_A_D31

DDR_A_D17

DDR_A_D9

DDR_A_D13

DDR_A_D20

DDR_A_D16

DDR_A_D25

DDR_A_D30

DDR_A_D24

DDR_A_D14

DDR_A_D15

DDR_A_D12

DDR_A_D22

DDR_A_D39

DDR_A_D54

DDR_A_D33

DDR_A_D38

DDR_A_D47

DDR_A_D44

DDR_A_D48

DDR3_DRAMRST#

DDR_A_MA0

DDR_A_D63

DDR_CS0_DIMMA#

M_CLK_DDR1

M_CLK_DDR#1

DDR_CKE1_DIMMA

M_ODT0

M_ODT1

DDR_CS1_DIMMA#

M_CLK_DDR0

M_CLK_DDR#0

DDR_CKE0_DIMMA

M_THERMAL#

+0.75VS

+1.5V

+1.5V

+1.5V

+3VS

+0.75VS

+0.75VS

+1.5V

+V_DDR_REFA

+1.5V

+3VS

DDR_A_DQS#[0..7]6,11

DDR_A_DQS[0..7]6,11

DDR_A_D[0..63]6,11

DDR_A_MA[0..15]6,11

DDR_CKE0_DIMMA6

DDR_A_BS26,11

M_CLK_DDR06

M_CLK_DDR#06

DDR_A_WE#6,11

DDR_A_CAS#6,11

DDR_A_BS06,11

DDR_CS1_DIMMA#6

PCH_SMBDATA 5,11,12,14,17,37,38,39

PCH_SMBCLK 5,11,12,14,17,37,38,39

M_THERMAL# 11,12,14,47

DDR3_DRAMRST# 6,11,12,14

DDR_CKE1_DIMMA 6

M_CLK_DDR1 6

M_CLK_DDR#1 6

DDR_A_BS1 6,11

DDR_A_RAS# 6,11

DDR_CS0_DIMMA# 6

M_ODT0 6

M_ODT1 6

Title

S

i

ze Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMC

14 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMC

14 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMC

14 71Friday, March 02, 2012

Compal Electronics, Inc.

RD28 0_0402_5%~D@

RD28 0_0402_5%~D@

1

2

RD33

10K_0402_5%~D

RD33

10K_0402_5%~D

1

2

CD62

10U_0603_6.3V6M~D

CD62

10U_0603_6.3V6M~D

1

2

CD60

10U_0603_6.3V6M~D

CD60

10U_0603_6.3V6M~D

1

2

CD66

0.1U_0402_16V4Z~D

CD66

0.1U_0402_16V4Z~D

1

2

CD53

1U_0402_6.3V6K~D

CD53

1U_0402_6.3V6K~D

1

2

RD40

10K_0402_5%~D

RD40

10K_0402_5%~D

1

2

CD59

10U_0603_6.3V6M~D

CD59

10U_0603_6.3V6M~D

1

2

CD58

10U_0603_6.3V6M~D

CD58

10U_0603_6.3V6M~D

1

2

CD63

10U_0603_6.3V6M~D

@

CD63

10U_0603_6.3V6M~D

@

1

2

CD57

10U_0603_6.3V6M~D

CD57

10U_0603_6.3V6M~D

1

2

CD65

2.2U_0603_6.3V6K~D

CD65

2.2U_0603_6.3V6K~D

1

2

CD70

1U_0402_6.3V6K~D

CD70

1U_0402_6.3V6K~D

1

2

CD52

0.1U_0402_16V4Z~D

CD52

0.1U_0402_16V4Z~D

1

2

CD69

1U_0402_6.3V6K~D

CD69

1U_0402_6.3V6K~D

1

2

CD68

1U_0402_6.3V6K~D

CD68

1U_0402_6.3V6K~D

1

2

RD39

10K_0402_5%~D

@

RD39

10K_0402_5%~D

@

1

2

+

CD64

330U_SX_2VY~D

+

CD64

330U_SX_2VY~D

1

2

CD56

1U_0402_6.3V6K~D

CD56

1U_0402_6.3V6K~D

1

2

CD55

1U_0402_6.3V6K~D

CD55

1U_0402_6.3V6K~D

1

2

CD54

1U_0402_6.3V6K~D

CD54

1U_0402_6.3V6K~D

1

2

CD51

2.2U_0603_6.3V6K~D

CD51

2.2U_0603_6.3V6K~D

1

2

RD32

10K_0402_5%~D

@

RD32

10K_0402_5%~D

@

1

2

CD71

0.1U_0402_16V4Z~D

CD71

0.1U_0402_16V4Z~D

1

2

RD31

1K_0402_1%~D

RD31

1K_0402_1%~D

1

2

CD72

2.2U_0603_6.3V6K~D

CD72

2.2U_0603_6.3V6K~D

1

2

CD67

1U_0402_6.3V6K~D

CD67

1U_0402_6.3V6K~D

1

2

JDIMM3

TYCO_2-2013289-1

JDIMM3

TYCO_2-2013289-1

VREF_DQ

1

VSS

3

DQ0

5

DQ1

7

VSS

9

DM0

11

VSS

13

DQ2

15

DQ3

17

VSS

19

DQ8

21

DQ9

23

VSS

25

DQS1#

27

DQS1

29

VSS

31

DQ10

33

DQ11

35

VSS

37

DQ16

39

DQ17

41

VSS

43

DQS2#

45

DQS2

47

VSS

49

DQ18

51

DQ19

53

VSS

55

DQ24

57

DQ25

59

VSS

61

DM3

63

VSS

65

DQ26

67

DQ27

69

VSS

71

CKE0

73

VDD

75

NC

77

BA2

79

VDD

81

A12/BC#

83

A9

85

VDD

87

A8

89

A5

91

VDD

93

A3

95

A1

97

VDD

99

CK0

101

CK0#

103

VDD

105

A10/AP

107

BA0

109

VDD

111

WE#

113

CAS#

115

VDD

117

A13

119

S1#

121

VDD

123

TEST

125

VSS

127

DQ32

129

DQ33

131

VSS

133

DQS4#

135

DQS4

137

VSS

139

DQ34

141

DQ35

143

VSS

2

DQ4

4

DQ5

6

VSS

8

DQS0#

10

DQS0

12

VSS

14

DQ6

16

DQ7

18

VSS

20

DQ12

22

DQ13

24

VSS

26

DM1

28

RESET#

30

VSS

32

DQ14

34

DQ15

36

VSS

38

DQ20

40

DQ21

42

VSS

44

DM2

46

VSS

48

DQ22

50

DQ23

52

VSS

54

DQ28

56

DQ29

58

VSS

60

DQS3#

62

DQS3

64

VSS

66

DQ30

68

DQ31

70

VSS

72

CKE1

74

VDD

76

A15

78

A14

80

VDD

82

A11

84

A7

86

VDD

88

A6

90

A4

92

VDD

94

A2

96

A0

98

VDD

100

CK1

102

CK1#

104

VDD

106

BA1

108

RAS#

110

VDD

112

S0#

114

ODT0

116

VDD

118

ODT1

120

NC

122

VDD

124

VREF_CA

126

VSS

128

DQ36

130

DQ37

132

VSS

134

DM4

136

VSS

138

DQ38

140

DQ39

142

VSS

144

VSS

145

DQ40

147

DQ41

149

VSS

151

DM5

153

VSS

155

DQ42

157

DQ43

159

VSS

161

DQ48

163

DQ49

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SA0

197

VDDSPD

199

DQ44

146

DQ45

148

VSS

150

DQS5#

152

DQS5

154

VSS

156

DQ46

158

DQ47

160

VSS

162

DQ52

164

DQ53

166

VSS

168

DM6

170

VSS

172

DQ54

174

DQ55

176

VSS

178

DQ60

180

DQ61

182

VSS

184

DQS7#

186

DQS7

188

VSS

190

DQ62

192

DQ63

194

VSS

196

EVENT#

198

SDA

200

SA1

201

SCL

202

VTT

203

VTT

204

GND1

205

GND2

206

CD61

10U_0603_6.3V6M~D

CD61

10U_0603_6.3V6M~D

1

2

RD30

1K_0402_1%~D

RD30

1K_0402_1%~D

1

2

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

Layout Note:

Place near JDIMM4.203,204

Note:

Check voltage tolerance of

VREF_DQ at the DIMM socket

Layout Note:

Place near JDIMMB

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWINGS AND SPECIFICATIONS CONTAINS CONFIDENTIAL,

T

RADE SECRET, AND OTHER PROPRIETARY INFORMATION

OF DELL. ("DELL"). THIS DOCUMENT MAY NOT BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN

AUTHORIZATION OF DELL. IN ADDITION, NEITHER THIS

SHEET NOR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT

DELL'S EXPRESS WRITTEN CONSENT.

Link Done

1

0

0

SA0

SA1

1

1

DIMM2

DIMM3

DIMM4

0

0

1

DIMM1

JDIMM2 (H8)A6

JDIMM1 (H4)A2

JDIMM3 (H5.2)A0

CPU

JDIMM4 (H9.2)A4

DDR_B_MA7

DDR_B_D22

DDR_B_D20

DDR_B_D52

DDR_B_MA14

DDR_B_D27

DDR3_DRAMRST#

DDR_B_D37

DDR_B_D36

DDR_B_MA6

DDR_B_D23

DDR_B_D21

DDR_B_D44

DDR_B_DQS#3

DDR_B_D54

DDR_B_D53

DDR_B_D46

DDR_B_D14

DDR_B_MA4

DDR_B_D45

DDR_B_D38

DDR_B_BS1

DDR_B_DQS3

DDR_B_D7

DDR_B_D6

DDR_B_D55

DDR_B_D47

DDR_B_D15

DDR_B_D28

DDR_B_RAS#

DDR_B_MA2

DDR_B_D29

DDR_B_DQS#5

DDR_B_MA11

DDR_B_D30

DDR_B_D12

DDR_B_D60

DDR_B_D39

DDR_B_MA0

DDR_B_DQS5

DDR_B_D31

DDR_B_D58

DDR_B_D13

DDR_B_D59

DDR_B_BS2

DDR_B_MA12

DDR_B_MA9

DDR_B_D4

DDR_B_MA8

DDR_B_D5

DDR_B_MA5

DDR_B_DQS#0

DDR_B_MA3

DDR_B_DQS0

DDR_B_MA1

DDR_B_MA10

DDR_B_BS0

DDR_B_WE#

DDR_B_CAS#

DDR_B_MA15

DDR_B_MA13

DDR_B_D0

DDR_B_D1

DDR_B_D32

DDR_B_D33

DDR_B_D2

DDR_B_DQS#4

DDR_B_D3

DDR_B_DQS4

DDR_B_D8

DDR_B_D34

DDR_B_D9

DDR_B_D35

DDR_B_DQS#1

DDR_B_D40

DDR_B_D61

DDR_B_DQS1

DDR_B_D41

DDR_B_DQS#7

DDR_B_D10

DDR_B_DQS7

DDR_B_D11

PCH_SMBDATA

PCH_SMBCLK

DDR_B_D42

DDR_B_D62

DDR_B_D16

DDR_B_D43

DDR_B_D63

DDR_B_D17

DDR_B_D48

DDR_B_DQS#2

DDR_B_D49

DDR_B_DQS2

+VREF_CD

DDR_B_DQS#6

DDR_B_D18

DDR_B_DQS6

DDR_B_D19

DDR_B_D50

DDR_B_D24

DDR_B_D51

DDR_B_D25

DDR_B_D56

DDR_B_D57

DDR_B_D26

+DIMM4_VREF

M_ODT2

DDR_CKE3_DIMMB

M_ODT3

M_CLK_DDR3

M_CLK_DDR#3

DDR_CS2_DIMMB#

M_CLK_DDR2

M_CLK_DDR#2

DDR_CS3_DIMMB#

DDR_CKE2_DIMMB

M_THERMAL#

+1.5V

+0.75VS

+1.5V

+0.75VS

+1.5V

+1.5V

+0.75VS

+V_DDR_REFB

+1.5V

+3VS

+3VS

DDR_B_DQS#[0..7]6,12

DDR_B_DQS[0..7]6,12

DDR_B_D[0..63]6,12

DDR_B_MA[0..15]6,12

DDR_CKE2_DIMMB6

DDR_B_BS26,12

M_CLK_DDR26

M_CLK_DDR#26

DDR_B_BS06,12

DDR_B_WE#6,12

DDR_B_CAS#6,12

DDR_CS3_DIMMB#6

PCH_SMBDATA 5,11,12,13,17,37,38,39

PCH_SMBCLK 5,11,12,13,17,37,38,39

M_THERMAL# 11,12,13,47

DDR3_DRAMRST# 6,11,12,13

DDR_CKE3_DIMMB 6

M_CLK_DDR3 6

M_CLK_DDR#3 6

DDR_B_BS1 6,12

DDR_B_RAS# 6,12

DDR_CS2_DIMMB# 6

M_ODT2 6

M_ODT3 6

Title

S

i

ze Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMD

15 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMD

15 71Friday, March 02, 2012

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

LA-8341P

1.0

DDRIII DIMMD

15 71Friday, March 02, 2012

Compal Electronics, Inc.

CD92

1U_0402_6.3V6K~D

CD92

1U_0402_6.3V6K~D

1

2

JDIMM4

TYCO_2-2013310-1

JDIMM4

TYCO_2-2013310-1

VREF_DQ

1

VSS

3

DQ0

5

DQ1

7

VSS

9

DM0

11

VSS

13

DQ2

15

DQ3

17

VSS

19

DQ8

21

DQ9

23

VSS

25

DQS1#

27

DQS1

29

VSS

31

DQ10

33

DQ11

35

VSS

37

DQ16

39

DQ17

41

VSS

43

DQS2#

45

DQS2

47

VSS

49

DQ18

51

DQ19

53

VSS

55

DQ24

57

DQ25

59

VSS

61

DM3

63

VSS

65

DQ26

67

DQ27

69

VSS

71

CKE0

73

VDD

75

NC

77

BA2

79

VDD

81

A12/BC#

83

A9

85

VDD

87

A8

89

A5

91

VDD

93

A3

95

A1

97

VDD

99

CK0

101

CK0#

103

VDD

105

A10/AP

107

BA0

109

VDD

111

WE#

113

CAS#

115

VDD

117

A13

119

S1#

121

VDD

123

TEST

125

VSS

127

DQ32

129

DQ33

131

VSS

133

DQS4#

135

DQS4

137

VSS

139

DQ34

141

DQ35

143

VSS

2

DQ4

4

DQ5

6

VSS

8

DQS0#

10

DQS0

12

VSS

14

DQ6

16

DQ7

18

VSS

20

DQ12

22

DQ13

24

VSS

26

DM1

28

RESET#

30

VSS

32

DQ14

34

DQ15

36

VSS

38

DQ20

40

DQ21

42

VSS

44

DM2

46

VSS

48

DQ22

50

DQ23

52

VSS

54

DQ28

56

DQ29

58

VSS

60

DQS3#

62

DQS3

64

VSS

66

DQ30

68

DQ31

70

VSS

72

CKE1

74

VDD

76

A15

78

A14

80

VDD

82

A11

84

A7

86

VDD

88

A6

90

A4

92

VDD

94

A2

96

A0

98

VDD

100

CK1

102

CK1#

104

VDD

106

BA1

108

RAS#

110

VDD

112

S0#

114

ODT0

116

VDD

118

ODT1

120

NC

122

VDD

124

VREF_CA

126

VSS

128

DQ36

130

DQ37

132

VSS

134

DM4

136

VSS

138

DQ38

140

DQ39

142

VSS

144

VSS

145

DQ40

147

DQ41

149

VSS

151

DM5

153

VSS

155

DQ42

157

DQ43

159

VSS

161

DQ48

163

DQ49

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SA0

197

VDDSPD

199

DQ44

146

DQ45

148

VSS

150

DQS5#

152

DQS5

154

VSS

156

DQ46

158

DQ47

160

VSS

162

DQ52

164

DQ53

166

VSS

168

DM6

170

VSS

172

DQ54

174

DQ55

176

VSS

178

DQ60

180

DQ61

182

VSS

184

DQS7#

186

DQS7

188

VSS

190

DQ62

192

DQ63

194

VSS

196

EVENT#

198

SDA

200

SA1

201

SCL

202

VTT

203

VTT

204

GND1

205

GND2

206

CD78

1U_0402_6.3V6K~D

CD78

1U_0402_6.3V6K~D

1

2

CD97

2.2U_0603_6.3V6K~D

CD97

2.2U_0603_6.3V6K~D

1

2

RD44

1K_0402_1%~D

RD44

1K_0402_1%~D

1

2

RD45

1K_0402_1%~D

RD45

1K_0402_1%~D

1

2

RD41 0_0402_5%~D@

RD41 0_0402_5%~D@

1

2

CD95

1U_0402_6.3V6K~D

CD95

1U_0402_6.3V6K~D

1

2

CD94

1U_0402_6.3V6K~D

CD94

1U_0402_6.3V6K~D

1

2

CD93

1U_0402_6.3V6K~D

CD93

1U_0402_6.3V6K~D

1

2

RD49

10K_0402_5%~D

@

RD49

10K_0402_5%~D

@

1

2

CD91

0.1U_0402_16V4Z~D

CD91

0.1U_0402_16V4Z~D

1

2

CD90

2.2U_0603_6.3V6K~D

CD90

2.2U_0603_6.3V6K~D

1

2

RD46

10K_0402_5%~D

@

RD46

10K_0402_5%~D

@

1

2

CD77

0.1U_0402_16V4Z~D

CD77

0.1U_0402_16V4Z~D

1

2

CD88

10U_0603_6.3V6M~D

@

CD88

10U_0603_6.3V6M~D

@

1

2

CD81

1U_0402_6.3V6K~D

CD81

1U_0402_6.3V6K~D

1

2

CD87

10U_0603_6.3V6M~D

CD87

10U_0603_6.3V6M~D

1

2

CD80

1U_0402_6.3V6K~D

CD80

1U_0402_6.3V6K~D

1

2

CD86

10U_0603_6.3V6M~D

CD86

10U_0603_6.3V6M~D

1

2

CD79

1U_0402_6.3V6K~D

CD79

1U_0402_6.3V6K~D

1

2

RD48

10K_0402_5%~D

RD48

10K_0402_5%~D

1

2

CD85

10U_0603_6.3V6M~D

CD85

10U_0603_6.3V6M~D

1

2

CD76

2.2U_0603_6.3V6K~D

CD76

2.2U_0603_6.3V6K~D

1

2

CD84

10U_0603_6.3V6M~D

CD84

10U_0603_6.3V6M~D

1

2

CD83

10U_0603_6.3V6M~D

CD83

10U_0603_6.3V6M~D

1

2

CD82

10U_0603_6.3V6M~D

CD82

10U_0603_6.3V6M~D

1

2

CD96

0.1U_0402_16V4Z~D

CD96

0.1U_0402_16V4Z~D

1

2

RD50

10K_0402_5%~D

RD50

10K_0402_5%~D

1

2

+

CD89

330U_SX_2VY~D

+

CD89

330U_SX_2VY~D

1

2

剩余70页未读,继续阅读

2012-12-03 上传

2021-06-07 上传

2021-04-03 上传

2021-04-30 上传

2021-03-10 上传

790611luo

- 粉丝: 1

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功