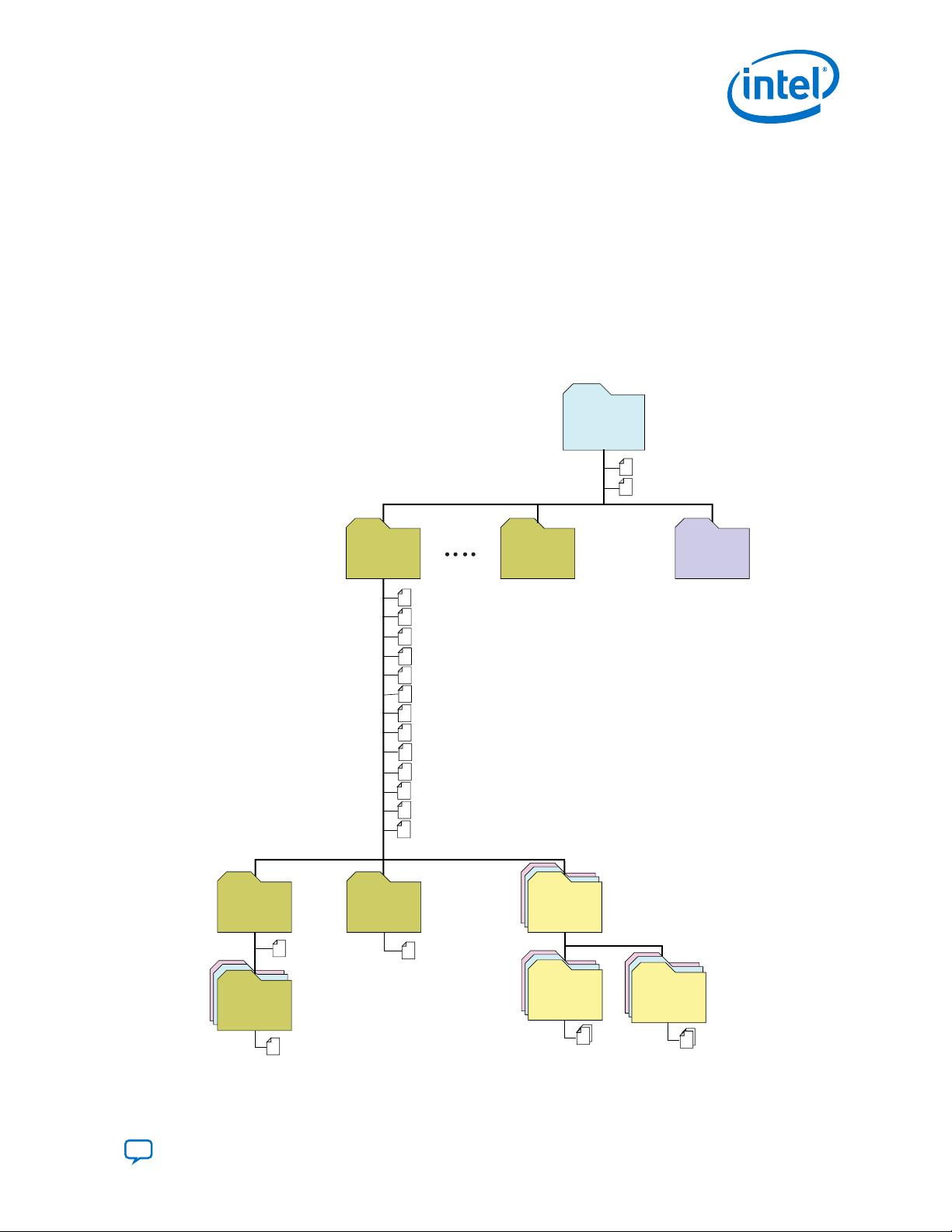

"该文档是25G Ethernet Intel Arria 10 FPGA IP核心的用户指南,用于指导用户如何在Intel Quartus Prime Design Suite 19.4版本中使用此高性能以太网解决方案。该IP核心支持25Gbps速率,并详细介绍了其特性、设备家族与速度等级支持、验证方法、性能和资源利用率,以及如何开始使用和集成到设计中。" 本文档主要涵盖以下几个关键知识点: 1. **25G Ethernet Intel FPGA IP Core**: 这是一个专为Intel Arria 10 FPGA设计的25千兆以太网接口IP核心,旨在提供高速数据传输能力,适用于数据中心、网络通信等应用。 2. **支持特性**: 25G Ethernet IP核心具备多种功能,包括但不限于符合IEEE 802.3by标准的25 Gigabit Ethernet协议支持、流控制、错误检测和校正机制等。 3. **设备家族和速度等级支持**: 支持Intel Arria 10系列的不同设备家族,且详细列出了各个设备的速度等级,以满足不同应用环境和性能需求。 4. **IP Core验证**: 验证过程包括模拟环境的设置、编译检查和硬件测试,确保IP核心在实际应用中的正确性和可靠性。 5. **性能和资源利用率**: 文档中会提供IP核心在实现25Gbps以太网功能时对FPGA资源的占用情况,包括逻辑元件、内存块和I/O引脚等,帮助用户评估设计的效率和可行性。 6. **开始使用**: 包含安装和授权Intel FPGA IP核心的步骤,以及如何配置IP核心参数和选项,便于用户快速上手。 7. **模拟IP Core**: 用户可以通过仿真工具验证IP核心的功能,确保设计在硬件实现前满足预期。 8. **生成文件结构**: 描述了在设计流程中生成的各类文件及其用途,帮助用户理解设计输出。 9. **设计集成**: 提供了关于引脚分配、添加收发器PLL(锁相环)以及处理可能的抖动问题的指导,确保IP核心能无缝融入用户的设计。 10. **处理潜在抖动**: 在Intel Arria 10器件中,可能会遇到信号质量问题,如抖动,文档提供了相应的处理策略,以维持高数据传输的稳定性。 这份用户指南是针对开发人员和工程师的宝贵参考资料,它详细阐述了如何在Intel Arria 10 FPGA平台上实现和优化25G Ethernet功能,对于那些寻求高速网络连接解决方案的人来说至关重要。

剩余90页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- OptiX传输试题与SDH基础知识

- C++Builder函数详解与应用

- Linux shell (bash) 文件与字符串比较运算符详解

- Adam Gawne-Cain解读英文版WKT格式与常见投影标准

- dos命令详解:基础操作与网络测试必备

- Windows 蓝屏代码解析与处理指南

- PSoC CY8C24533在电动自行车控制器设计中的应用

- PHP整合FCKeditor网页编辑器教程

- Java Swing计算器源码示例:初学者入门教程

- Eclipse平台上的可视化开发:使用VEP与SWT

- 软件工程CASE工具实践指南

- AIX LVM详解:网络存储架构与管理

- 递归算法解析:文件系统、XML与树图

- 使用Struts2与MySQL构建Web登录验证教程

- PHP5 CLI模式:用PHP编写Shell脚本教程

- MyBatis与Spring完美整合:1.0.0-RC3详解

信息提交成功

信息提交成功