"Verilog HDL基础: 硬件描述语言概念与4位寄存器设计示例"

需积分: 10 175 浏览量

更新于2024-01-14

收藏 8.85MB PPT 举报

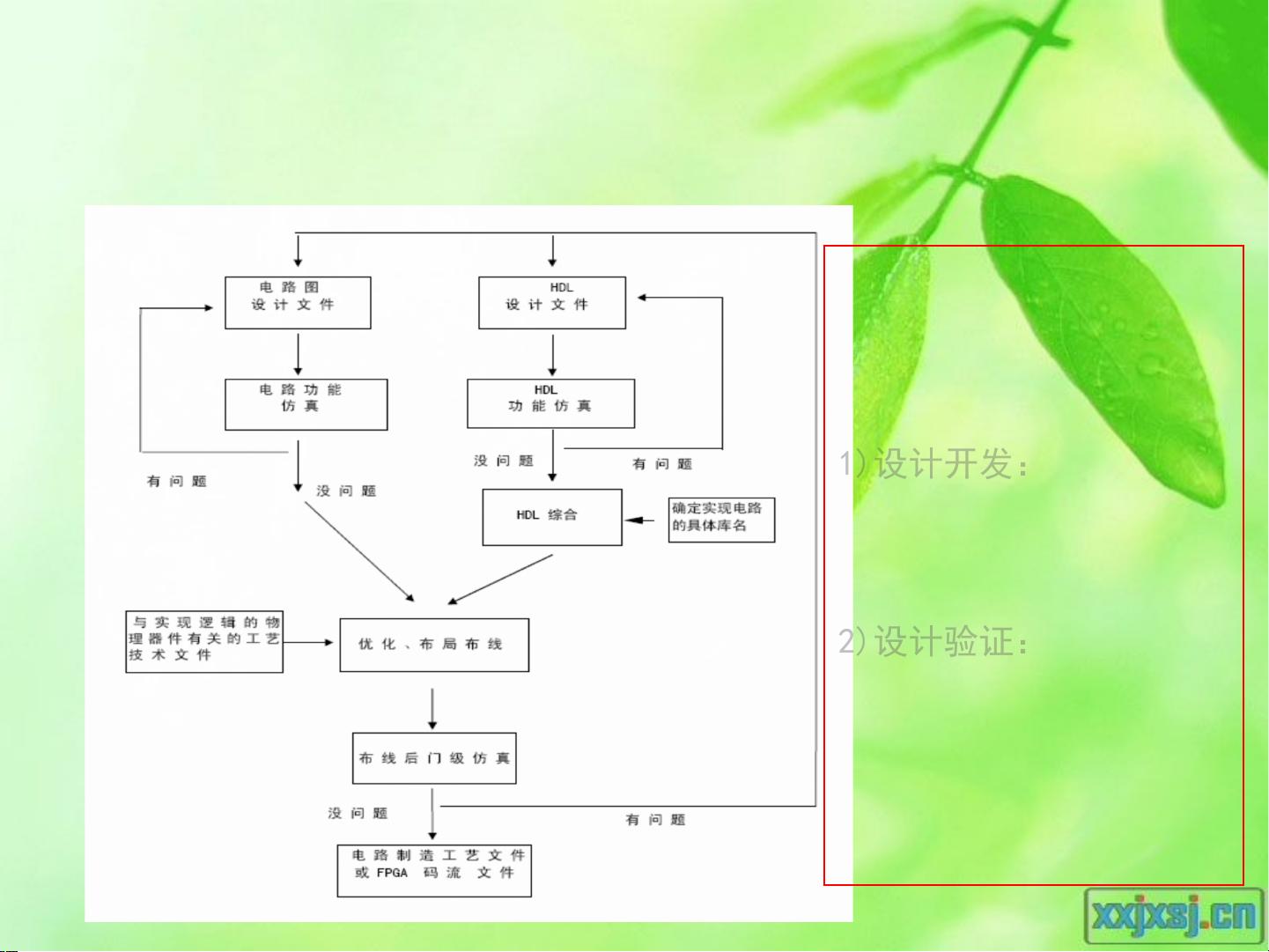

本段描述了硬件描述语言Verilog HDL基础的内容。Verilog HDL是一种硬件描述语言,它可以用于建立电子系统的行为级仿真模型,以及编写设计文件,是硬件设计人员和电子设计自动化工具之间的接口。硬件描述语言利用计算机的巨大能力对复杂的数字逻辑进行仿真,并且自动综合生成符合要求的数字逻辑网表,最终生成具体电路的延时模型。然后,经过验证无误后,可以用于制造ASIC芯片,或者写入CPLD和FPGA器件中。

硬件描述语言是一种能够对硬件逻辑电路的功能进行描述的高级编程语言,具有特殊的结构来描述电路的连接、功能、不同抽象级上描述电路、电路的时序以及具有并行性。Verilog和VHDL是两种主要的HDL,Verilog起源于C语言,因此非常类似于C语言,容易掌握,而VHDL则格式严谨。同时,VHDL出现较晚,但标准。

在硬件描述语言基础部分,并介绍了Verilog的基本概念以及硬件描述语言HDL。硬件描述语言利用计算机的巨大能力对用HDL建模的复杂数字逻辑进行仿真,然后再自动综合以生成符合要求且在电路结构上可以实现的数字逻辑网表,根据网表和某种工艺的器件自动生成具体电路然后生成该工艺条件下这种具体电路的延时模型。仿真验证无误后用于制造ASIC芯片或写入CPLD和FPGA器件中。

本段中还给出了一个具体的Verilog HDL代码示例,该代码示例用触发器组成带清零端的4位寄存器。其中,将包含模块" flop.v ”的代码引入当前模块,然后定义了硬件寄存器的输入输出,以及使用flop模块构建了4个触发器f1、f2、f3、f4,来实现寄存器的存储功能。这个具体的Verilog HDL代码示例在说明硬件描述语言的基础知识的同时,也帮助读者理解了实际应用的场景和方式。

总之,硬件描述语言Verilog HDL基础的内容主要包括了硬件描述语言HDL的基本概念、Verilog HDL的特点和基本语法,以及一个具体的Verilog HDL代码示例。这些内容为读者提供了对硬件描述语言的全面认识,并且通过实际的代码示例帮助读者更好地理解了硬件描述语言的具体应用。

2018-01-20 上传

2022-09-23 上传

2019-11-21 上传

2021-10-04 上传

2022-09-23 上传

111 浏览量

2022-09-14 上传

四方怪

- 粉丝: 28

- 资源: 2万+

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章