VerilogHDL建模基础与技巧探索

需积分: 9 162 浏览量

更新于2024-07-22

收藏 8.55MB PDF 举报

"Verilog HDL那些事建模篇" 是一篇针对初学者的教程,由黑金动力社区荣誉出品,旨在帮助学习者理解和掌握Verilog HDL中的建模概念,以及如何有效地运用这一工具进行FPGA设计。

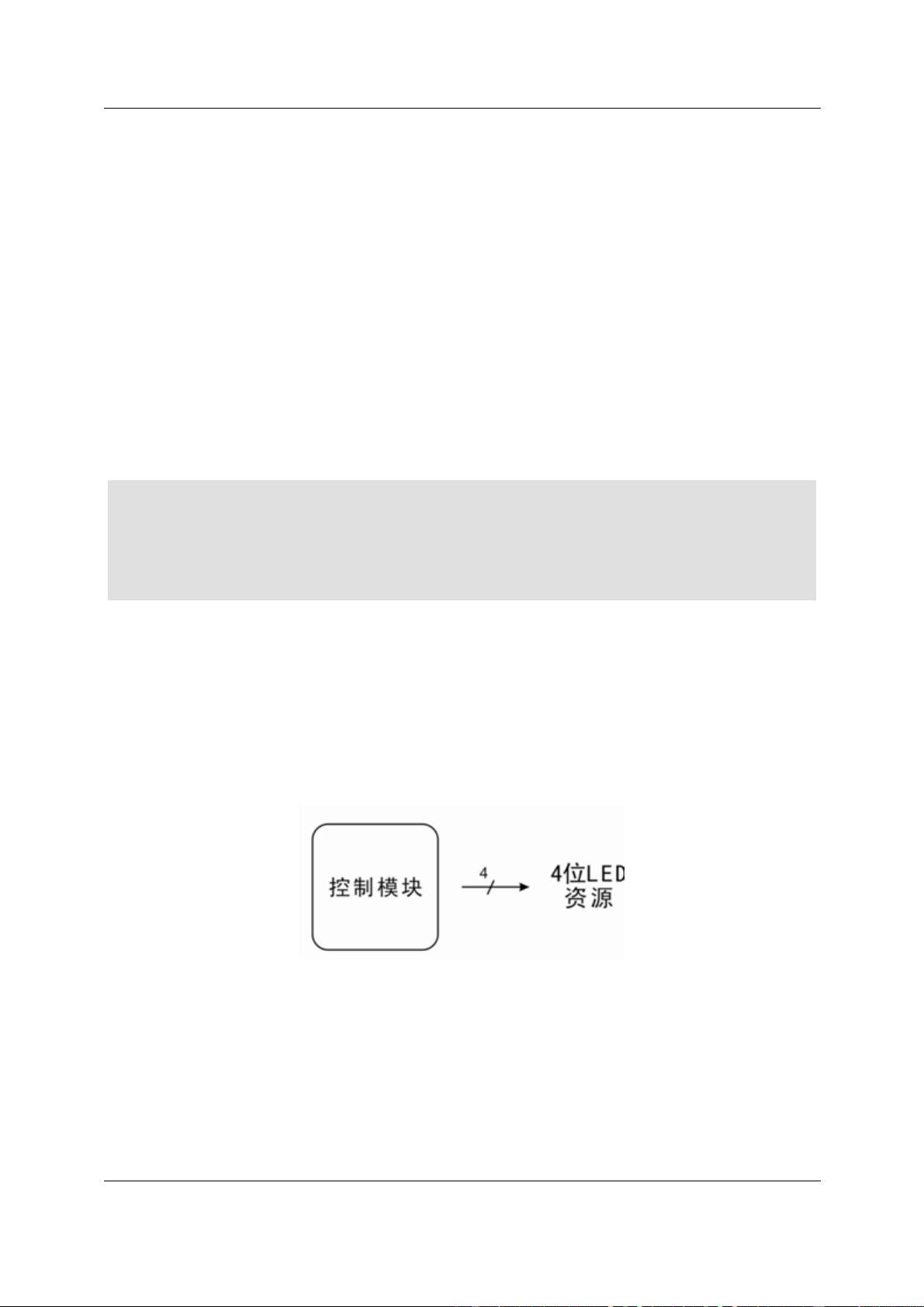

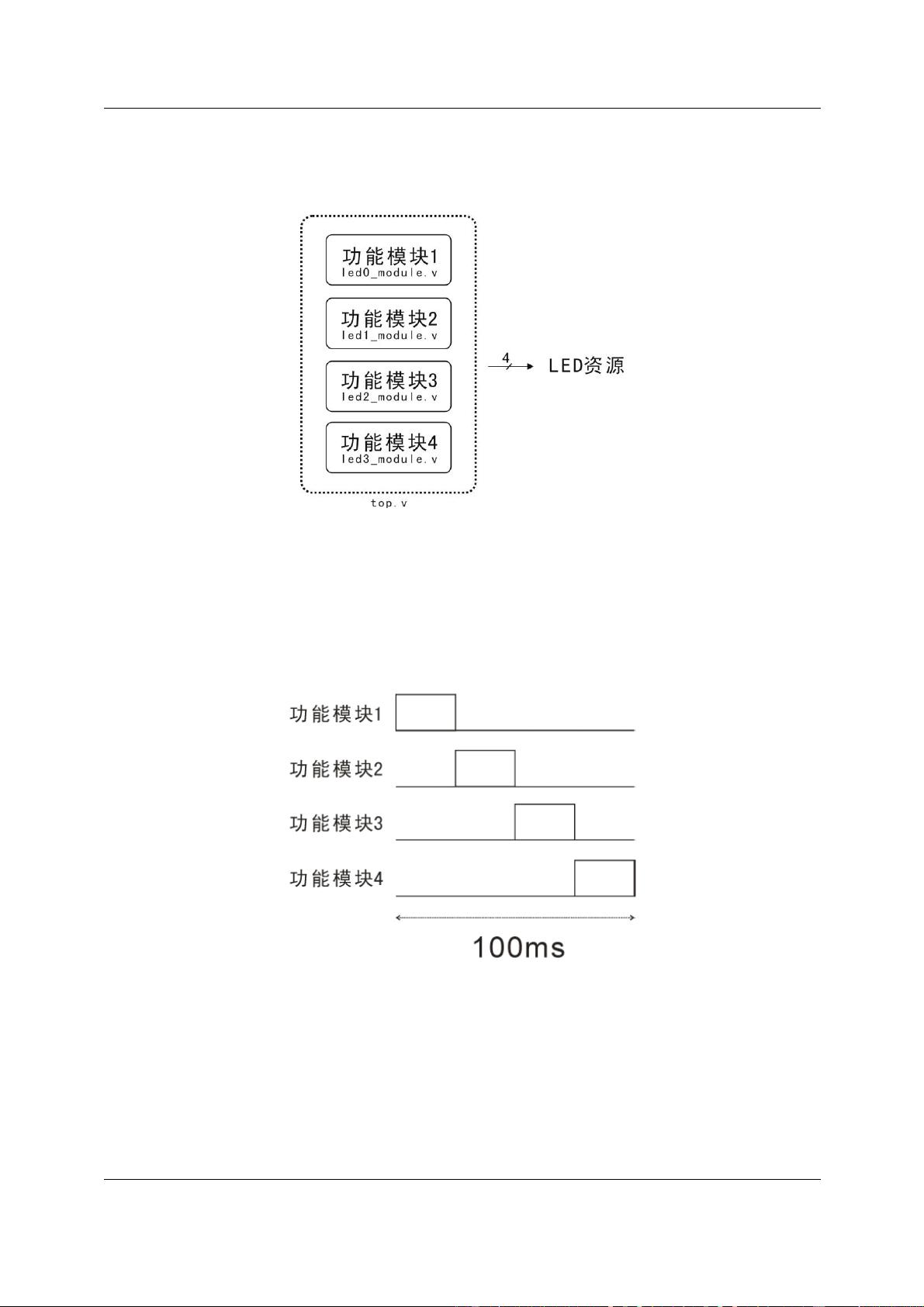

Verilog HDL是一种硬件描述语言,广泛用于FPGA(Field Programmable Gate Array)的设计。建模在Verilog HDL中占据了核心地位,它是创建逻辑模块的基础,类似于使用乐高积木构建复杂结构,Verilog HDL则是连接和定义这些积木的工具。然而,许多初学者在学习过程中可能感到困惑,因为缺乏对建模方法的深入理解和实践。

“建模”是指在Verilog HDL中创建逻辑模块的过程,这包括定义模块的输入、输出、内部状态和行为。有效的建模不仅要求清晰理解设计的逻辑功能,还需要良好的编程风格,使得代码易于阅读和维护。建模技巧的重要性在于,它直接影响到设计的可读性、可维护性和效率。

作者指出,很多学习者在面对复杂的源代码时可能会感到无助,甚至想要放弃,这往往是因为缺乏建模技巧。学习Verilog HDL不仅仅是理解RTL(寄存器传输级)代码,更关键的是要能读懂并理解他人设计的意图和实现方式。这需要大量的实践和经验积累,而不仅仅是理论学习。

作者强调,好的Verilog HDL设计应该具备清晰的表达能力,整洁的代码结构,并且遵循一定的建模规范。建模技巧对于提高设计质量和效率至关重要,甚至比时序分析和功能仿真等其他技能更为基础。作者坚信,掌握建模技巧后,Verilog HDL语言在某些方面可以媲美甚至超越其他高级编程语言。

"Verilog HDL那些事建模篇" 提供了对Verilog HDL建模基础的深入探讨,对于那些在FPGA学习之路上感到迷茫的初学者来说,是一份宝贵的参考资料。通过学习和实践建模技巧,可以帮助他们更好地理解Verilog HDL,并提升FPGA设计能力。

2019-03-11 上传

2015-10-16 上传

2013-06-06 上传

2019-07-11 上传

2021-10-04 上传

2018-05-03 上传

2019-09-05 上传

nuaayzy

- 粉丝: 0

- 资源: 1

最新资源

- 天池大数据比赛:伪造人脸图像检测技术

- ADS1118数据手册中英文版合集

- Laravel 4/5包增强Eloquent模型本地化功能

- UCOSII 2.91版成功移植至STM8L平台

- 蓝色细线风格的PPT鱼骨图设计

- 基于Python的抖音舆情数据可视化分析系统

- C语言双人版游戏设计:别踩白块儿

- 创新色彩搭配的PPT鱼骨图设计展示

- SPICE公共代码库:综合资源管理

- 大气蓝灰配色PPT鱼骨图设计技巧

- 绿色风格四原因分析PPT鱼骨图设计

- 恺撒密码:古老而经典的替换加密技术解析

- C语言超市管理系统课程设计详细解析

- 深入分析:黑色因素的PPT鱼骨图应用

- 创新彩色圆点PPT鱼骨图制作与分析

- C语言课程设计:吃逗游戏源码分享