超前进位加法器与时序约束解析:AXI4协议背景下的设计优化

75 浏览量

更新于2024-08-03

收藏 8.3MB DOCX 举报

"本文主要介绍了超前进位加法器、时序约束以及握手信号处理与AXI4协议在IC设计中的应用,特别是FPGA设计的关键技术。内容涵盖四位超前进位加法器的实现,系统时钟约束的步骤,以及时钟延迟约束的设置方法。"

超前进位加法器是数字逻辑电路设计中的一个重要概念,它通过组合逻辑提前计算出每一位的进位,以减少整个加法运算的延迟。相比于传统的加法器,超前进位加法器能够在不增加太多硬件资源的情况下提高电路的工作速度。以四位超前进位加法器为例,其计算逻辑公式和对应的代码实现展示了如何高效地计算进位和和值。

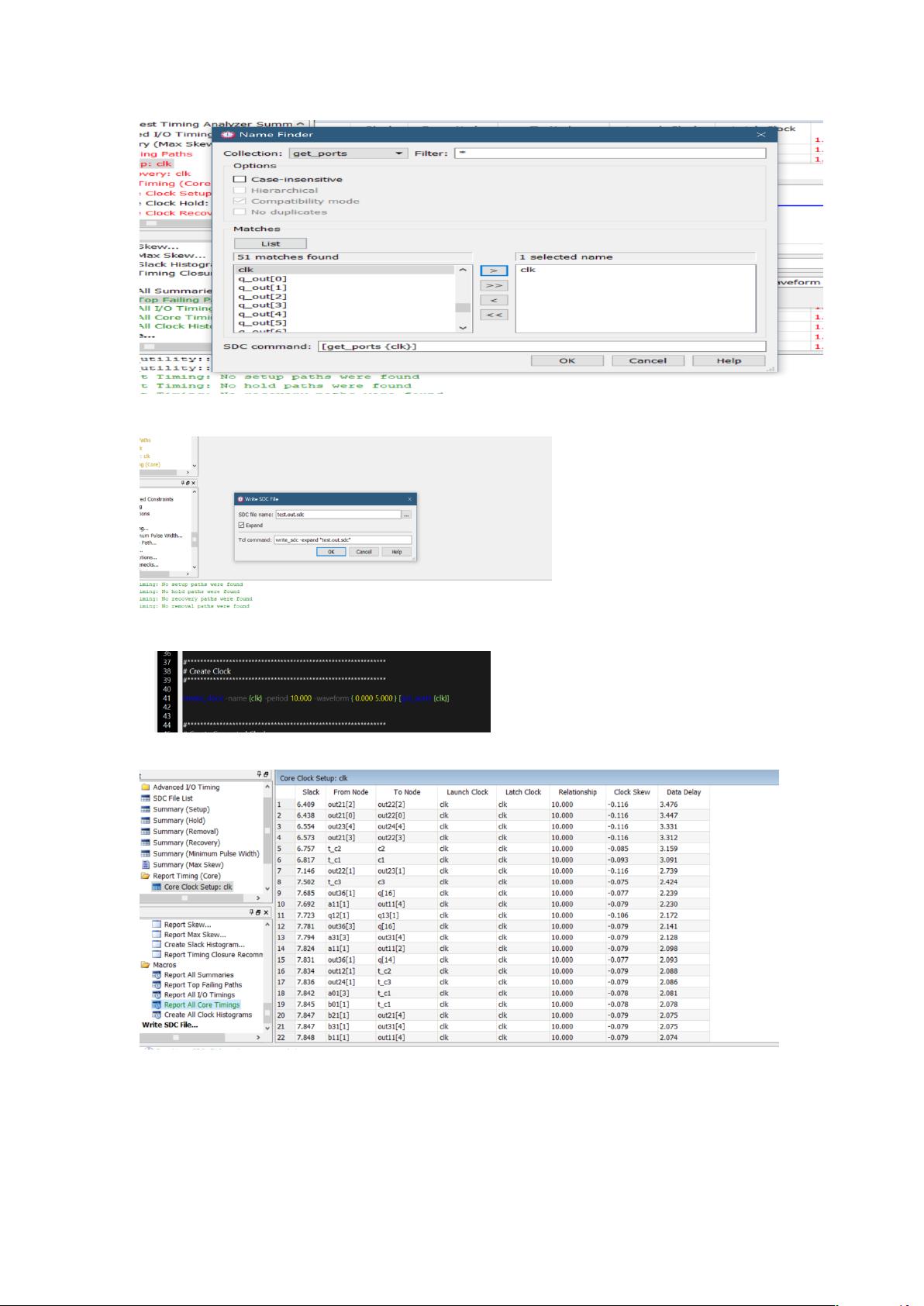

时序约束在FPGA设计中起着至关重要的作用,确保设计满足时钟周期和建立/保持时间要求,从而保证系统的稳定性和可靠性。系统时钟约束通常涉及创建时钟网表、定义时钟周期和占空比,以及约束设计中的时钟。在这个过程中,首先需要对默认的1000MHz时钟进行约束,然后创建和绑定设计所需的时钟,最后更新时序约束文件以避免时序违规。时钟约束还包括对生成时钟的定义,例如通过PLL、分频器等产生的时钟,以及设置时钟延迟,这有助于精确控制时钟在网络中的传播。

时钟延迟约束是另一个关键环节,它允许指定从理想时钟到实际路径的额外延迟,分为时钟源延迟和时钟网络延迟。这种约束对于时序分析至关重要,因为它影响数据到达时间和时钟到达时间的计算,确保数据传输的正确性。

此外,虽然没有直接提及,AXI4协议是高级可扩展接口(Advanced eXtensible Interface)的一种,广泛用于FPGA中的数据通信,特别是在处理器和外设间。AXI4协议定义了数据传输的握手信号处理,确保数据传输的同步和无冲突,同时提供高带宽和低延迟的通信。

这些知识点对于软件工程师,尤其是专注于FPGA和IC设计的工程师来说,是理解和优化硬件系统性能的基础。熟悉超前进位加法器的原理和实现、掌握时序约束的设定方法,以及理解AXI4协议中的握手信号处理,将有助于设计出更加高效和可靠的硬件系统。

182 浏览量

2021-10-01 上传

2023-06-22 上传

2023-07-03 上传

2023-06-19 上传

2023-03-31 上传

2023-04-05 上传

2024-01-24 上传

2023-04-05 上传

芯火平台

- 粉丝: 74

- 资源: 1

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析