Xilinx LogiCORE IP Guide: 1G/2.5G Ethernet PCS/PMA & SGMII v16.1...

需积分: 50 81 浏览量

更新于2024-07-17

5

收藏 5.03MB PDF 举报

本篇文档是Xilinx公司发布的关于1G/2.5G Ethernet PCS/PMA (Physical Coding Sublayer/Physical Medium Attachment) 或者 SGMII (Serializer/Deserializer) v16.1的LogiCORE IP产品指南,适用于Vivado Design Suite。PG047是在2018年11月14日更新的,主要内容涵盖了1G/2.5G Ethernet技术在设计过程中的应用、产品特性、设计原则、流程步骤以及特定设计注意事项。

**章节1:概述**

本章首先介绍了产品的主要应用场景,可能包括网络设备、路由器、交换机等需要高速以太网接口的领域。推荐的设计经验包括对高速数字信号处理和时钟管理有深入理解。同时,章节详细说明了许可证和订购信息,确保用户了解使用此IP核的相关条款。

**章节2:产品规格**

- **标准支持**:该核心兼容1G和2.5G以太网标准,如1000BASE-T(铜线)、1000BASE-LX/SX(光纤)和2500BASE-X(光纤)。此外,还可能支持SGMII规范。

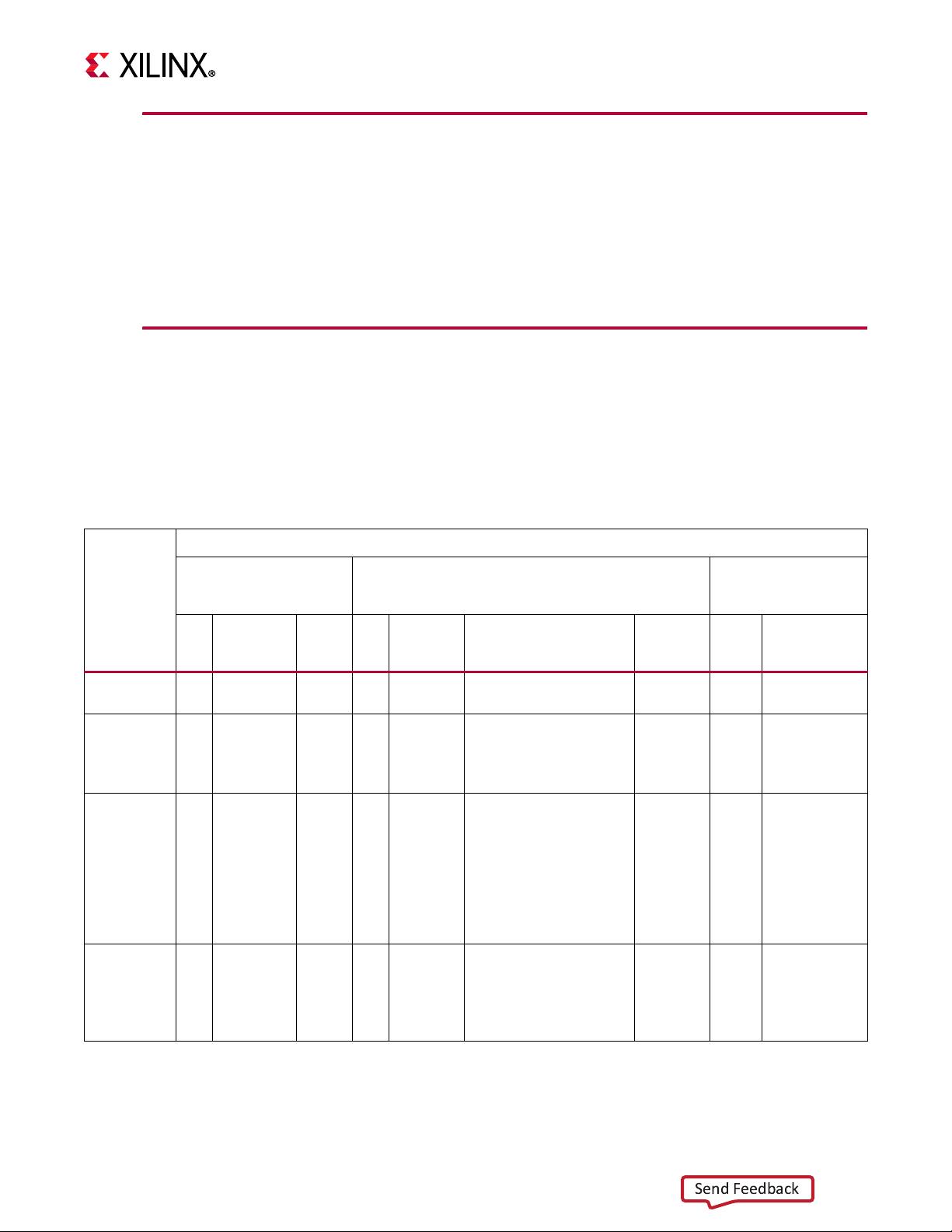

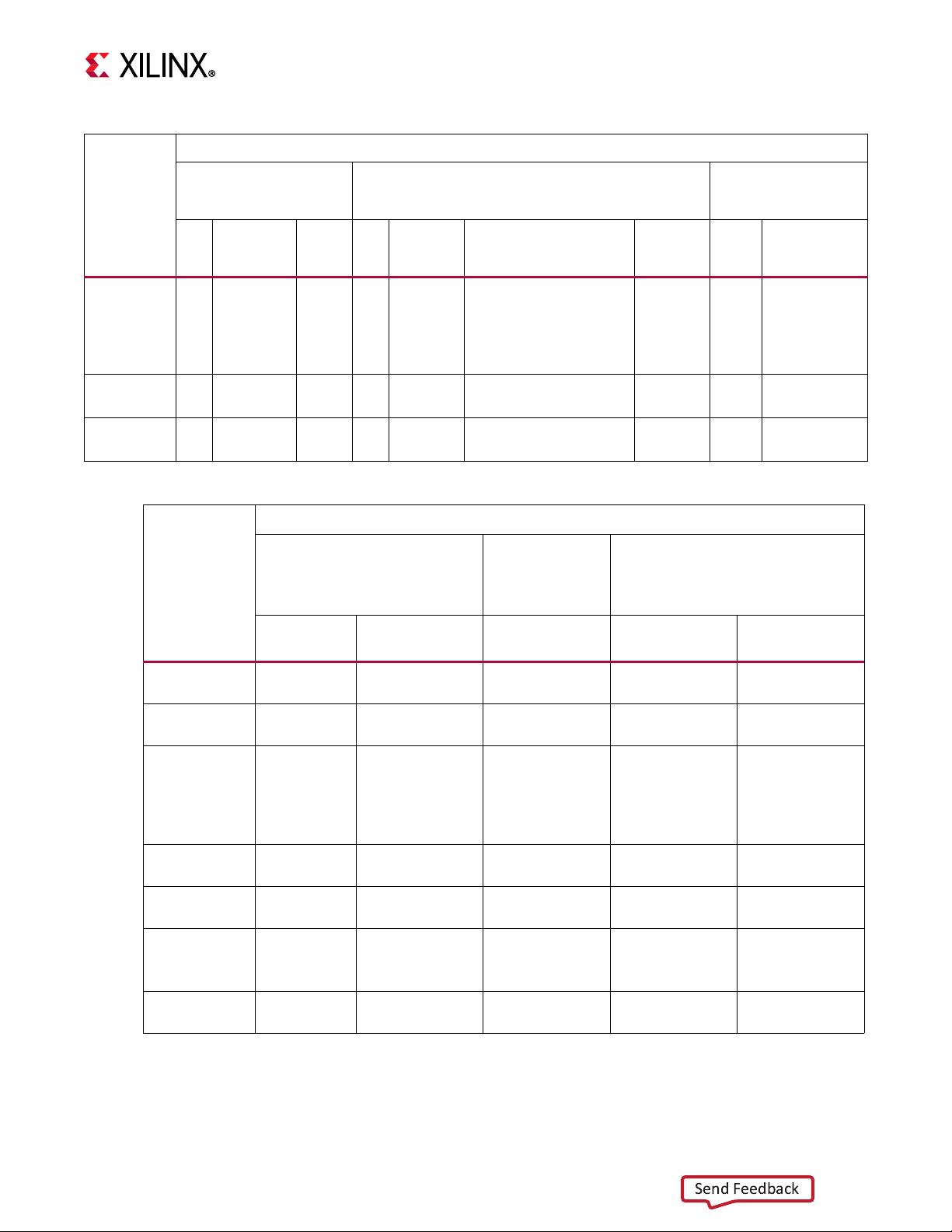

- **性能指标**:文档提供了关于速度、电压需求、速度等级以及资源利用率的具体数据,帮助设计师评估其在特定设计中的可行性。

- **端口描述**:列出了每个接口的功能和配置选项,以便于集成到系统架构中。

- **寄存器空间**:详细说明了控制和状态寄存器的组织和功能,便于用户进行配置和调试。

**章节3:设计与核心使用**

- **通用设计原则**:给出了共享逻辑、时钟管理、复位机制以及与TX/RX(发送/接收)模块的交互建议。

- **1000BASE-X和2500BASE-X**:针对两种不同的光纤传输标准,提供特定的实现技术和注意事项。

- **SGMII与动态切换**:讲解如何在不同的数据速率下灵活切换至SGMII模式,以及在LVDS(Low-Voltage Differential Signaling)环境下的同步/异步通信。

- **Ten-Bit Interface**:描述了十位接口的特性和用法,可能是为了支持更高的带宽需求。

- **客户侧GMII数据路径**:说明如何使用GMII接口与外部系统通信,可能包括数据流管理和协议解析。

- **自动协商**:解释了核心如何实现自动协商,以适应不同设备间的通信协议兼容性。

- **动态标准切换**:介绍如何在1000BASE-X和SGMII之间动态选择标准,以优化系统性能。

- **与其他核心的接口**:指导用户如何与其他IP核协同工作,确保整体系统设计的无缝连接。

- **特殊设计考虑**:针对特定应用环境可能遇到的问题和解决方案进行了深入讨论。

**章节4:设计流程步骤**

- **定制和生成核心**:详细说明如何根据项目需求对IP核进行定制,包括参数设置和接口配置。

- **用户反馈**:鼓励用户向Xilinx提供反馈,以便持续改进产品和文档质量。

这份文档是设计人员在使用Xilinx的1G/2.5G Ethernet PCS/PMA或SGMII v16.1 LogiCORE IP时的重要参考,提供了全面的技术细节和设计指导,帮助工程师高效地集成并优化高速以太网接口。

2023-06-25 上传

点击了解资源详情

2019-08-15 上传

hbicecream1

- 粉丝: 0

- 资源: 21

最新资源

- MD5加密文档,包括原理及代码

- Rampant.TechPress.Oracle.SQL.Internals.Handbook

- ext中文手册整理版

- 电子商务大赛资料2-试题下面有

- java2实用教程(第3版例子代码).doc

- mapinfo开发的三种方法

- 技术资料下载\嵌入式软件编程的论文30篇\ERA2000成像测井地面仪器硬件的设计与实现.pdf

- Advanced_Python_programming

- Struts常见错误汇总.txt

- 酒店管理系统可行性分析

- VHDL基础教程学习

- max232 pdf

- emule 源码分析

- 基于J2EE的Ajax宝典

- eclipse中文使用文档

- 浅谈Java的输入输出流.pdf