Verilog HDL入门教程:华为内部培训资料

"Verilog_HDL_华为入门教程.pdf"

Verilog HDL是一种广泛使用的硬件描述语言,用于设计和验证数字电子系统,包括集成电路。华为的这个入门教程详细介绍了Verilog的基础知识,帮助初学者快速掌握该语言的核心概念。

教程首先介绍了Verilog的基本语法,包括标识符、关键词、注释、书写规范等。标识符用于命名模块、变量和其他设计元素,而关键词是Verilog语言中的特定词汇,如`module`、`input`、`output`等。书写规范的建议确保代码清晰易读,这对于团队合作和代码维护至关重要。

在数据类型部分,教程讲解了线网类型和寄存器类型。线网类型表示信号的连接,而寄存器类型则用于存储数据。此外,还提到了常量、值集合和数字值集合,这些都是定义设计参数和逻辑状态的基础。

运算符和表达式是Verilog编程的重要组成部分。教程涵盖了算术运算符、关系运算符、逻辑运算符、按位逻辑运算符以及条件和连接运算符。这些运算符用于构建复杂的逻辑表达式,实现数字逻辑功能。

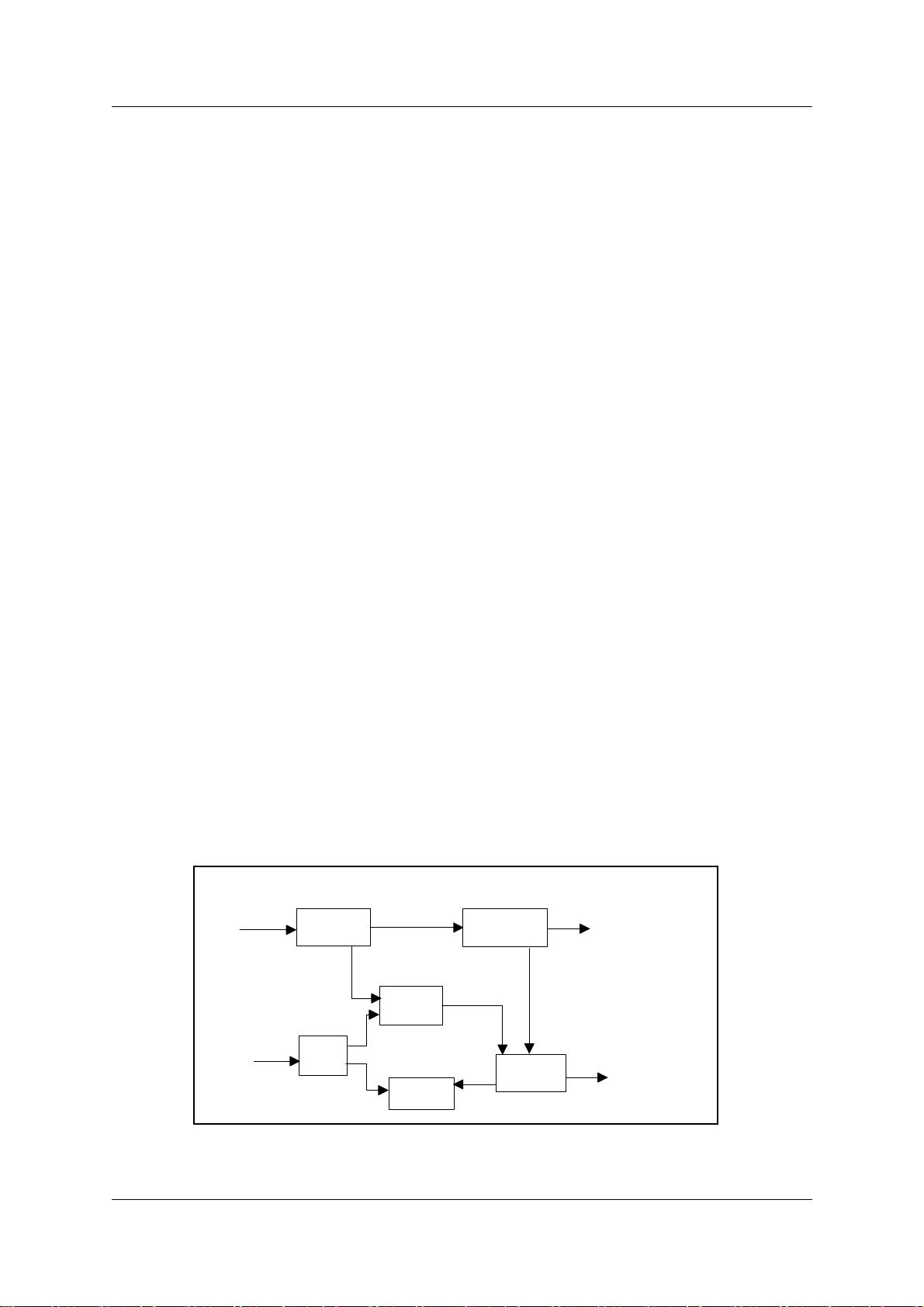

建模是Verilog的核心,教程详细阐述了三种建模方式:结构化描述、数据流描述和行为描述。结构化描述模仿电路的实际布局,数据流描述关注数据如何在不同组件间流动,而行为描述则更注重系统的功能表现。这些建模方式使得设计者可以从不同角度理解并实现设计。

在建模的章节中,教程介绍了模块的概念,包括模块的结构、时延和混合设计描述。模块是Verilog设计的基本单元,可以包含输入、输出、内部信号和子模块。时延描述了信号在逻辑操作中的延迟,混合设计描述允许在同一个设计中结合使用多种建模方式。

行为建模部分涉及了顺序语句块、过程赋值语句和具体实例。这些内容帮助设计者编写能够模拟实际硬件行为的代码。例如,`case`语句用于选择执行特定分支,条件语句控制流程,而连接运算符则用于合并多个信号。

最后,教程还包含了习题和附录,其中附录列出了Verilog的保留字,供学习者参考。通过这个入门教程,读者将能够掌握Verilog的基础,并开始进行数字系统的设计和验证工作。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-24 上传

119 浏览量

2022-02-13 上传

2022-09-14 上传

105 浏览量

2014-06-12 上传

li987072220

- 粉丝: 3

- 资源: 51

最新资源

- 掌握JSON:开源项目解读与使用

- Ruby嵌入V8:在Ruby中直接运行JavaScript代码

- ThinkErcise: 20项大脑训练练习增强记忆与专注力

- 深入解析COVID-19疫情对HTML领域的影响

- 实时体育更新管理应用程序:livegame

- APPRADIO PRO:跨平台内容创作的CRX插件

- Spring Boot数据库集成与用户代理分析工具

- DNIF简易安装程序快速入门指南

- ActiveMQ AMQP客户端库版本1.8.1功能与测试

- 基于UVM 1.1的I2C Wishbone主设备实现指南

- Node.js + Express + MySQL项目教程:测试数据库连接

- tumbasUpk在线商店应用的UPK技术与汉港打码机结合

- 掌握可控金字塔分解与STSIM图像指标技术

- 浏览器插件:QR码与短链接即时转换工具

- Vercel部署GraphQL服务的实践指南

- 使用jsInclude动态加载JavaScript文件的方法与实践