没有合适的资源?快使用搜索试试~ 我知道了~

首页REALTEK RTD2482D HDMI1.3多功能显示控制器技术规格

"RTD2482D是一款由REALTEK公司生产的HDMI1.3多功能显示控制器,主要用于处理视频信号的捕获、转换和显示。该控制器具备丰富的功能和高级特性,如全局事件标志、看门狗定时器、输入视频捕获、显示格式控制、色彩处理以及内置的时序控制器等。"

详细说明:

1. **REALTEK RTD2482D**: 这是REALTEK公司设计的一款高性能显示控制器,专门针对HDMI1.3标准,适用于各种显示设备,如电视、显示器和投影仪等。

2. **HDMI1.3兼容性**: HDMI1.3标准支持更高的数据传输速率和更丰富的色彩空间,确保了高质量的数字音频和视频传输。

3. **多功能特性**: RTD2482D集成了多种功能,包括输入视频捕获、帧窗口控制、FIFO频率管理、缩放控制、显示格式设置、显示微调、循环冗余校验(CRC)、FIFO窗口、上拉缩放、帧同步微调、同步处理器、宏视(MacroVision)防拷贝技术等。

4. **全球事件标志(Global Event Flag)**: 这个特性允许控制器根据特定事件触发相应的操作,增强了系统的灵活性和响应性。

5. **看门狗定时器(WatchDog)**: 用于监控系统状态,如果检测到异常,可以自动复位,保障系统的稳定运行。

6. **输入视频捕获**: 支持不同来源的视频输入,如HDMI、DVI或其它模拟视频源,并能进行有效的信号处理。

7. **显示格式控制**: 可以适应多种分辨率和颜色格式,满足不同的显示需求。

8. **色彩处理**: 包括对比度、亮度系数调整、伽马控制、色度处理、抖动控制、叠加/色板/背景色控制,以及图像自动功能,提供细腻的色彩调整。

9. **嵌入式时序控制器(Embedded Timing Controller, TCON)**: 自动配置显示设备的水平和垂直时序,确保准确的显示输出。

10. **LVDS和RSDS控制**: 提供对低电压差分信号(LVDS)和射频串行数字接口(RSDS)的支持,适应不同类型的显示面板。

11. **测试功能**: 为了调试和优化,控制器内置了测试模式,方便工程师进行性能评估和故障排查。

12. **嵌入式OSD**: 支持在屏幕上显示操作系统菜单或用户界面,增强用户体验。

13. **数字滤波**: 通过数字滤波技术改善图像质量,减少噪声和失真。

14. **VBI控制**: 对垂直消隐间隔(VBI)数据进行处理,如 Closed Caption 字幕或Teletext。

15. **视频色彩空间转换**: 如YUV到RGB的转换,确保不同格式的视频信号能正确显示。

RTD2482D是一款高度集成的显示控制器,提供了全面的视频处理能力,适用于需要高清晰度和多样化的显示应用。其强大的功能和灵活性使得它在现代显示设备设计中具有广泛的适用性。

REALTEK RTD2472/2482D Series-GR

16

( GPIO

open-drain )

XO AO

127

Crystal Output

XI AI

128

Crystal Input

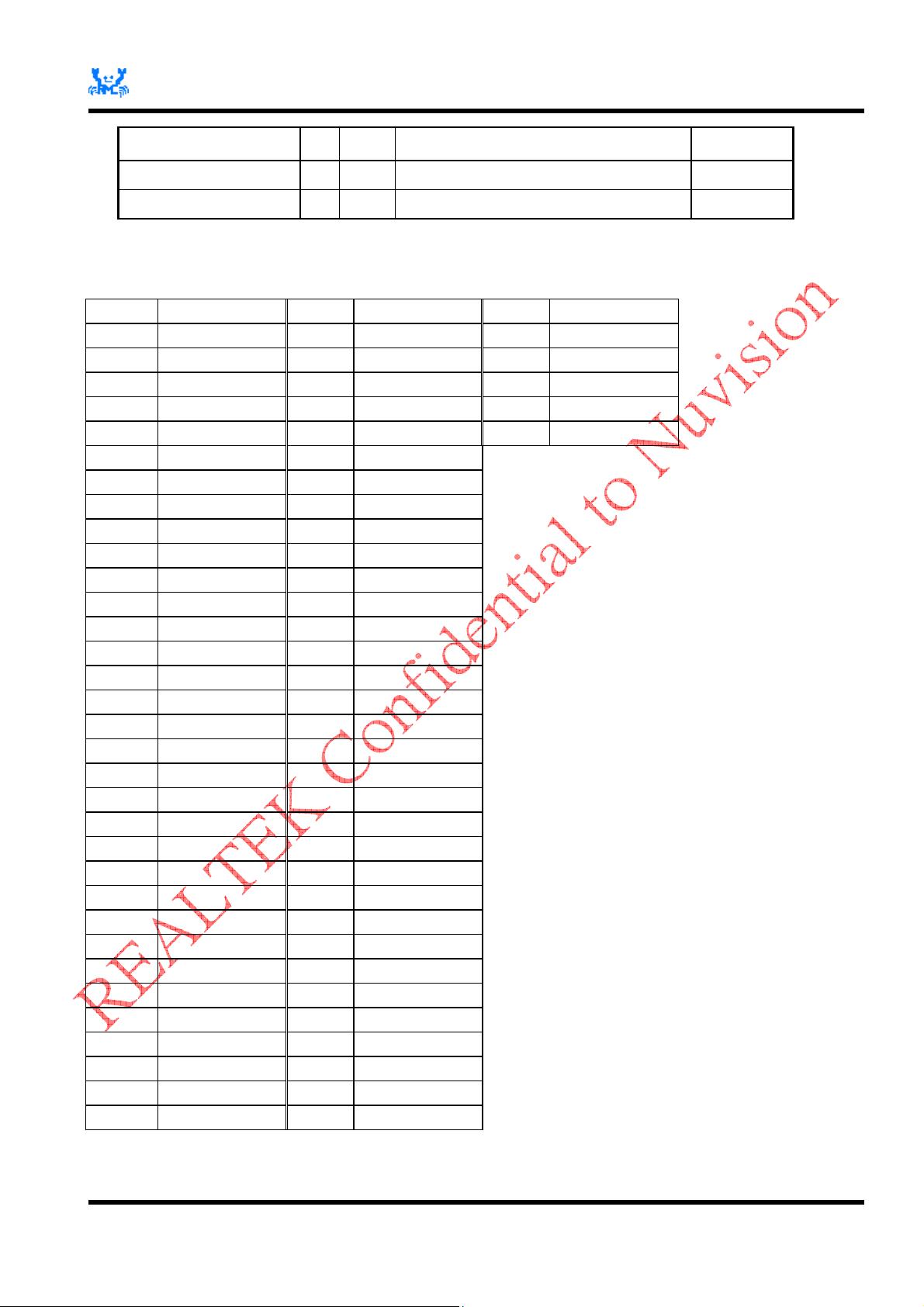

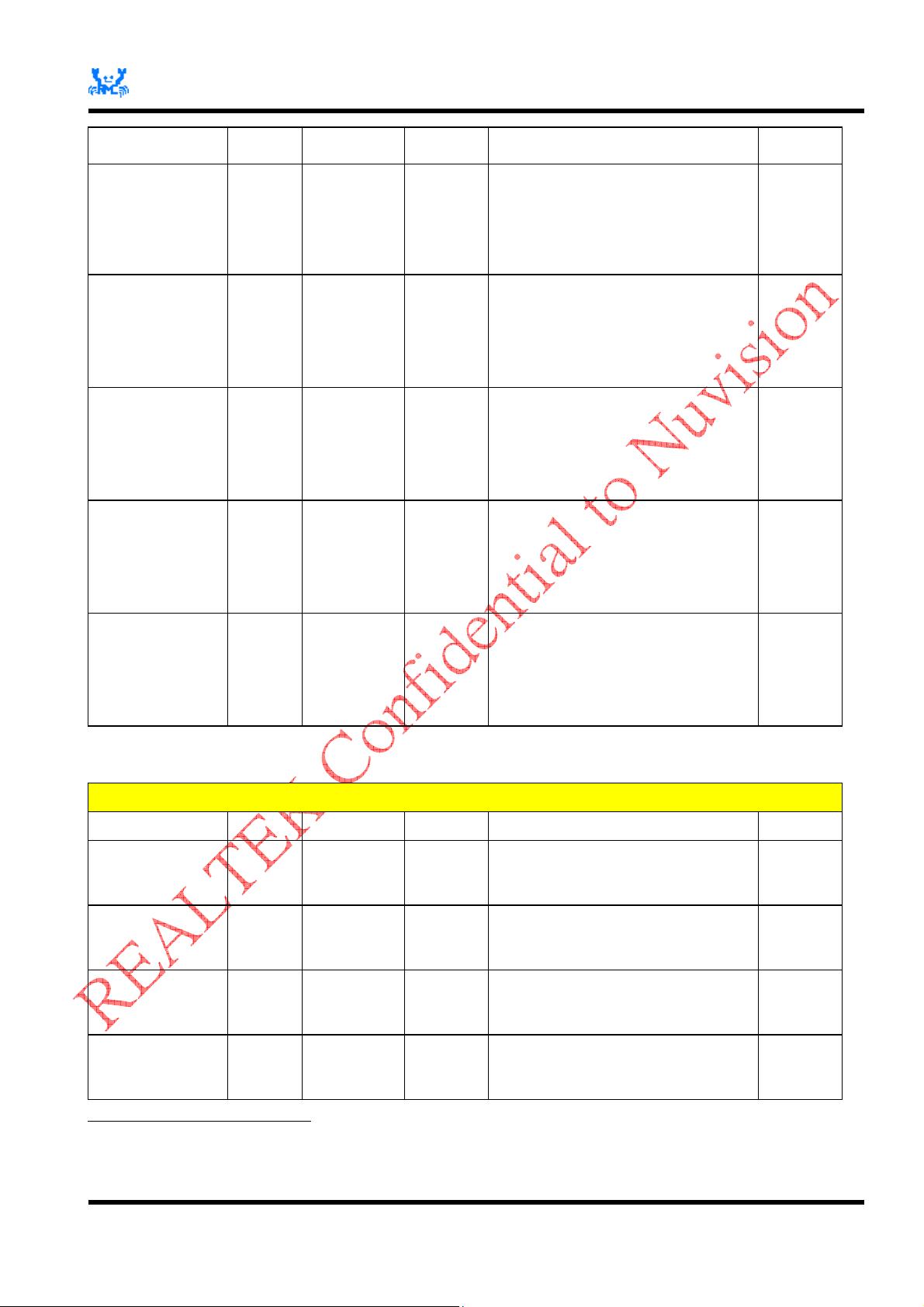

MCU GPIO assignment

PIN No.

PIN No.PIN No.

PIN No.

MCU

MCU MCU

MCU GPIO Name

GPIO NameGPIO Name

GPIO Name

PIN No.

PIN No.PIN No.

PIN No.

MCU

MCU MCU

MCU GPIO Name

GPIO NameGPIO Name

GPIO Name

PIN No.

PIN No.PIN No.

PIN No.

MCU

MCU MCU

MCU GPIO Na

GPIO NaGPIO Na

GPIO Name

meme

me

31

3131

31

PD.

PD.PD.

PD.7

77

7

70

7070

70

P1.6

P1.6P1.6

P1.6

121

121121

121

P7.3

P7.3P7.3

P7.3

32

3232

32

PD.

PD.PD.

PD.6

66

6

71

7171

71

P1.7

P1.7P1.7

P1.7

122

122122

122

P7.2

P7.2P7.2

P7.2

33

3333

33

PD.

PD.PD.

PD.5

55

5

72

7272

72

PC.

PC.PC.

PC.2

22

2

123

123123

123

P7.1

P7.1P7.1

P7.1

34

3434

34

PD.

PD.PD.

PD.4

44

4

74

7474

74

P9.0

P9.0P9.0

P9.0

124

124124

124

P7.0

P7.0P7.0

P7.0

35

3535

35

PD.

PD.PD.

PD.3

33

3

75

7575

75

P9.1

P9.1P9.1

P9.1

126

126126

126

PC.

PC.PC.

PC.0

00

0

36

3636

36

PD.

PD.PD.

PD.2

22

2

76

7676

76

P9.2

P9.2P9.2

P9.2

37

3737

37

PD.

PD.PD.

PD.1

11

1

77

7777

77

P9.3

P9.3P9.3

P9.3

39

3939

39

PD.

PD.PD.

PD.0

00

0

78

7878

78

P9.4

P9.4P9.4

P9.4

41

4141

41

PB.

PB.PB.

PB.7

77

7

79

7979

79

PA.0

PA.0PA.0

PA.0

42

4242

42

PB.

PB.PB.

PB.6

66

6

80

8080

80

PA.1

PA.1PA.1

PA.1

3

33

3

PB.

PB.PB.

PB.5

55

5

81

8181

81

PA.2

PA.2PA.2

PA.2

44

4444

44

PB

PBPB

PB4

44

4

82

8282

82

PA.3

PA.3PA.3

PA.3

45

4545

45

PB

PBPB

PB.

..

.3

33

3

83

8383

83

PA.4

PA.4PA.4

PA.4

46

4646

46

PB.

PB.PB.

PB.2

22

2

94

9494

94

P5.0 (removed)

P5.0 (removed)P5.0 (removed)

P5.0 (removed)

47

4747

47

PB.

PB.PB.

PB.1

11

1

95

9595

95

P5.1 (removed)

P5.1 (removed)P5.1 (removed)

P5.1 (removed)

48

4848

48

PB.

PB.PB.

PB.0

00

0

96

9696

96

P5.2

P5.2P5.2

P5.2

50

5050

50

P6.0

P6.0P6.0

P6.0

97

9797

97

P5.3

P5.3P5.3

P5.3

51

5151

51

P6.1

P6.1P6.1

P6.1

98

9898

98

P5.4

P5.4P5.4

P5.4

52

5252

52

P6.2

P6.2P6.2

P6.2

99

9999

99

P5.5

P5.5P5.5

P5.5

53

5353

53

P6.3

P6.3P6.3

P6.3

100

100100

100

P5.6

P5.6P5.6

P5.6

54

5454

54

P6.4

P6.4P6.4

P6.4

101

101101

101

P5.7

P5.7P5.7

P5.7

55

5555

55

P6.5

P6.5P6.5

P6.5

102

102102

102

P7.6

P7.6P7.6

P7.6

56

5656

56

P6.6

P6.6P6.6

P6.6

103

103103

103

P7.5

P7.5P7.5

P7.5

57

5757

57

P6.7

P6.7P6.7

P6.7

104

104104

104

P7.4

P7.4P7.4

P7.4

58

5858

58

P3.0/RXD(I/O)

P3.0/RXD(I/O)P3.0/RXD(I/O)

P3.0/RXD(I/O)

105

105105

105

P8.0

P8.0P8.0

P8.0

59

5959

59

P3

P3P3

P3.1/TXD(O)

.1/TXD(O).1/TXD(O)

.1/TXD(O)

108

108108

108

P8.1/CLKO1(O)

P8.1/CLKO1(O)P8.1/CLKO1(O)

P8.1/CLKO1(O)

63

6363

63

PC.

PC.PC.

PC.3

33

3

109

109109

109

P3.2/INT0(I)

P3.2/INT0(I)P3.2/INT0(I)

P3.2/INT0(I)

64

6464

64

P1.0/T2(I)

P1.0/T2(I)P1.0/T2(I)

P1.0/T2(I)

110

110110

110

P3.3/INT1(I)

P3.3/INT1(I)P3.3/INT1(I)

P3.3/INT1(I)

65

6565

65

P1.1/T2EX(I)

P1.1/T2EX(I)P1.1/T2EX(I)

P1.1/T2EX(I)

111

111111

111

P3.4/T0

P3.4/T0P3.4/T0

P3.4/T0

66

6666

66

P1.2/CLKO2(O)

P1.2/CLKO2(O)P1.2/CLKO2(O)

P1.2/CLKO2(O)

112

112112

112

P3.5(BS)/T1

P3.5(BS)/T1P3.5(BS)/T1

P3.5(BS)/T1

67

6767

67

P1.3

P1.3P1.3

P1.3

113

113113

113

P3.6

P3.6P3.6

P3.6

68

6868

68

P1.4

P1.4P1.4

P1.4

114

114114

114

P3.7

P3.7P3.7

P3.7

69

6969

69

P1.5

P1.5P1.5

P1.5

119

119119

119

PC.

PC.PC.

PC.1

11

1

REALTEK RTD2472/2482D Series-GR

17

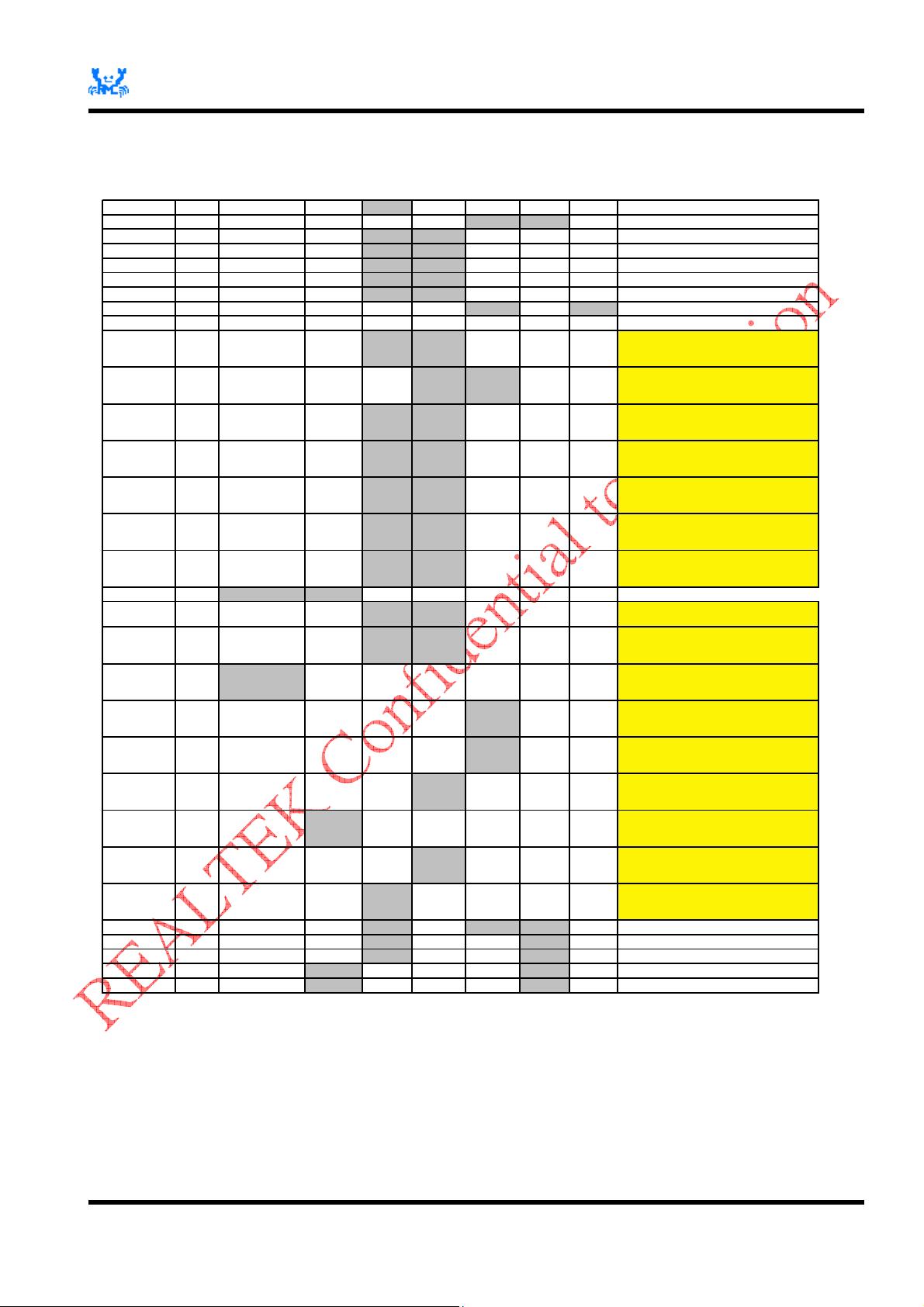

TCON Pin assignment notice:

Note : TCON [2] toggle function is inactive

#define _PIN_41

1: PBD0i, 2: PBD0o<open-drain> 3: PBD0o 4: TCON[5]

#define _PIN_55 1: P6D5o 2: P6D5o<push-pull>

3: ADCB0 4: PWM1

5: PWM5 6:TCON[0] 7:TCON[5]

#define _PIN_56 1: P6D6o 2: P6D6o<push-pull>

3: ADCB1 4: TCON[1]

5:TCON[4]

#define _PIN_57 1: P6D7o 2: P6D7o<push-pull>

3: ADCB2 4: TCON[9]

5:TCON[11]

#define _PIN_58 1: P3D0o 2: P3D0o<push-pull>

3: RXD 4: TCON[7]

5;TCON[10]

#define _PIN_59 1: P3D1o 2: P3D1o<push-pull>

3: TXD 4: TCON[3]

5:TCON[5]

#define _PIN_63 1: PCD0o 2: PCD0o<push-pull>

3: PWM2 4: TCON[1]

5: TCON[8]

#define _PIN_64 1: P1D0o 2: P1D0o<push-pull>

3: T2 4: SD0

5: SPDIF0 6: TCON[0] 7: IrDA 8:TCON[7]

#define _PIN_65 1: P1D1o 2: PWM1

3: T2EX 4: TCON[1]

5: TCON[7] 6: WS

TCON is only for RSDS SINGLE Mode

RSDS SINGLE ModeRSDS SINGLE Mode

RSDS SINGLE Mode ,

and it should be no eo-swap , RSDS Power Control

should be turn on (CR_8C-C3[0]= 1'b1)

#define _PIN_66 1: P1D2o 2: reserved

3: CLKO 4: SCK

5: TCON[2] 6: TCON[4]

TCON is only for RSDS SINGLE Mode

RSDS SINGLE ModeRSDS SINGLE Mode

RSDS SINGLE Mode ,

and it should be no eo-swap , RSDS Power Control

should be turn on (CR_8C-C3[0]= 1'b1)

#define _PIN_67 1: P1D3o 2: reserved

3: MCK 4: TCON[5]

5: TCON[9]

TCON is only for RSDS SINGLE Mode

RSDS SINGLE ModeRSDS SINGLE Mode

RSDS SINGLE Mode ,

and it should be no eo-swap , RSDS Power Control

should be turn on (CR_8C-C3[0]= 1'b1)

#define _PIN_68 1: P1D4o 2: reserved

3: SD0 4: TCON[3]

5: TCON[13] 6: SPDIF0

TCON is only for RSDS SINGLE Mode

RSDS SINGLE ModeRSDS SINGLE Mode

RSDS SINGLE Mode ,

and it should be no eo-swap , RSDS Power Control

should be turn on (CR_8C-C3[0]= 1'b1)

#define _PIN_69 1: P1D5o 2: reserved

3: SD1 4: TCON[3]

5: TCON[7] 6: SPDIF1 7: IICSCL

TCON is only for RSDS SINGLE Mode

RSDS SINGLE ModeRSDS SINGLE Mode

RSDS SINGLE Mode ,

and it should be no eo-swap , RSDS Power Control

should be turn on (CR_8C-C3[0]= 1'b1)

#define _PIN_70 1: P1D6o 2: reserved

3: SD2 4: TCON[9]

5: TCON[11] 6: SPDIF2 7: IICSDA

TCON is only for RSDS SINGLE Mode

RSDS SINGLE ModeRSDS SINGLE Mode

RSDS SINGLE Mode ,

and it should be no eo-swap , RSDS Power Control

should be turn on (CR_8C-C3[0]= 1'b1)

#define _PIN_71 1: P1D7o 2: PWM5

3: SD3 4: TCON[8]

5: TCON[10] 6: SPDIF3 7: PWM1

TCON is only for RSDS SINGLE Mode

RSDS SINGLE ModeRSDS SINGLE Mode

RSDS SINGLE Mode ,

and it should be no eo-swap , RSDS Power Control

should be turn on (CR_8C-C3[0]= 1'b1)

#define _PIN_72 1: PCD1o 2: TCON[6]

3:TCON[12] 4: PWM3

#define _PIN_99 1: P5D5o 2: reserved

3: PWM3 4: TCON[6]

5: TCON[11]

TCON is only forTTL Mode ,

and it should be

8C-A0 Bit 6 turn on.

#define _PIN_100 1: P5D6o 2: reserved

3: PWM4 4: TCON[3]

5: TCON[12]

TCON is only forTTL Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_101 1: P5D7o 2: TCON[0]

3: PWM5

TCON is only forTTL Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_102 1: P7D6o 2: PWM0

3: reserved 4: SD3

5: SPDIF3 6: TCON[10]

TCON is only forTTL Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_103 1: P7D5o 2: reserved

3: PWM1 4: SD2

5: SPDIF2 6: TCON[8] 7: IICSCL

TCON is only forTTL Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_104 1: P7D4o 2: reserved

3: SD1 4: IRQ

5: TCON[5] 6: SPDIF1 7: IICSDA

TCON is only forTTL

Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_105 1: P8D0o 2: reserved

3: TCON[9] 4: SD0

5: SPDIF0)

TCON is only forTTL Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_108 1: P8D1o 2: reserved

3: CLKO 4: MCK

5: TCON[7])

TCON is only forTTL Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_109 1: P3D2o 2: reserved

3: INT0 4: TCON[3]

5: SCK)

TCON is only forTTL Mode

ModeMode

Mode ,

and , RSDS Power Control should be turn on (CR_8C-

C3[1]= 1'b1)

#define _PIN_110 1: P3D3o 2: P3D3o<push-pull>

3: INT1 4: TCON[6]

5: WS 6:TCON[2] 7:TCON[7]

#define _PIN_111 1: P3D4o 2: P3D4o<push-pull>

3: T0 4: TCON[4]

5: SD0 6: SPDIF0 7:TCON[7]

#define _PIN_112 1: P3D5o 2: P3D5o<push-pull>

3: T1 4: TCON[9]

5: SD1 6: SPDIF1 7:TCON[5]

#define _PIN_113 1: P3D6o 2: P3D6o<push-pull>

3: TCON[1] 4: SD2

5: SPDIF2 6: IrDA 7:TCON[11]

#define _PIN_114 1: P3D7o 2: P3D7o<push-pull>

3: TCON[13] 4: SD3

5: SPDIF3 6: PWM4 7:TCON[0]

REALTEK RTD2472/2482D Series-GR

18

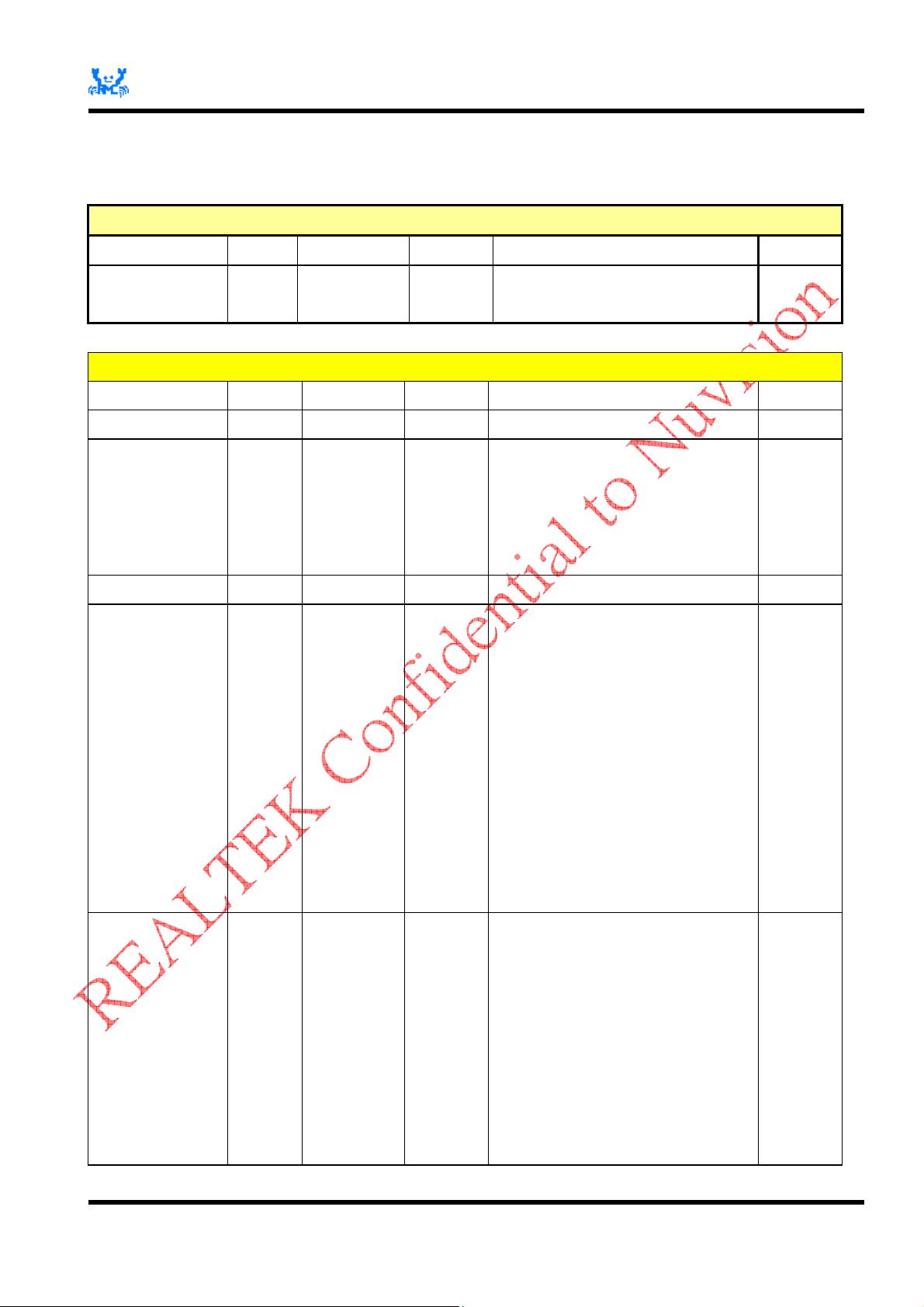

5. Register Description

Global Event Flag

Register::ID_Reg 0x00

Name Bit R/W Default Description Config

ID 7:0

R

0x01

MSB 4 bits: 0000 product code

LSB 4 bits: 0001 rev. code

Register:: Host_ctrl 0x01

Name Bit R/W Default Description Config.

Rev 7 --- 0 Reserved

Reset_chk 6 R/W 0

Reset Check

Once scalar is reset, this value will be

cleared to 0.The purpose of it is to check

if LVR has been triggered.

It should be written to 1 ahead, then

read it..LVR has been triggered if the

value is 0,else LVR has not.

Rev 5:3 --- ---

Reserved

PD_EN 2 R/W 1

Power Down Mode Enable

0: Norma

1: Enable power down mode

(Default)

Turn off ADC RGB Channel/ ADC

Band-gap/ SOG/ DPLL/ LVDS/ADC

PLL/ SYNC- PROC/ TMDS /

HDMI-Audio PLL/AUTO SOY

ADC/m2pll

Note: For LVDS/RSDS Power Control,

refer to following table.

PS_EN 1 R/W 1

Power Saving Mode Enable

0: Normal

1: Enable power saving mode (Default)

Turn off ADC RGB channel/ DPLL/

LVDS/ ADC PLL/ m2pll

When power down or power saving

function is enabled, internal mcu clock

is forced to crystal clock.

Note: For LVDS/RSDS Power Control,

REALTEK RTD2472/2482D Series-GR

19

refer to following table.

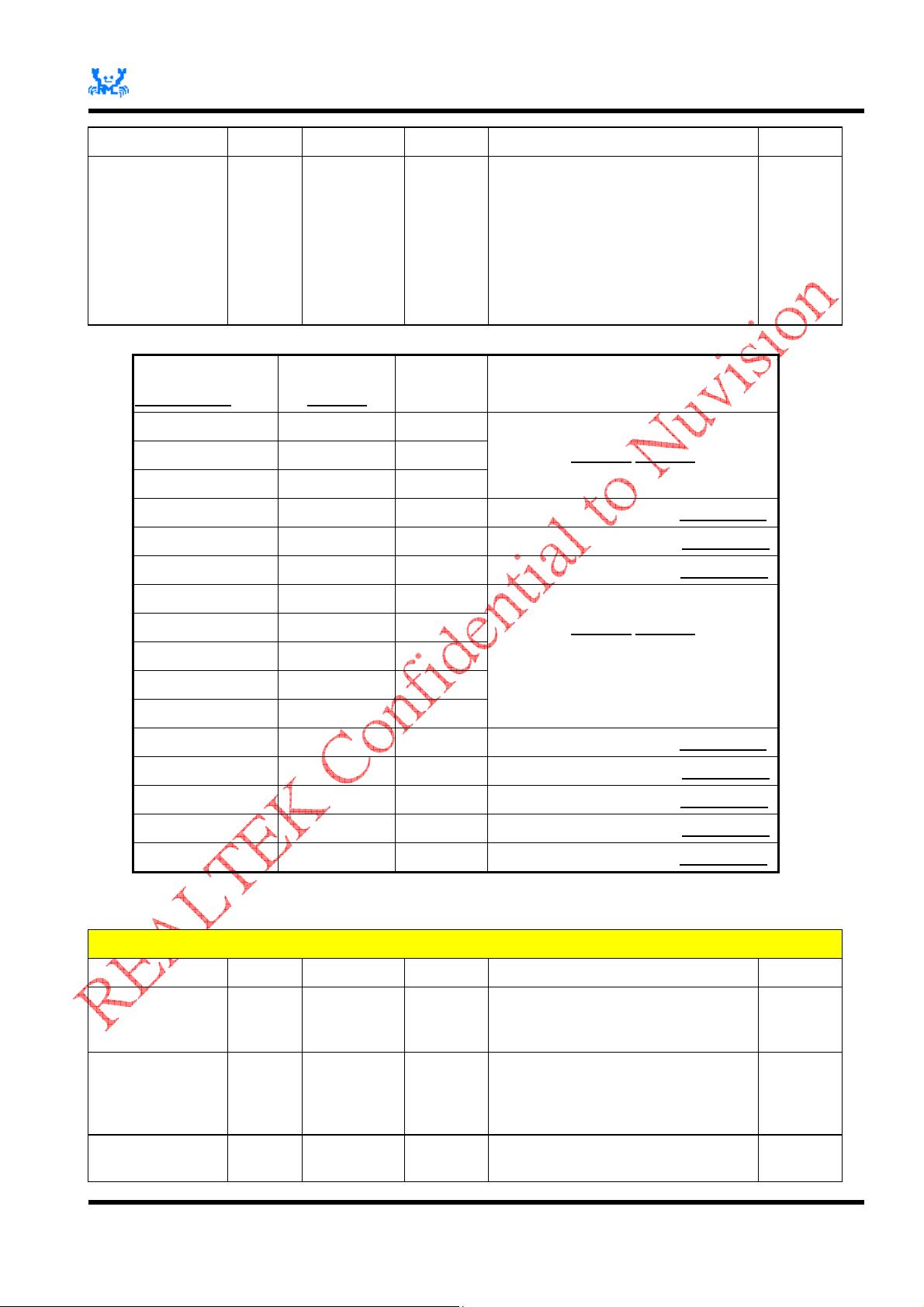

Sft_Reset 0 R/W 0

Software Reset Whole Chip (Low

pulse at least 8ms)

0: Normal (Default)

1: Reset

All registers are reset to default except

HOST_CTRL and power-on-latch.

Power Down/Power Saving control only effective when LVDS/RSD Display Output is double.

DISP_TYPE

CR 8E-00[1:0]

DATA_TYPE

CR 28[2]

Port Power Control

LVDS [01] Double [1]

LVDS Mid

Power Down/Power Saving

CR01 [2]/CR 01[1]

LVDS [01] Double [1]

LVDS Even

LVDS [01] Double [1]

LVDS Odd

LVDS [01] Single [0]

LVDS Mid

Power Up LVDS Mid-Port CR8C-A0 [6]

LVDS [01] Single [0]

LVDS Even

Power Up LVDS Even-Port CR8C-A0 [5]

LVDS [01] Single [0]

LVDS Odd

Power Up LVDS Odd-Port CR8C-A0 [4]

RSDS [10] Double [1]

LVDS Mid

Power Down/Power Saving

CR01 [2]/CR 01[1]

RSDS [10] Double [1]

LVDS Even

RSDS [10] Double [1]

LVDS Odd

RSDS [10] Double [1]

RSDS Even

RSDS [10] Double [1]

RSDS Odd

RSDS [10] Single [0]

LVDS Mid

Power Up LVDS Mid-Port CR8C-A0 [6]

RSDS [10] Single [0]

LVDS Even

Power Up LVDS Even-Port CR8C-A0 [5]

RSDS [10] Single [0]

LVDS Odd

Power Up LVDS Odd-Port CR8C-A0 [4]

RSDS [10] Single [0]

RSDS Even

Power Up RSDS Even-Port CR8C-C3 [1]

RSDS [10] Single [0]

RSDS Odd

Power Up RSDS Odd-Port CR8C-C3 [0]

Register:: STATUS0 0x02

Name Bit R/W Default Description Config.

ADCPLL_nonlock

7 R 0

ADC_PLL Non-Lock

If the ADC_PLL non-lock occurs, this

bit is set to “1”.

IVS_error 6 R 0

Input VSYNC Error

If the input vertical sync occurs within

the programmed active period, this bit is

set to “1”.

IHS_error 5 R 0

Input HSYNC Error

If the input horizontal sync occurs

REALTEK RTD2472/2482D Series-GR

20

within the programmed active period,

this bit is set to “1”.

ODD_Occur 4 R 0

Input ODD Toggle Occur (For internal

field odd toggle, refer to CR1A[5])

If the ODD signal (From SAV/EAV or

V16_ODD) toggle occurs, this bit is set

to “1”.

V8HV_Occur 3 R 0

Video8 Input Vertical/Horizontal

Sync Occurs

If the YUV input V or H sync edge

occurs, this bit is set to “1”.

ADCHV_Occur 2 R 0

ADC Input Vertical/Horizontal Sync

Occurs

Input V or H sync edge occurs; this bit

is set to “1”.

Buffer_Ovf1 1 R 0

Input Overflow Status (Frame Sync

Mode) *

1

If an overflow in the input data capture

buffer occurs, this bit is set to “1”.

Buffer_Udf1 0 R 0

Line Buffer Underflow Status (Frame

Sync Mode)

If an underflow in the line-buffer

occurs, this bit is set to “1”.

Write to clear status.

Register:: STATUS1 0x03

Name Bit R/W Default Description Config.

Buffer_Ovf2 7 R 0

Line Buffer Overflow Status

1: Line Buffer overflow has occurred

since the last status cleared

Buffer_Udf2 6 R 0

Line Buffer Underflow Status

1: Line Buffer underflow has occurred

since the last status cleared

DENA_Stop 5 R 0

DENA Stop Event Status

1: If the DENA stop event occurred

since the last status cleared

DENA_Start 4 R 0

DENA Start Event Status

1: If the DENA start event occurred

since the last status cleared as an

*

1

Only first event of input overflow/underflow is recorded if both of them occurs.

剩余381页未读,继续阅读

yuezhiying

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功