中国科大张展翔:信号处理与FPGA实验报告

需积分: 0 179 浏览量

更新于2024-06-30

收藏 1.42MB PDF 举报

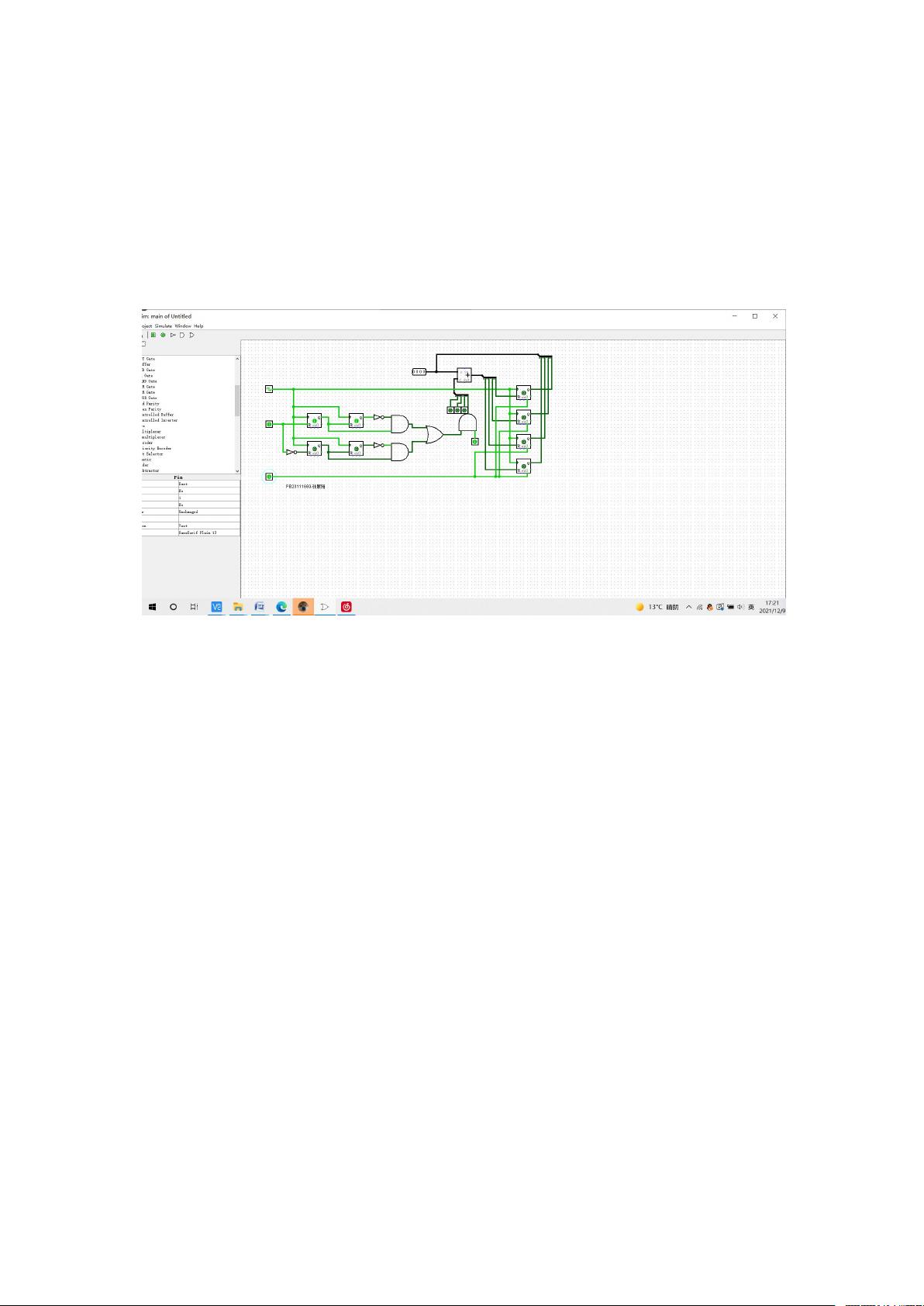

本篇实验报告由中国科学技术大学计算机学院的张展翔(学号PB20111669)于2021年12月16日完成,针对《数字电路实验》中的信号处理及有限状态机主题进行研究。实验的主要目标是让学生深化对FPGA开发的理解,包括整体流程、信号处理技术以及有限状态机的设计和应用。

首先,实验着重于提升学生的实践能力,通过使用如VLAB (vlab.ustc.eud.cn)、FPGAOL (fpgaol.ustc.edu.cn)、Logisim和Vivado等工具。实验分为三个部分:

1. 部分一:状态机逻辑设计 - 学生通过一个简单的4输入2输出的有限状态机实现,使用参数化来定义四种不同的状态转移,例如C_0到C_1,C_1到C_2,以此类推,并利用cur和nex寄存器控制状态转移。这部分涉及基本的状态机结构和状态转换规则。

2. 部分二:时钟同步与复位操作 - 在always @(posedge clk or posedge rst)语句中,设计了复位机制,当rst为高电平时,状态变量cur被重置为C_0,实现了状态机的初始化。

3. 部分三:状态指示与输出设计 - 通过比较cur和C_3的状态,控制led信号的输出,当cur等于C_3时,led输出低电平,否则为高电平,这展示了状态机在控制逻辑电路中的应用。

接下来的两个练习进一步巩固了这些技能:

- 题目2:计数器设计 - 学生被要求设计一个计数器电路,可能是一个模8或非同步计数器,用于展示有限状态机的计数功能和时序逻辑。

- 题目3:设计文件 - 提供了一个名为counter的模块,包含输入clk、rst、sw和button,以及输出数据和地址寄存器。在这个模块中,学生需要使用状态机设计一个计数器,同时考虑按钮输入的控制,可能涉及到自增计数、清零以及按钮状态检测等功能。

整个实验旨在通过实际操作,使学生能够在理论知识基础上,熟练地将有限状态机应用于数字电路设计中,从而提高他们解决实际问题的能力和数字信号处理技术的掌握程度。通过这次实验,学生不仅能够深化理解信号处理原理,还能够提升FPGA硬件编程和调试的技能。

2022-08-04 上传

126 浏览量

2022-08-04 上传

2022-08-04 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

126 浏览量

1144 浏览量

宝贝的麻麻

- 粉丝: 42

- 资源: 294

最新资源

- Perl 二十四小时搞定

- 简明 Python 教程 《a byte of python》中译本

- 3G技术普及手册(华为内部版)

- 广告公司固定管理系统-需求分析

- 相当全面的J2EE面试题!!!

- rails_plugins_presentation.pdf

- SOA 案例研究:不同应用程序的集成组织

- ajax--dwr测试

- Servlet_JSP

- java struts 教程

- Struts 中文简介

- 五星_中兴《GSM移动通信基本知识》_

- 数据库第四版答案 大学教材课后答案

- 正则表达式30分钟入门教程

- 三级C语言上机南开100题(2009年终结修订word版).doc

- 基于IBM DS4500磁盘阵列的配置实验