用Logisim与Verilog实现1-bit二选一选择器及真值表自动生成

需积分: 0 12 浏览量

更新于2024-08-04

收藏 963KB PDF 举报

本实验是关于《数字电路实验》的项目,由张展翔同学(学号PB20111669)在中国科学技术大学计算机学院进行。实验目标旨在提高学生对Logisim软件的熟练运用,包括电路设计和仿真,以及初步理解Verilog语言的基础知识。

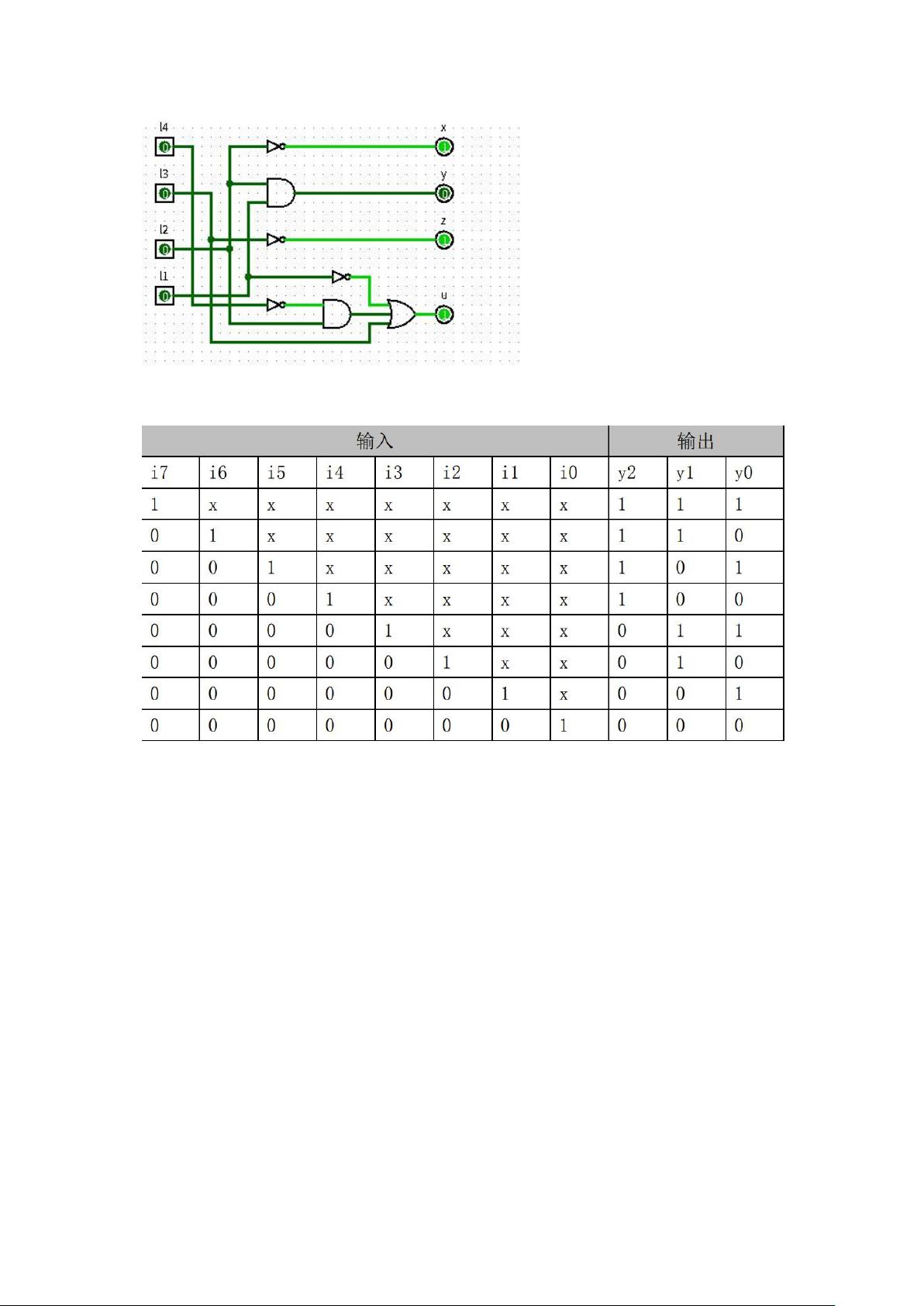

在实验2中,学生需要通过真值表构建一个1-bit的二选一选择器。首先,学生利用Logisim的AnalyzeCircuit功能,将四个输入和输出进行编号,并输入真值表数据,这个过程帮助他们理解逻辑函数的对应关系。根据真值表,输出信号的表达式被确定为y2, y1, y0,这些表达式展示了如何使用逻辑运算符(如与(&)、或(|)和非(~))来实现选择逻辑。

通过"Project"菜单中的"Analyze Circuit"功能,学生可以直接输入表达式生成电路。这涉及到电路优化,即使用"Minimized"选项卡对表达式进行简化,以减少逻辑门的数量。通过对比化简前后的电路结构,可以看到逻辑门的节省对于电路复杂度的显著影响。

此外,实验还涉及Verilog Hardware Description Language (HDL)的入门,这是一种用于描述硬件电路行为的高级编程语言。在这个阶段,学生学习了Verilog模块的基本结构,如`module`的定义,包括输入端口和输出端口的声明。这标志着他们开始从逻辑设计过渡到硬件描述层面,为未来的数字系统设计打下基础。

本实验不仅锻炼了学生的逻辑思维和电路设计技能,还让他们接触到实际的硬件描述语言,为他们在IT领域特别是电子设计自动化(EDA)方面的发展奠定了坚实的基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-04 上传

2022-08-04 上传

2022-08-04 上传

2022-08-04 上传

点击了解资源详情

点击了解资源详情

高中化学孙环宇

- 粉丝: 15

- 资源: 338

最新资源

- simulatedevice_v1.0.7.zip

- 垃圾分类网站管理系统-毕业设计

- 火车订票系统.rar

- Moriyama.SuperDocTypeCreate

- CordovaGui-开源

- mri_demo

- 练习4

- Jekyll静态站点生成器 v3.6.1

- class26rishon

- C++面向对象多线程编程-pdf

- 基于Springboot与Vue的学生选课系统毕业设计

- 租赁系统。。.rar

- AreaTri(P1,P2,P3):给定顶点的 3D 坐标的三角形面积-matlab开发

- dynamic-charts-reactjs

- FirebaseAuthentication

- C++后台开发 核心技术与应用实践