8086微处理器:内部结构与系统设计解析

需积分: 9 34 浏览量

更新于2024-07-27

收藏 522KB PPT 举报

"8086微处理器及其系统结构"

8086微处理器是Intel公司于1978年推出的一款16位微处理器,它以其先进的架构和强大的处理能力在个人计算机领域起到了里程碑式的作用。该处理器是IBM PC及其兼容机的基础,奠定了现代计算机系统的基础。

2.1 8086微处理器

8086的内部结构分为两个主要部分:执行单元(Execution Unit, EU)和总线接口单元(Bus Interface Unit, BIU)。执行单元负责执行指令,而BIU则处理与内存和I/O设备的数据传输。

- 执行单元(EU)包含:

- 算术逻辑单元(ALU):执行算术和逻辑运算,并计算寻址的16位偏移地址。

- 标志寄存器(F):存储运算结果的状态标志,如零标志、进位标志等。

- 数据暂存寄存器:协助ALU进行运算,暂时存储数据。

- 通用寄存器:包括AX、BX、CX、DX、SP、BP、SI和DI,用于数据处理和地址计算。

- EU控制电路:解析指令并生成控制信号以协调EU各部分的工作。

- 总线接口单元(BIU)包括:

- 指令队列缓冲器:类似于指令寄存器,存储待执行的指令。

- 地址加法器和段寄存器:将逻辑地址转换为物理地址。

- 指令指针寄存器(IP):存储下一条要执行的指令的段内偏移地址。

- 总线控制电路:生成与外部总线交互所需的控制信号。

- 内部通讯寄存器:用于EU和BIU之间的数据交换。

2.2 总线周期与总线结构

总线周期是8086处理数据时的基本时间单位,包括T1、T2、T3、T4和T5五个阶段,涉及地址锁存、数据读写等操作。8086采用三态总线,支持数据总线、地址总线和控制总线,分别用于传输数据、内存和I/O设备的地址以及控制信号。

2.3 8086总线操作时序

总线操作时序是CPU与内存或I/O设备交互的具体步骤,包括读周期、写周期等,确保数据正确无误地在CPU和外部设备之间传输。

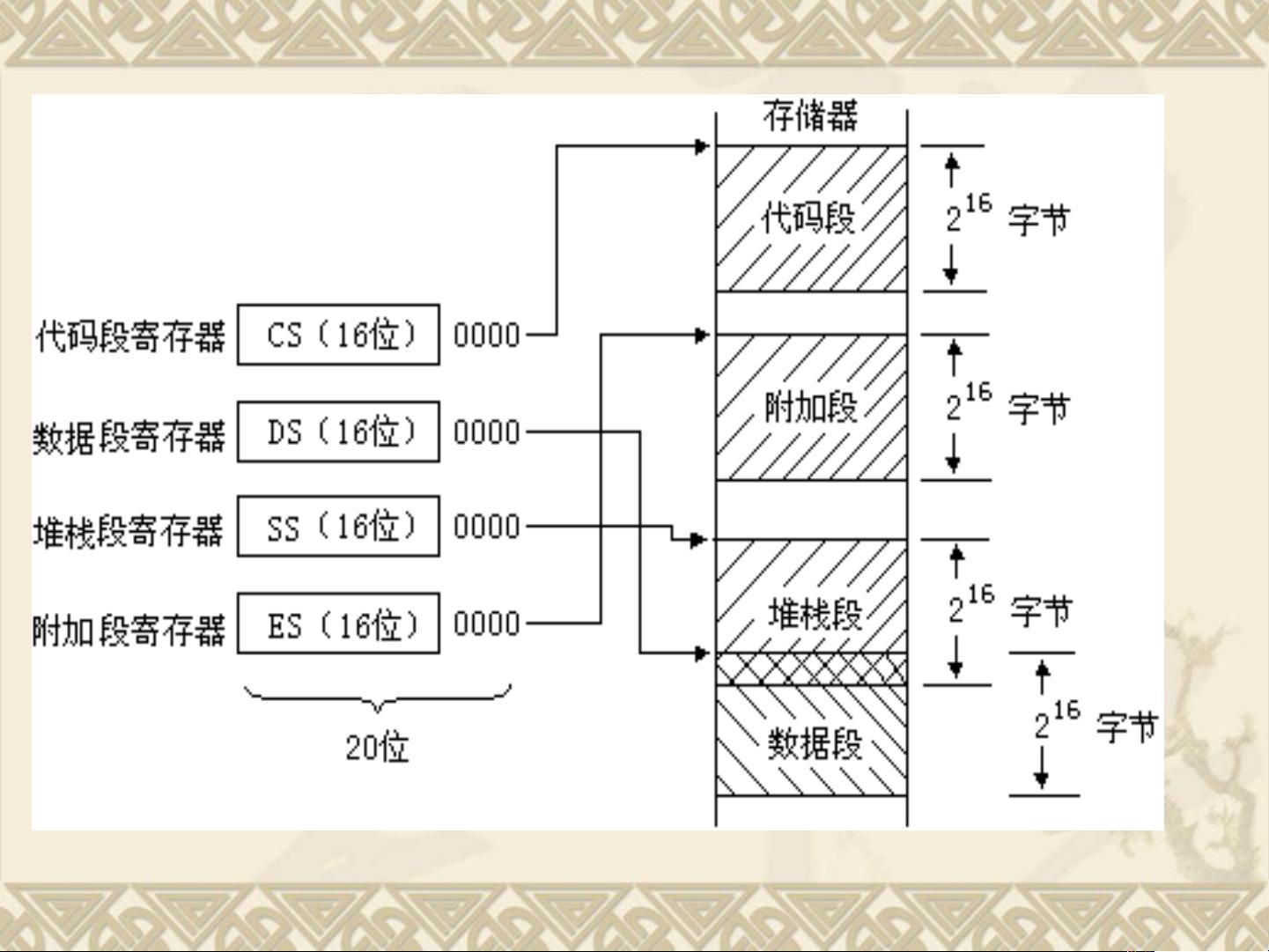

在8086系统中,为了扩展16位处理器的寻址能力,引入了段寄存器。每个段寄存器(CS、DS、ES、SS)存储16位的段基址,配合32位的偏移地址(由IP、BX、BP、SP、SI、DI中的一个提供),共同构成20位的物理地址。通过这种方式,8086能访问高达1MB(2^20字节)的内存空间。

总结来说,8086微处理器的系统结构是其高效运行的关键,包括其内部复杂的执行单元和总线接口单元,以及独特的地址寻址机制。这些设计使得8086不仅能够执行多种指令,还能处理大量数据,从而成为当时个人计算机发展的基石。

2011-05-10 上传

2010-04-14 上传

2021-09-17 上传

2021-09-17 上传

2021-10-09 上传

点击了解资源详情

点击了解资源详情

jazzyquenn

- 粉丝: 0

- 资源: 1

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜