Accellera

Analog and Mixed-signal Extensions to Verilog HDL Version 2.3.1, June 1, 2009

3 Copyright © 2009 Accellera Organization, Inc. All rights reserved.

connected to the node so all continuous ports and nets see the same potential. The flow is shared so flow

from all continuous ports and nets at a node shall sum to zero (

0). In this way, the node acts as an infinitesi-

mal point of interconnection in which the potential is the same everywhere on the node and on which no

flow can accumulate. Thus, the node embodies Kirchhoff's Potential and Flow Laws (KPL and KFL). When

a component connects to a node through a conservative port or net, it can either affect, or be affected by,

either the potential at the node, and/or the flow onto the node through the port or net.

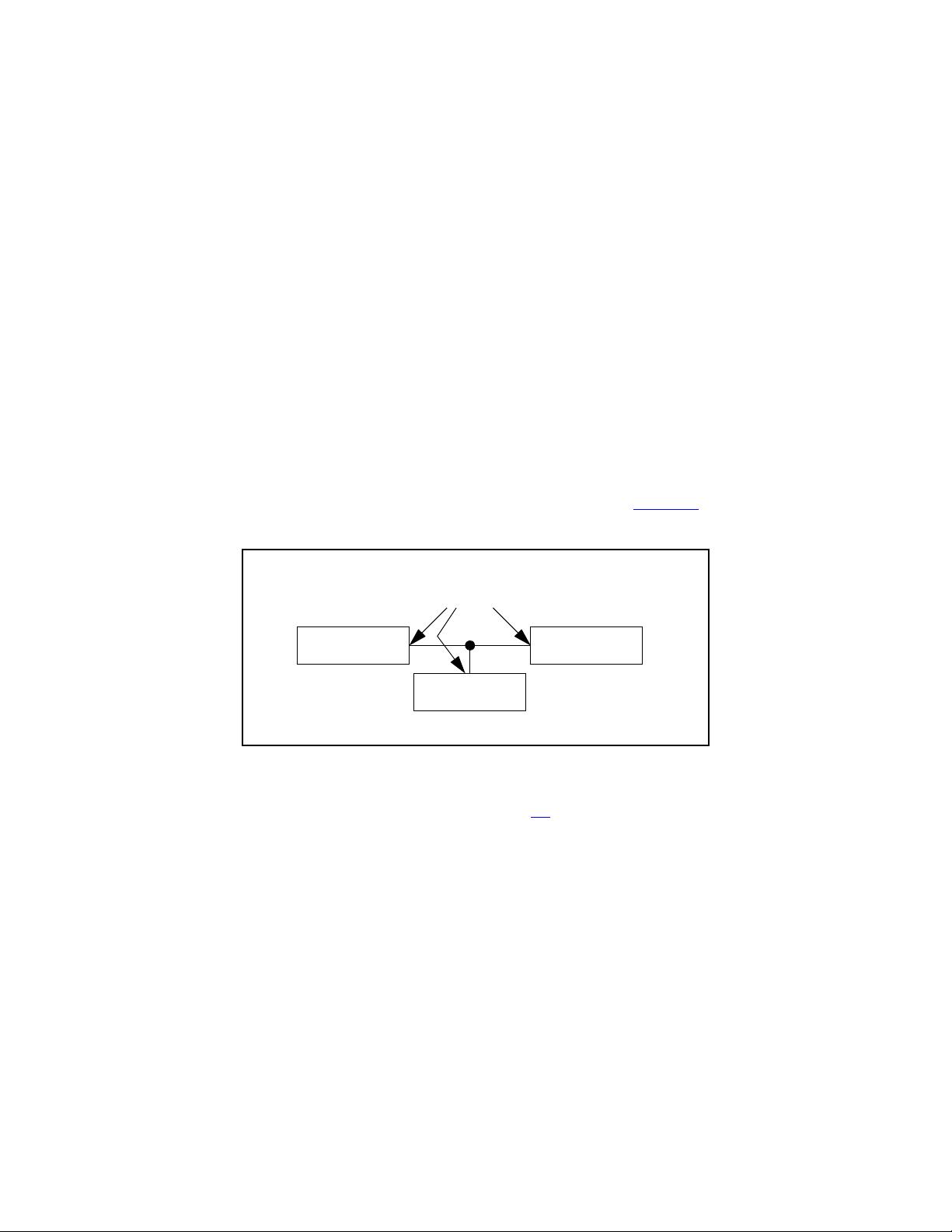

With conservative systems it is also useful to define the concept of a branch. A branch is a path of flow

between two nodes through a component. Every branch has an associated potential (the potential difference

between the two nodes) and flow.

A behavioral description of a conservative component is constructed as a collection of interconnected

branches. The constitutive equations of the component are formulated as to relate the branch potentials and

flows. In the probe/source approach (see 5.4.2

), the branch potential or flow is specified as a function of

branch potentials and flows. If the branch potential and flow are left unspecified, not on the left-hand side of

a contribution statement, then the branch acts as a probe. In this case, if the branch flow is used in an expres-

sion, the branch potential is forced to zero (0). Otherwise the branch flow is assumed to be zero (0) and the

branch potential is available for use in an expression. Using both the potential and flow of a 'probe' branch in

an expression is not allowed. Nor is specifying both the branch potential and flow at the same time. (While

these last two conditions are not really necessary, they do eliminate conditions which are useless and confus-

ing.)

1.3.1.1 Reference nodes

The potential of a single node is given with respect to a reference node. The potential of the reference node,

which is called

ground in electrical systems, is always zero (0). Any net of continuous discipline can be

declared to be

ground. In this case, the node associated with the net shall be the global reference node in the

circuit. This is compatible with all analog disciplines and can be used to bind a port of an instantiated mod-

ule to the reference node.

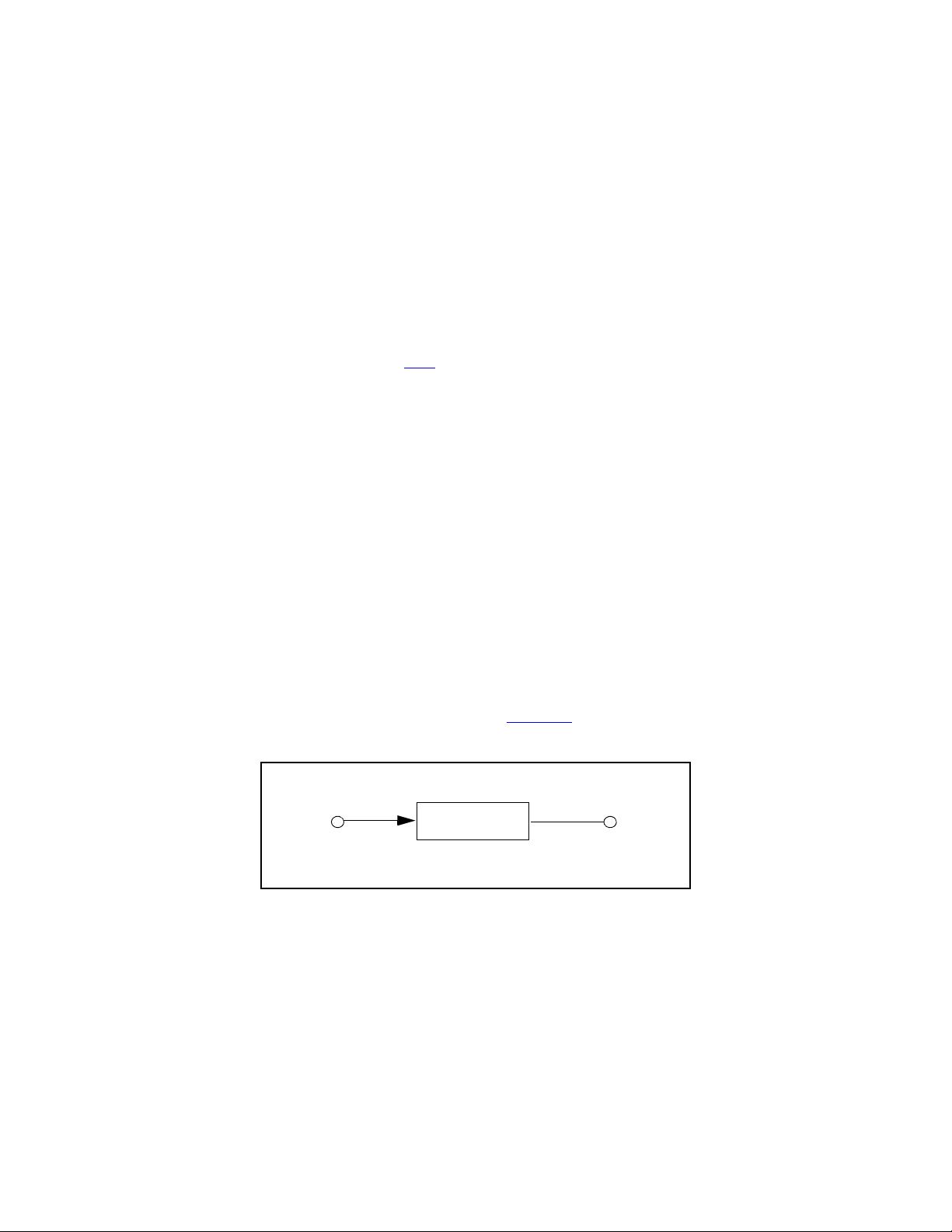

1.3.1.2 Reference directions

The reference directions for a generic branch are shown in Figure 1-2

.

Figure 1-2: Reference directions

The reference direction for a potential is indicated by the plus and minus symbols near each port. Given the

chosen reference direction, the branch potential is positive whenever the potential of the port marked with a

plus sign (

A) is larger than the potential of the port marked with a minus sign (B). Similarly, the flow is pos-

itive whenever it moves in the direction of the arrow (in this case from + to -).

Verilog-AMS HDL uses associated reference directions. A positive flow enters a branch through the port

marked with the plus sign and exits the branch through the port marked with the minus sign.

A

B

flow

+

potential

-