Verilog HDL下的可调参数信号发生器设计

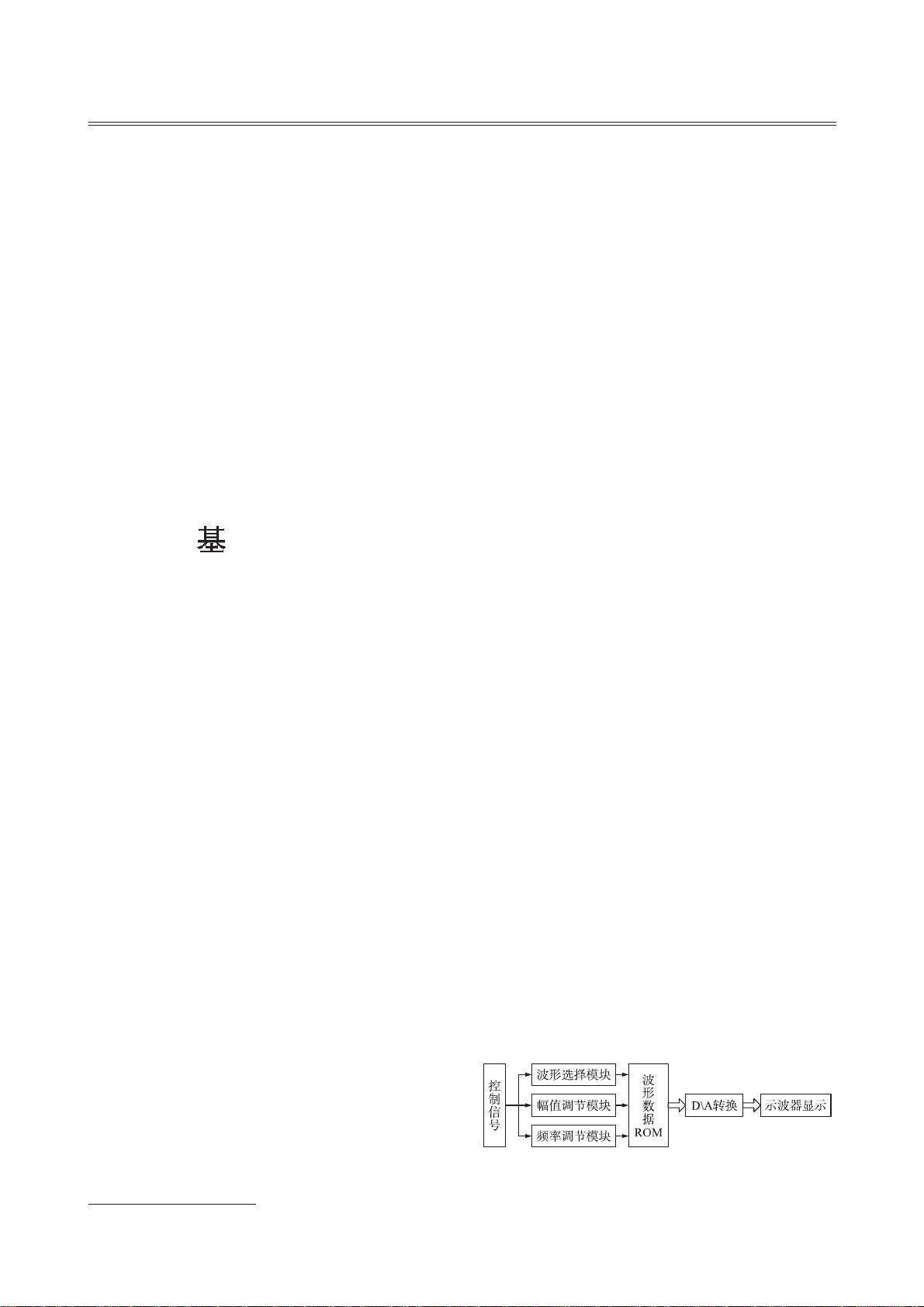

本文档探讨了基于Verilog HDL(硬件描述语言)的信号发生器的设计与实现。Verilog HDL是一种广泛应用于电子设计自动化(EDA)中的高级语言,用于描述数字电路的结构和行为,特别是在现场可编程门阵列(FPGA)和复杂集成电路(ASIC)设计中。作者陈亚军和陈隆道的研究专注于设计一个功能强大的信号发生器,它能够生成包括正弦波、方波、三角波和锯齿波在内的多种波形,并且这些波形的幅度和频率可以根据需要进行动态调整。

在Altera公司的Quartus设计环境中,作者使用Verilog HDL实现了这一设计。这种选择使得设计过程更加高效,因为Verilog提供了模块化和抽象化的特性,使得设计易于维护和扩展。此外,由于其硬件描述性质,该语言允许设计师直接描述硬件组件的行为,从而减少了由软件仿真到实际硬件映射的复杂性,提高了设计的可靠性。

信号发生器的设计不仅注重功能实现,还考虑了用户体验和易用性。通过灵活的Verilog HDL编程,用户能够方便地配置波形参数,适应不同的应用场景需求。当设计完成并下载到FPGA芯片后,实验结果验证了设计的正确性和性能,满足了预期的电路行为。

总结来说,这篇论文介绍了如何利用Verilog HDL进行高效的信号发生器设计,其优势在于简化设计流程、提高设计灵活性以及增强系统的可靠性。这对于嵌入式系统和需要实时信号处理的领域具有实际应用价值。关键词包括嵌入式系统、信号发生器、Verilog硬件描述语言和Quartus设计环境,这表明了研究的重要性和相关技术领域的关注。文章的最终目标是为电子设备设计提供一种实用且高效的解决方案,且得到了国际期刊《电子器件》的认可,发表于2011年10月第34卷第5期。

131 浏览量

459 浏览量

113 浏览量

104 浏览量

2023-06-09 上传

130 浏览量

BOYUAN12

- 粉丝: 1

最新资源

- Android平台DoKV:小巧强大Key-Value管理框架介绍

- Java图书管理系统源码与MySQL的无缝结合

- C语言实现JSON与结构体间的互转功能

- 快速标签插件:将构建信息轻松嵌入Java应用

- kimsoft-jscalendar:多语言、兼容主流浏览器的日历控件

- RxJava实现Android多线程下载与断点续传工具

- 直观示例展示JQuery UI插件强大功能

- Visual Studio代码PPA在Ubuntu中的安装指南

- 电子通信毕业设计必备:元器件与芯片资料大全

- LCD1602显示模块编程入门教程

- MySQL5.5安装教程与界面展示软件下载

- React Redux SweetAlert集成指南:增强交互与API简化

- .NET 2.0实现JSON数据生成与解析教程

- 上海交通大学计算机体系结构精品课件

- VC++开发的屏幕键盘工具与源码解析

- Android高效多线程图片下载与缓存解决方案