Development of Through Silicon Via (TSV) Interposer for

Memory Module Flip Chip Package

Nicholas Kao, Eason Chen, Daniel Lee, Mike Ma

Advanced Product Design & Testing Dept. Corporate R & D, Siliconware Precision Industries Co. Ltd.

No. 123, Sec. 3, Da Fong Rd, Tantzu, Taichung 42749, Taiwan, R.O.C.

Email: nicholas@spil.com.tw

Tel: 886-4-25341525 ext 7941

Abstract

With the trend of microelectronics packaging toward

more functionality, high performance and smaller form

factor, the product is required to deliver more I/Os and better

electrical characteristics under a minimum module system.

Therefore, a 3D IC integration System in Package (SiP) with

passive Through Silicon Via (TSV) interposer technology is

proposed to provide high density and heterogeneous

integration needed for such requirement.

Due to the Coefficients of Thermal Expansion (CTE)

mismatch between materials, thermal-mechanical stress and

warpage are induced during Through Silicon Interposer (TSI)

fabrication process, which may affect TSV crack or

Controlled Collapse Chip Connection (C4) bump crack after

TSI bonding to organic substrate process. Therefore, this

work is a step by step process simulation with various design

parameters by finite element method (FEM) to investigate

stress and warpage behaviors of processing effect. For both

full array dummy bumps layout and thinner top chips are to

reduce micro-bump stress. Also, low CTE organic substrate

core, high CTE mold compound and thinner top chips

perform lower package warpage. Finally, this paper aims to

provide a guideline to designer for 3D IC integration SiP

with passive TSV interposer structure by using the finite

element models.

Introduction

As the demands of more functionality and high

performance, the product is required to deliver more I/Os and

better electrical characteristics. Therefore, a 3D IC

integration package with TSI technology is proposed to

provide high density and heterogeneous integration needed

for such requirement. Functional chips stacked on a TSI then

assembled on an organic substrate is as test vehicle (See

Figure-1). The electrical connection between functional chips

to TSI is through micro-bumps and Re-Distribution Layer

(RDL) then is going to the TSV of TSI. TSI and organic

substrate interconnect is by C4 bumps. Due to the CTE

mismatch between materials, thermal-mechanical stress and

warpage are induced during TSI fabrication and package

assembly process, which may affect TSV crack or C4 bump

crack after top chips bonding to TSI and TSI bonding to

organic substrate processes.

Firstly, the design parameters including RDL design, TSI

thickness, bump layout, top chip thickness and DRAM chips

space are discussed in detail. The key challenge during

assembly process is chip level warpage contribution to cause

solder bump non-wetting or bridge issue. From simulation

result, a balanced RDL Cu coverage design is effective to

reduce TSI warpage. In addition, thinner top chip thickness

with full array dummy bump layout performs lower micro-

bump stress. Secondly, the underfill, mold compound and

organic substrate core material selection are also included in

this paper. In assembly flow, top chips are assembled on TSI

and filled the micro-bump gap with underfill, then entire

package and C4 bump gap are filled with mold compound.

The simulation indicated that low CTE core and high CTE

compound are effective to reduce package warpage. Finally,

this paper aims to provide a guideline to designer for 3D IC

integration SiP with passive TSV interposer structure by

using the finite element models.

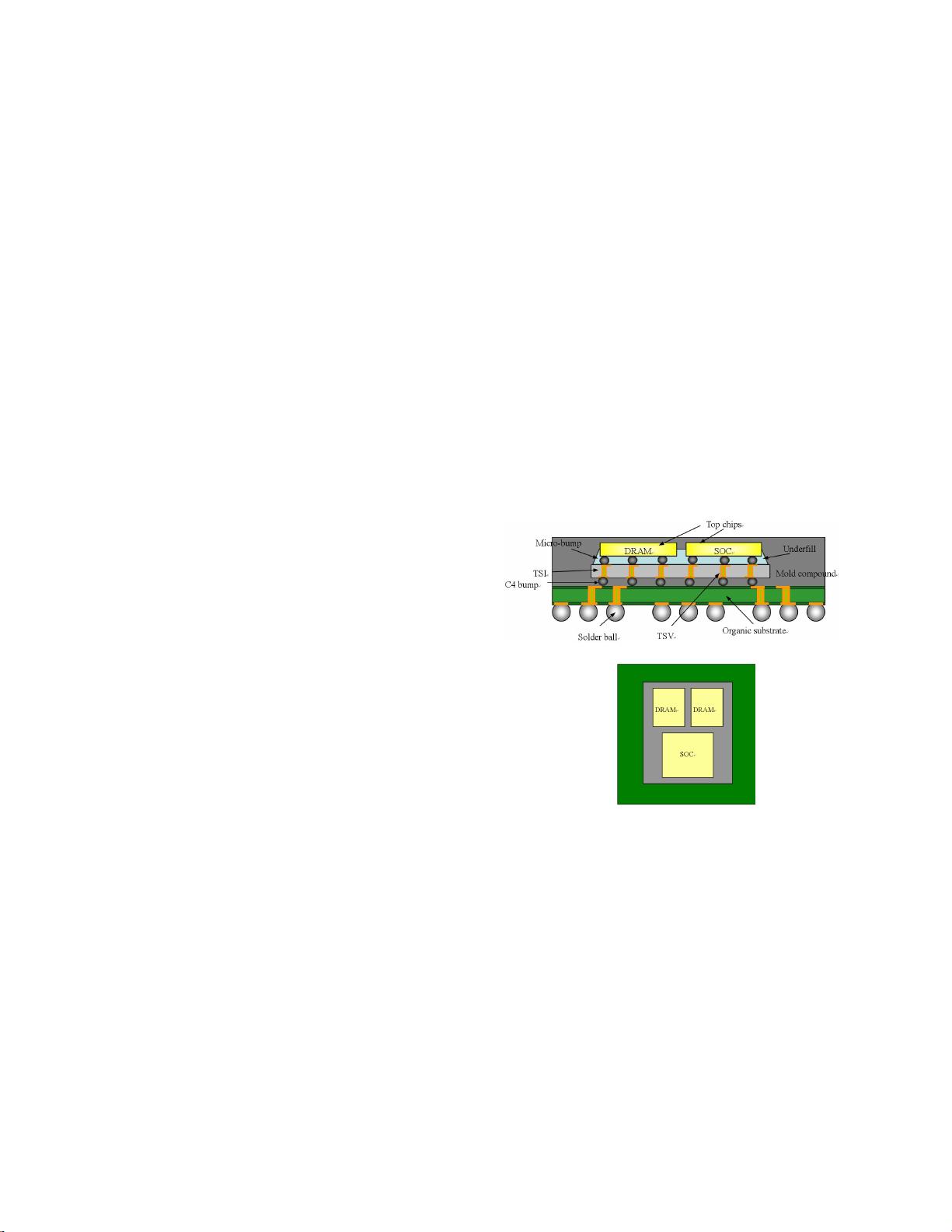

(a)

(b)

Figure-1: 3D FCCSP test vehicle. (a) side view (b) top view.

Test Vehicle

Figure-1 shows a multi-chip stacked 3D-FCCSP test

vehicle used in this paper. This structure consists of three top

chips with lead free micro-bumps and a bottom TSI with lead

free C4 bumps. Top chips include two DRAM chips and one

SOC chip with the size of 7.74mm 6.24mm and 6.98mm

6.73mm, respectively. They were stacked on a TSI with the

size of 16.0mm 14.6mm. Then, underfill was filled into the

gap between top chips and TSI which is around micro-

bumps. After chip to chip stacking process, it was stacked on

an organic substrate and jointed by C4 bumps. The entire

package and C4 bump gap was filled with mold compound.

Detail package size and dimension are summarized in Table-

1.