没有合适的资源?快使用搜索试试~ 我知道了~

首页计算机系统详解:硬件组成与性能指标

计算机系统详解:硬件组成与性能指标

需积分: 3 1 下载量 47 浏览量

更新于2024-07-23

收藏 1.01MB DOCX 举报

计算机系统知识大纲深入探讨了计算机硬件与软件交互的核心原理,以及它们在现代信息技术中的关键作用。该大纲首先从计算机的硬件组成出发,介绍了基本的硬件框图,包括输入设备(如键盘和鼠标)、输出设备(如显示器和打印机)、高速缓存(Cache)、主存储器(如RAM)、辅助存储器(如硬盘)、运算器(处理算术和逻辑运算的部件ALU),以及控制器(负责解析和执行指令的部件)。总线结构被强调,它作为一个公共信息传输平台,优化了系统扩展性和灵活性。 在大型和中型计算机系统中,接口设计更为复杂,通常分为主机、通道、设备控制器和外部设备四级。这展示了计算机硬件系统的层次结构,从最底层的物理组件到更抽象的软件层次,如微程序级、传统机器级、操作系统级、汇编语言级和高级语言级。这种多层架构使得软件的移植和兼容成为可能。 工作过程方面,程序首先加载到主存储器,由控制器按指令顺序执行,体现了计算机的执行逻辑。衡量计算机性能的关键指标包括机器字长(决定计算精度)、数据通道宽度(数据传输能力)、主存容量(存储空间大小)和运算速度(如平均运算速率、指令周期、MIPS和MFLOPS等)。 数据信息的表示也十分重要,涉及到进位计数制(如二进制、八进制和十六进制)以及数值数据的编码方式,如无符号数、带符号数的原码、补码和反码表示。此外,还讨论了定点数和浮点数的表示方法,例如定点小数和定点整数的表示范围,这对于理解和设计高效的数据处理算法至关重要。 这个大纲覆盖了从计算机硬件基础到数据处理和性能评估的广泛内容,为理解和构建计算机系统提供了全面的知识框架。

资源详情

资源推荐

2. 数据校验码的码距:任意两个码字之间最少变化的二进制位数;

3. 码距越大,检、纠错能力就越强,而且检错能力总是大于或等于纠错能力。

4. 奇偶校验码:码距为 2,可以检测出一位错误(或奇数位错误),但不能定位出错的位

置,也不能检测出偶数位错误。用于存储器读、写检查或 ASCII 字符传送过程中的检查。

5. 海明校验码:主存的 ECC 采用这类校验码。多重奇偶校验,在有效信息位中加入几个校

验位行程海明码,使码距比较均匀地拉大,并把海明码的每一个二进制位分配到几个奇偶

校验组中。能够指出错误的位置,为自动纠错提供依据。2

k-1

≥N+K+1;

6. 循环冗余校验码:计算机网络、同步通信以及磁表面存储器中广泛使用 CRC 码;假设,

待编码的有效信息以多项式 M(X)表示,将它左移若干位后,用另一个约定的多项式 G(X)去

除,所产生的余数 R(X)就是检验位。有效信息和检验位相拼接就构成了 CRC 码。当整个

CRC 码被接收后,仍用约定的多项式 G(X)去除,若余数为 0 表明该代码是正确的;若余数

不为 0 表明某一位出错,再进一步由余数值确定出错的位置,以便进行纠正。

7. 循环冗余校验码编码方法:信息位 N 位,校验位 K 位,校验码为(N+K,N)码。

第三节 计算机中的逻辑部件

一、 组合逻辑电路

1. 编码器:m 个输入端和 n 个输出端,输出的是二进制编码值。M≤2

N

1) 二进制编码器:全编码器,输入信号 m=2

n

,输出信号位数 n;

2) 二 - 十进制编码器:0~9 用四位二进制代码来表示的电路,m=10,n=4,部分编码;

3) 优先编码器:只对其中优先级最好的输入进行编码,8 线-3 线优先编码器;

2. 译码器:解码器,编码的逆过程;n 个输入端,m 个输出端,2

n

≥m;根据逻辑功能的

不同,分为通用译码器和显示译码器。

3. 数据选择器与数据分配器:

1) 数据选择器:多路选择器,MUX,多个输入、一个输出,能在选择信号的作用下,

从多个输入中选择某一个送到输出端。

2) 数据分配器:一个输入端、多个输出端,将一个输入端的信号送至多个输出端中的

某一个,DMUX;带有使能端的全译码器;

4. 时序逻辑电路:不仅与输入输出有关,还与该时刻电路的状态有关;必须包含具有记

忆功能的电子器件——触发器;触发器和一些控制门可以组成寄存器、移位寄存器、

计数器等基本的时序逻辑电路。

1) 寄存器:接收、寄存或传送信息,并行输入 -并行输出方式,一个触发器仅能寄存

一位二进制代码

2) 计数器:累计输入脉冲的个数,可以用来计数、定时、分频;

3) 异步计数器:没有公共的时钟脉冲,串行计数器;

4) 同步计数器:各个触发器的时钟脉冲均来自于同一个计数输入脉冲,并行计数器;

5. 总线电路:小型、微型机的典型结构,使用较小的硬件代价组成具有较强功能的系统;

1) 三态门:三种逻辑状态,0、1、浮空状态;

2) 单向和双向总线电路:单向:总线信息智能向一个方向传送(地址总线);双向:

数据总线;

6. 可编辑逻辑器件(PLD):用户通过编程手段使芯片产生一定的逻辑功能的器件

1) 专用集成电路:标准集成电路和用户定制电路。

第四节 指令系统

一、 指令:计算机执行某些操作的命令;指令系统:指令的集合,主要位于硬件和软

件的交界面上;

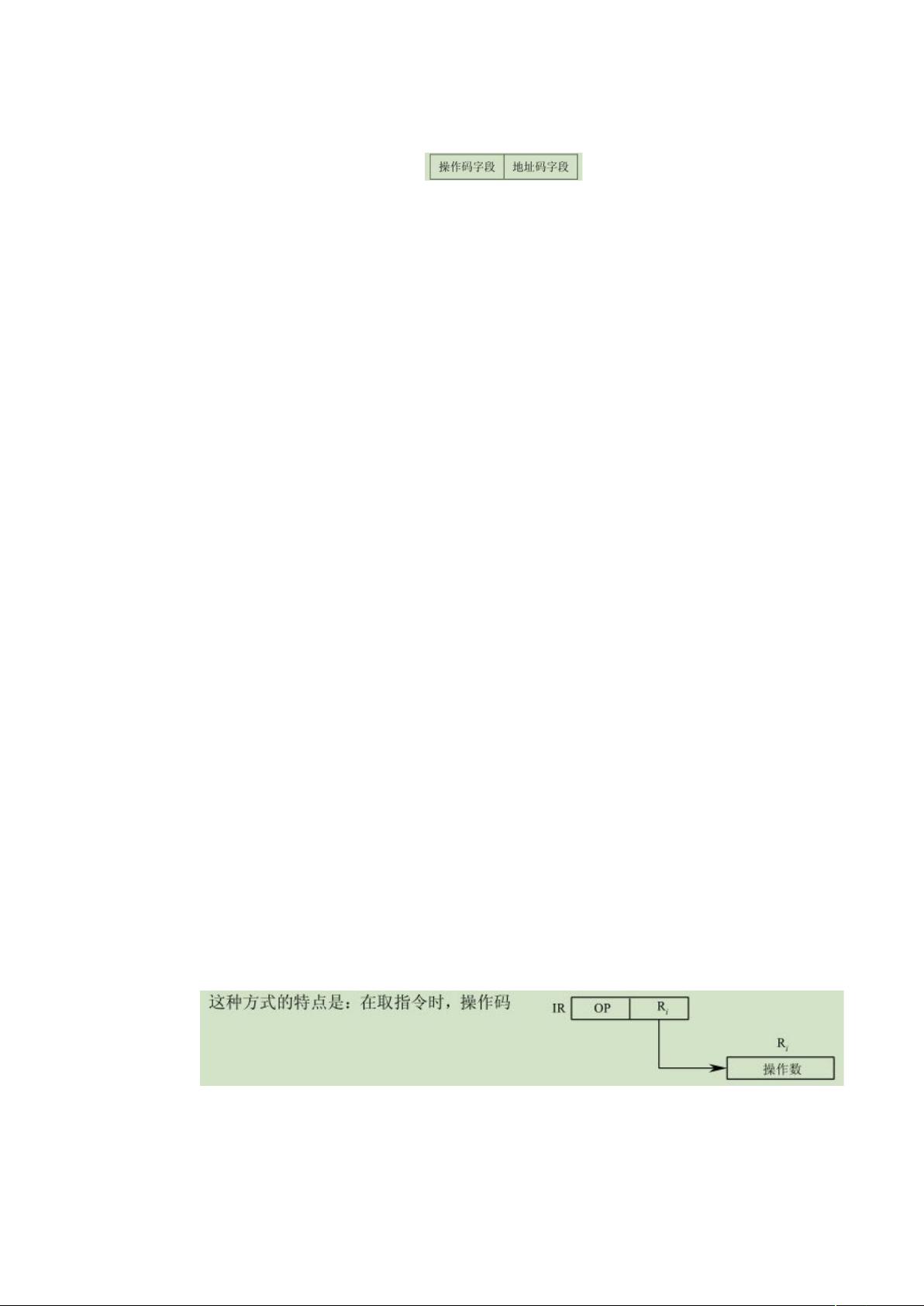

二、指令格式:有意义的二进制代码。 ;操作码指明了指令的操作

性质及功能,地址码则给出了操作数的地址。

1)指令的长度:包含的二进制代码的位数;

2)指令长度准则:指令长度应尽可能短;指令长度应等于字节的整数倍;

四、 指令的地址码结构:

1) 四地址指令:操作码 OP;OP|A

1

|A

2

|A

3

|A

4

;指令含义:(A

1

)OP(A

2

)→A

3

,A

4

=下条将

要执行指令的地址;

2) 三地址 指令: 用程序 计数 器 PC 来存放指令 地 址 ;OP|A

1

|A

2

|A

3

;指令 含 义 :

(A

1

)OP(A

2

)→A

3

,(PC)+1→PC(隐含);

3) 二地址指令:让第一操作数地址同时兼存放结果的地址; OP|A

1

|A

2

;指令含义:

(A

1

)OP(A

2

)→A

1

,(PC)+1→PC(隐含);

4) 一地址指令:隐含的操作数存放在一个专门的寄存器中,保存着多条指令连续操

作的累计结果,故称为累加寄存器 Acc;(Acc) OP(A

1

) →Acc;(PC)+1→PC(隐含);

5) 零地址指令:只有操作码字段,没有地址码字段,格式为:OP;用在堆栈计算机

中

五、 指令的操作码:每一条指令都有一个唯一确定的操作码;

1) 规整型(定长编码)

2) 非规整型(变长编码)

六、 寻址技术:寻找操作数的地址或下一条将要执行的指令地址;

1) 编址方式:字编址(与访问单位一致,每个编址单位所包含的就信息量<二进制位

数>与访问一次寄存器、主存所获得的信息量相同,每执行一条指令,程序计数器

PC+1,每从主存中读出一个数据,地址计数器+1)、节编址(为了适应非数值应

用的需要,编址单位与信息的基本单位相一致)、位编址(地址信息浪费更大);

2) 指令中地址码的位数:每个地址码的位数与主存容量和最小寻址单位(编址单

位)有关,主存容量越大,所需的地址码位数越长。

3) 数据寻址(寻找操作数的地址)和指令寻址(寻找下一条将要执行的指令地址);

指令寻址又可细分为顺序寻址(程序计数器 PC+1)和跳跃寻址(程序转移类指令:

直接、相对、间接)

4) 基本的数据寻址方式:根据指令中给出的地址码字段寻找真实操作数地址的方式。

指令中地址码字段给出的地址成为形式地址(A),可能不能直接访问主存,形式

地址通过某种运算得到的能够访问主存的地址称为有效地址( EA);从形式地址

生成有效地址的各种方式称为寻址方式;

1. 立即寻址:操作数本身,只要取出指令就去除了可以立即使用的操作数 OP|立

即数:

2. 寄存器寻址:给出某一个通用寄存器的编号,这个指定的寄存器中存放操作数,

IR 表示存放指令的寄存器,操作数 S 与寄存器 R

i

的关系为:S=(R

i

);

3. 直接寻址:地址 A 就是操作数的有效地址,EA=A,操作数地址不能修改;

4. 寄存器间寻址法:地址码给出某一通用寄存器的编码,被指定的寄存器中存放

剩余25页未读,继续阅读

luckyyouyou2004

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 十种常见电感线圈电感量计算公式详解

- 军用车辆:CAN总线的集成与优势

- CAN总线在汽车智能换档系统中的作用与实现

- CAN总线数据超载问题及解决策略

- 汽车车身系统CAN总线设计与应用

- SAP企业需求深度剖析:财务会计与供应链的关键流程与改进策略

- CAN总线在发动机电控系统中的通信设计实践

- Spring与iBATIS整合:快速开发与比较分析

- CAN总线驱动的整车管理系统硬件设计详解

- CAN总线通讯智能节点设计与实现

- DSP实现电动汽车CAN总线通讯技术

- CAN协议网关设计:自动位速率检测与互连

- Xcode免证书调试iPad程序开发指南

- 分布式数据库查询优化算法探讨

- Win7安装VC++6.0完全指南:解决兼容性与Office冲突

- MFC实现学生信息管理系统:登录与数据库操作

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功