CPLD/FPGA实现:16×16字符发生器设计

需积分: 10 139 浏览量

更新于2024-08-02

收藏 985KB DOC 举报

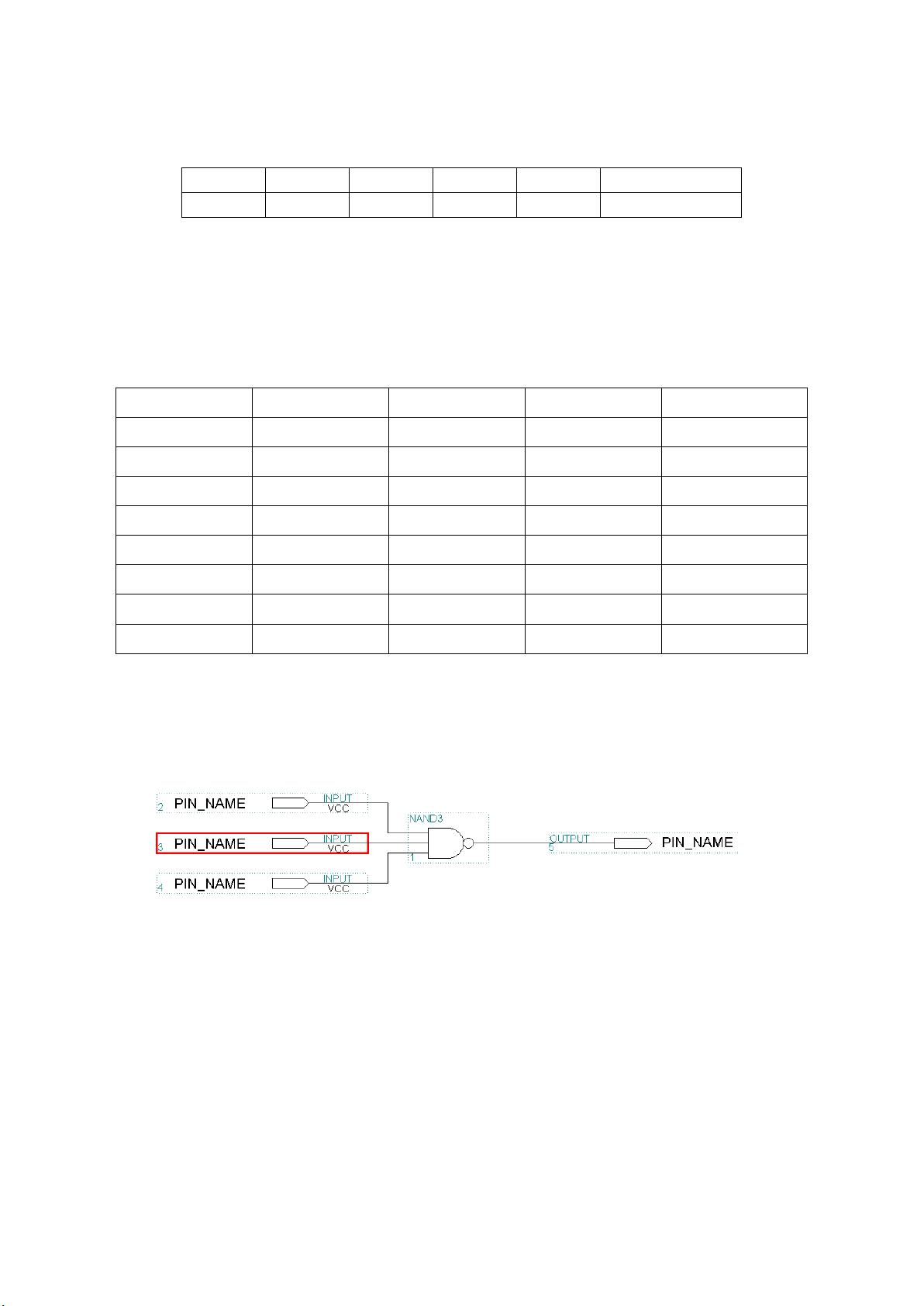

"该资源是一个关于电子技术课程设计的项目,主要目标是设计一个16×16字符发生器,使用MAX+PLUS11工具完成。设计内容包括理解点阵字符的产生和显示原理,了解ROM和16×16点阵LED的工作机理,并通过CPLD/FPGA芯片实现ROM的地址和读信号生成,以及扫描驱动电路。设计任务是稳定清晰地显示“太原科技大学”六个字符。设计分为三个部分:八进制计数器、ROM259×8和ADDRESS1。八进制计数器提供地址,ROM存储字符数据,ADDRESS1负责正确地将数据写入16×16点阵LED上。"

在这个电子技术课程设计中,学生们将深入学习以下几个核心知识点:

1. 点阵字符的产生与显示原理:点阵字符是通过点亮特定的LED矩阵来形成字符图形,通常使用行扫描和列驱动的方式实现。在这个设计中,16×16点阵意味着每个字符由16行和16列的LED组成,通过控制每一行和每一列的亮灭来显示字符。

2. ROM(Read-Only Memory)工作机理:ROM是一种非易失性存储器,用于存储固定不变的数据,如字符代码。在字符发生器中,ROM用于存储“太原科技大学”六个字符的点阵数据,这些数据在特定地址被读取后,送到扫描驱动电路。

3. CPLD/FPGA芯片的应用:复杂可编程逻辑器件(CPLD)或现场可编程门阵列(FPGA)用于生成ROM的地址和读取信号。这些器件具有高度的灵活性,可以根据设计需求配置内部逻辑,实现地址产生和控制信号的生成。

4. 总线系统:在设计中,总线用于传输地址、数据和控制信号。理解如何生成和抵定制定位的EPLD(可编程逻辑设备)是设计的关键部分,因为它决定了数据在系统中的流动路径。

5. 计数器设计:74LS160是一个十进制计数器,通过修改其内部逻辑,可以将其转变为八进制计数器,产生0-7的循环地址,用以驱动ROM的地址线。

6. 扫描驱动电路:电路包括高低位驱动输出HOUT0-7和LOUT0-7,它们与16×16点阵LED的行和列连接,随着地址计数器的计数值变化,实现逐行扫描显示字符。

7. 地址映射与读写操作:理解如何根据字符位置映射对应的ROM地址,并编写读写过程信号,以确保正确地从ROM读取数据并在LED点阵上显示。

8. 系统集成:将上述各部分集成到一个完整的设计中,需要考虑时序控制、复位功能以及信号同步,以确保字符稳定清晰地显示。

9. 硬件描述语言(HDL)编程:使用MAX+PLUS11工具,学生需要掌握HDL语言,如VHDL或Verilog,来描述和实现数字逻辑设计。

10. 实际操作与调试:实际操作中,学生会学习如何在硬件平台上验证设计,包括电路搭建、程序下载、故障排查等。

这个课程设计项目不仅锻炼了学生的理论知识,也提升了他们的实践能力和问题解决技巧,是一次全面的电子技术学习体验。

点击了解资源详情

277 浏览量

点击了解资源详情

237 浏览量

2011-12-08 上传

278 浏览量

428 浏览量

2009-12-02 上传

484 浏览量

kuaikuaixia

- 粉丝: 0

- 资源: 1

最新资源

- LucenceInActionCH

- 动态视位模型及其参数估计

- 计算机等级考试三级网络题集

- [70-549] 70-549 MCPD Training Kit.pdf

- ActionScript3.0 Design Patterns

- 关于交换网络故障的全面分析排除实战

- D 语言编程参考手册 2.0

- javascript语言精髓与编程实践

- 画pcb图的经验所得

- 分治分治法及其应用,具体说明如何进行分治

- 03.漫谈兼容内核之三:关于kernel-win32的文件操作

- 漫谈兼容内核之二:关于kernel-win32的对象管理

- C#完全手册 C#入门教程

- 漫谈兼容内核之一:ReactOS怎样实现系统调用

- JSP技术的详细简介

- Windows驱动开发笔记