Verilog异步FIFO设计与调试总结

需积分: 50 53 浏览量

更新于2024-09-01

收藏 3.2MB DOCX 举报

异步FIFO框图及程序调试总结

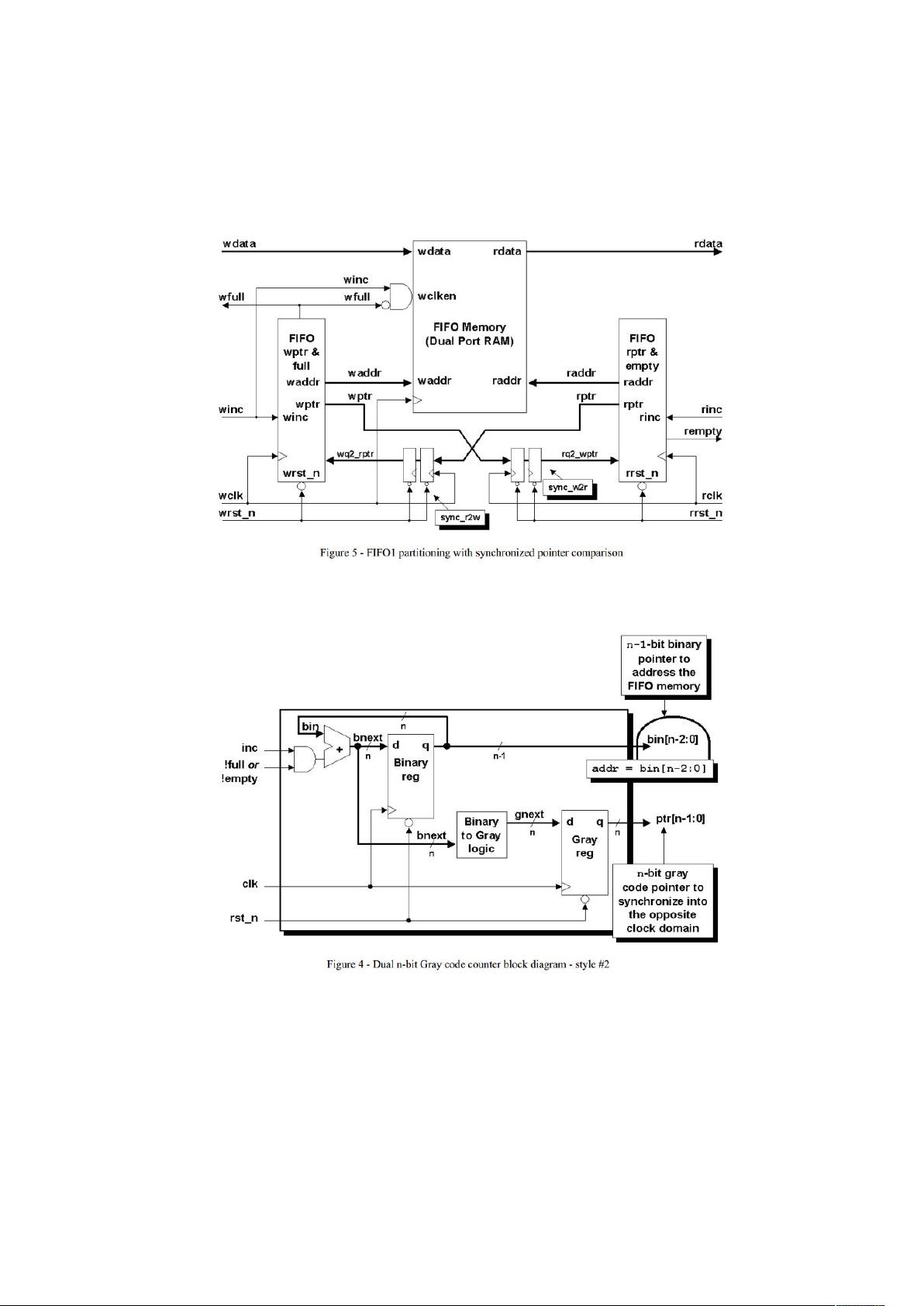

异步FIFO是一种常用的数字电路设计技术,用于实现数据的存储和传输。在 Verilog 中,异步FIFO的设计需要考虑到框图的设计、代码的编写和调试等多方面的内容。

**异步FIFO框图设计**

异步FIFO的框图设计是指整个系统的结构设计,包括读取地址和用于空满判断的格雷码的生成逻辑框图。这种框图设计需要考虑到系统的总体架构、信号流和数据传输的过程。

**代码调试过程中的问题和解决方法**

在代码调试过程中,可能会出现一些问题,例如:

1. 更改代码名称时未改全信号名称,解决方法是将所有相关的信号名称都进行修改。

2. 信号声明时应该在声明端口类型(input/output/…)时应该将线型(reg/wire/…)和位宽一起声明,否则nLint将出现重复定义的报错信息。

3. 后面添加的代码中未对新加入的信号进行定义声明,解决方法是对新加入的信号进行定义声明。

4. 顶层例化模块时名称位置写反,解决方法是将源名称和用户自己定义的名称写在正确的位置。

5. 模块名称应和代码文件名称相对应,解决方法是将模块名称和代码文件名称保持一致。

6. Verilog运算符(如&&===~!)和特定的模块(如mem)定义方法不清晰,不准确,解决方法是熟练掌握Verilog语言的基本语法和运算符。

7. 信号参数概念和定义及其计算方法不明确,解决方法是了解信号参数的概念和定义,并掌握其计算方法。

8. Verilog中定义的mem:reg[31:0]memFile[63:0]指的是声明一个memory类型的变量memFile,位宽为32,深度为64,即定义一个有64个32位寄存器的存储器mem。

9. Always时序语句中可以出现逻辑赋值,如(rempty<=(a&&b)),解决方法是熟练掌握Always语句的使用。

10. 模块端口未连接,解决方法是查看verdi中的逻辑图,检查模块端口的连接情况。

**信号和端口类型**

在 Verilog 中,信号和端口类型是非常重要的概念。输入端口可以由wire/reg驱动,但输入端口只能是wire;输出端口可以使wire/reg类型,输出端口只能驱动wire。模块间连线可用wire定义。

**时钟域不同时的注意事项**

在时钟域不同时,要注意先同步,同步过程中需要注意各个信号同步过程中的时钟驱动信号。

**模块间的连接**

模块间的连接需要注意端口名称尽量相同,避免出现连接错误。

**其他注意事项**

在编写Verilog代码时,需要注意代码的可读性和维护性,避免出现代码的错误和 Bug。同时,需要熟练掌握Verilog语言的基本语法和运算符,避免出现语法错误。

**异步FIFO的应用**

异步FIFO的应用非常广泛,例如在数字电路设计、数据存储和传输等领域。异步FIFO的设计需要考虑到系统的总体架构、信号流和数据传输的过程。

异步FIFO框图及程序调试总结是非常重要的技术知识,需要熟练掌握Verilog语言的基本语法和运算符,避免出现代码的错误和 Bug,同时需要注意信号和端口类型、时钟域不同时的注意事项等问题。

2019-05-04 上传

2021-11-19 上传

2023-03-01 上传

2022-06-27 上传

2021-06-05 上传

2021-07-13 上传

qq_41922833

- 粉丝: 26

- 资源: 4

最新资源

- 逻辑分析仪使用手册特备版

- C语言测试-想成为嵌入式程序员应知道的0x10个基本问题.doc

- ASP考试系统理论指导

- PSoC的动态配置能力及其实现方法

- java面试题集(100题)

- 马潮老师AVR新书《AVR单片机嵌入式系统原理与应用实践》.

- 程序员面试好东西 JAVA

- AIX 逻辑卷管理

- 在Linux世界驰骋系列之Shell编程

- 直流电源及数显电路的设计

- OSWorkflow中文手册.pdf

- OSWorkflow开发指南.pdf

- Webwork2 开发指南.pdf

- Bootloader+Source+Code+Modification+Guide.pdf

- Hibernate开发指南.pdf

- 华为编程规范——规范你的程序设计