The Virtualization Module of the MIPS64® Architecture

16 MIPS64® Architecture for Programmers Volume IV-i: Virtualization Module of the MIPS64® Architecture, Revision 1.06

Copyright © 2010-2012 MIPS Technologies Inc. All rights reserved.

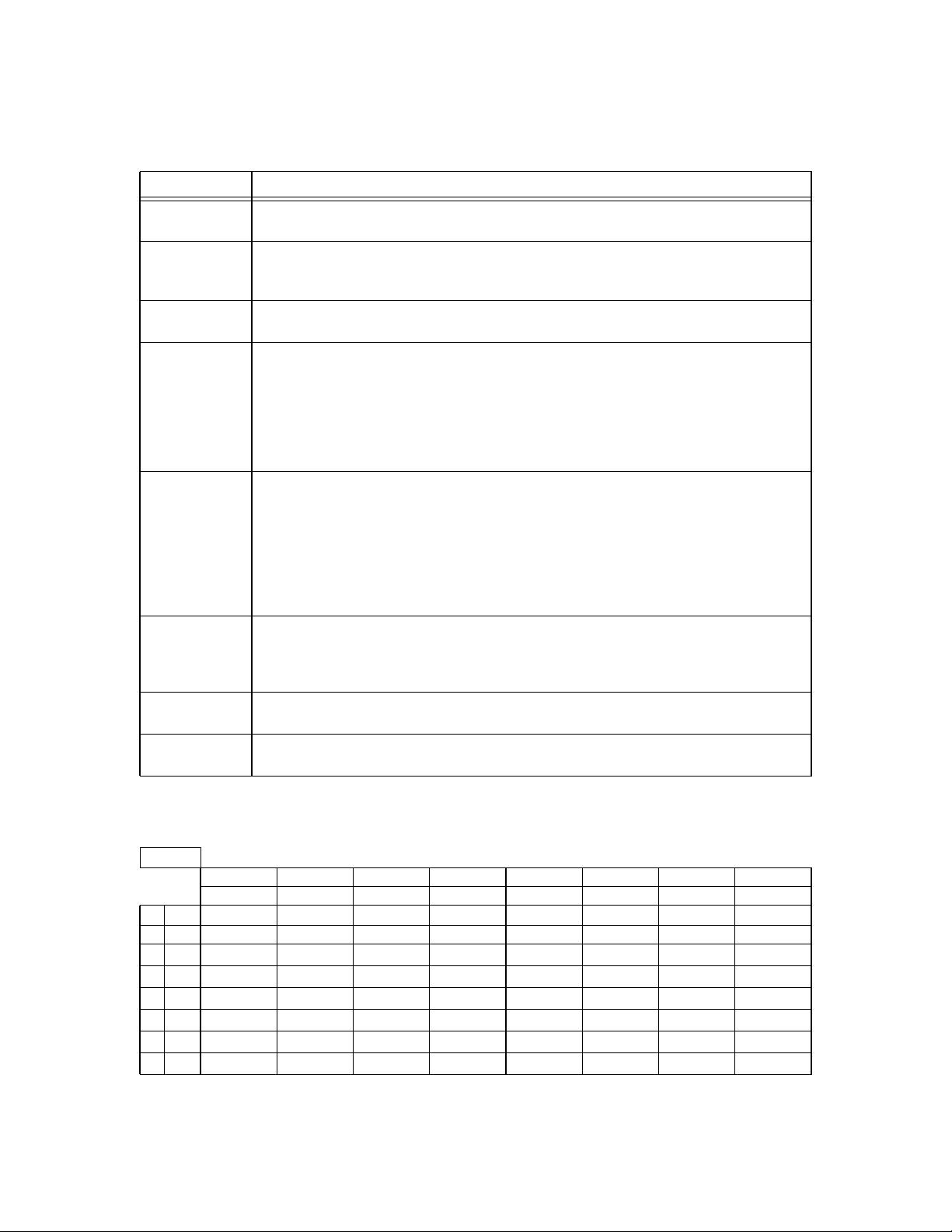

Table 2.1 Symbols Used in the Instruction Encoding Tables

Symbol Meaning

∗ Operation or field codes marked with this symbol are reserved for future use. Executing such an

instruction must cause a Reserved Instruction Exception.

δ (Also italic field name.) Operation or field codes marked with this symbol denotes a field class.

The instruction word must be further decoded by examining additional tables that show values for

another instruction field.

β Operation or field codes marked with this symbol represent a valid encoding for a higher-order

MIPS ISA level. Executing such an instruction must cause a Reserved Instruction Exception.

⊥ Operation or field codes marked with this symbol represent instructions which are not legal if the

processor is configured to be backward compatible with MIPS

64 processors. If the processor is

executing in Kernel Mode, Debug Mode, or 64-bit instructions are enabled, execution proceeds

normally. In other cases, executing such an instruction must cause a Reserved Instruction Excep-

tion (non-coprocessor encodings or coprocessor instruction encodings for a coprocessor to which

access is allowed) or a Coprocessor Unusable Exception (coprocessor instruction encodings for a

coprocessor to which access is not allowed).

θ Operation or field codes marked with this symbol are available to licensed MIPS partners. To avoid

multiple conflicting instruction definitions, MIPS Technologies will assist the partner in selecting

appropriate encodings if requested by the partner. The partner is not required to consult with MIPS

Technologies when one of these encodings is used. If no instruction is encoded with this value,

executing such an instruction must cause a Reserved Instruction Exception (SPECIAL2 encodings

or coprocessor instruction encodings for a coprocessor to which access is allowed) or a Coproces-

sor Unusable Exception (coprocessor instruction encodings for a coprocessor to which access is

not allowed).

σ Field codes marked with this symbol represent an EJTAG support instruction and implementation

of this encoding is optional for each implementation. If the encoding is not implemented, execut-

ing such an instruction must cause a Reserved Instruction Exception. If the encoding is imple-

mented, it must match the instruction encoding as shown in the table.

ε Operation or field codes marked with this symbol are reserved for MIPS Modules. If the Module is

not implemented, executing such an instruction must cause a Reserved Instruction Exception.

φ Operation or field codes marked with this symbol are obsolete and will be removed from a future

revision of the MIPS64 ISA. Software should avoid using these operation or field codes.

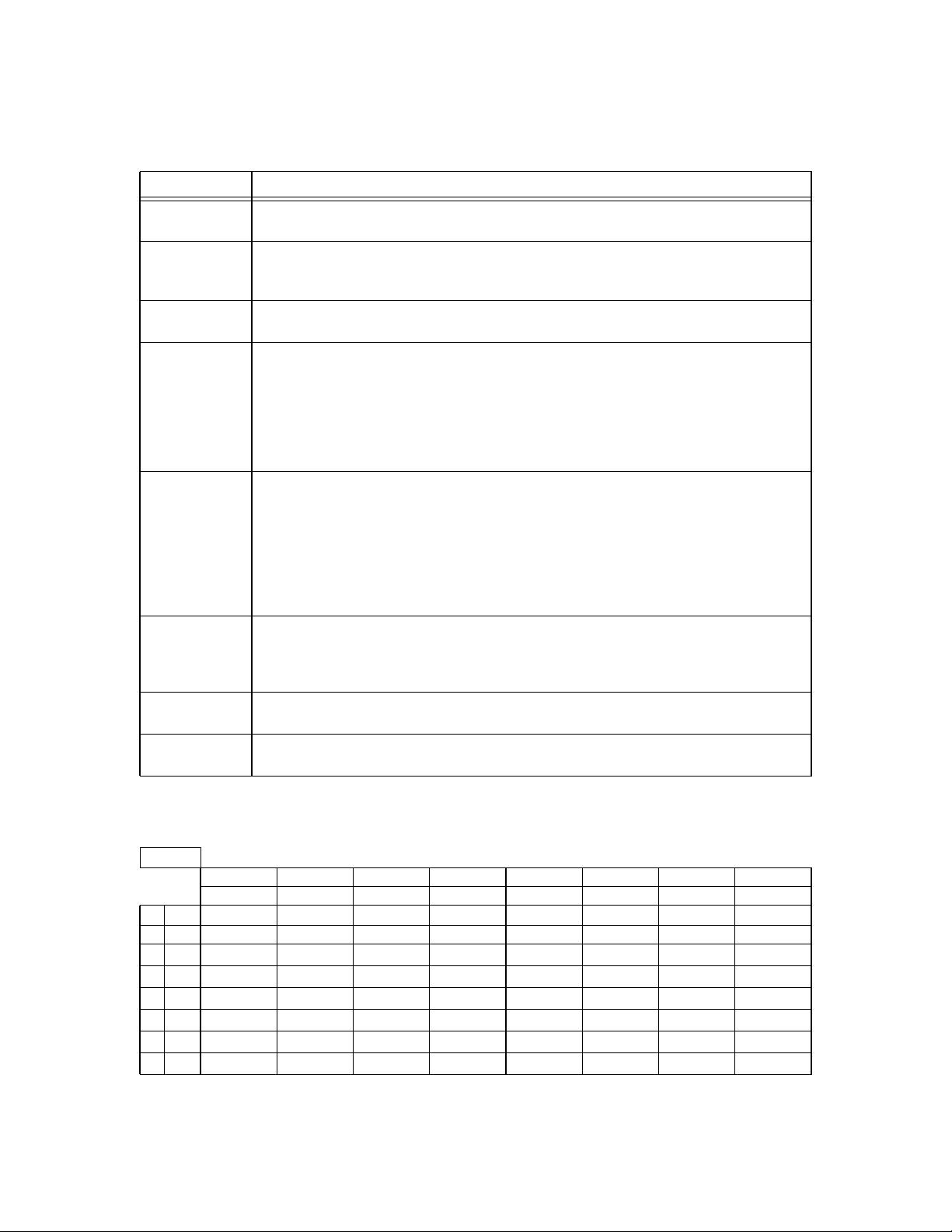

Table 2.2 Virtualization Module Encoding of the Opcode Field

opcode bits 28..26

01234567

bits 31..29 000 001 010 011 100 101 110 111

0 000

1 001

2 010 COP0 δ

3 011

4 100

5 101

6 110

7 111

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功