STM32F4xx GPIO与DMA实现同步串行传输教程

需积分: 3 98 浏览量

更新于2024-07-17

收藏 1.2MB PDF 举报

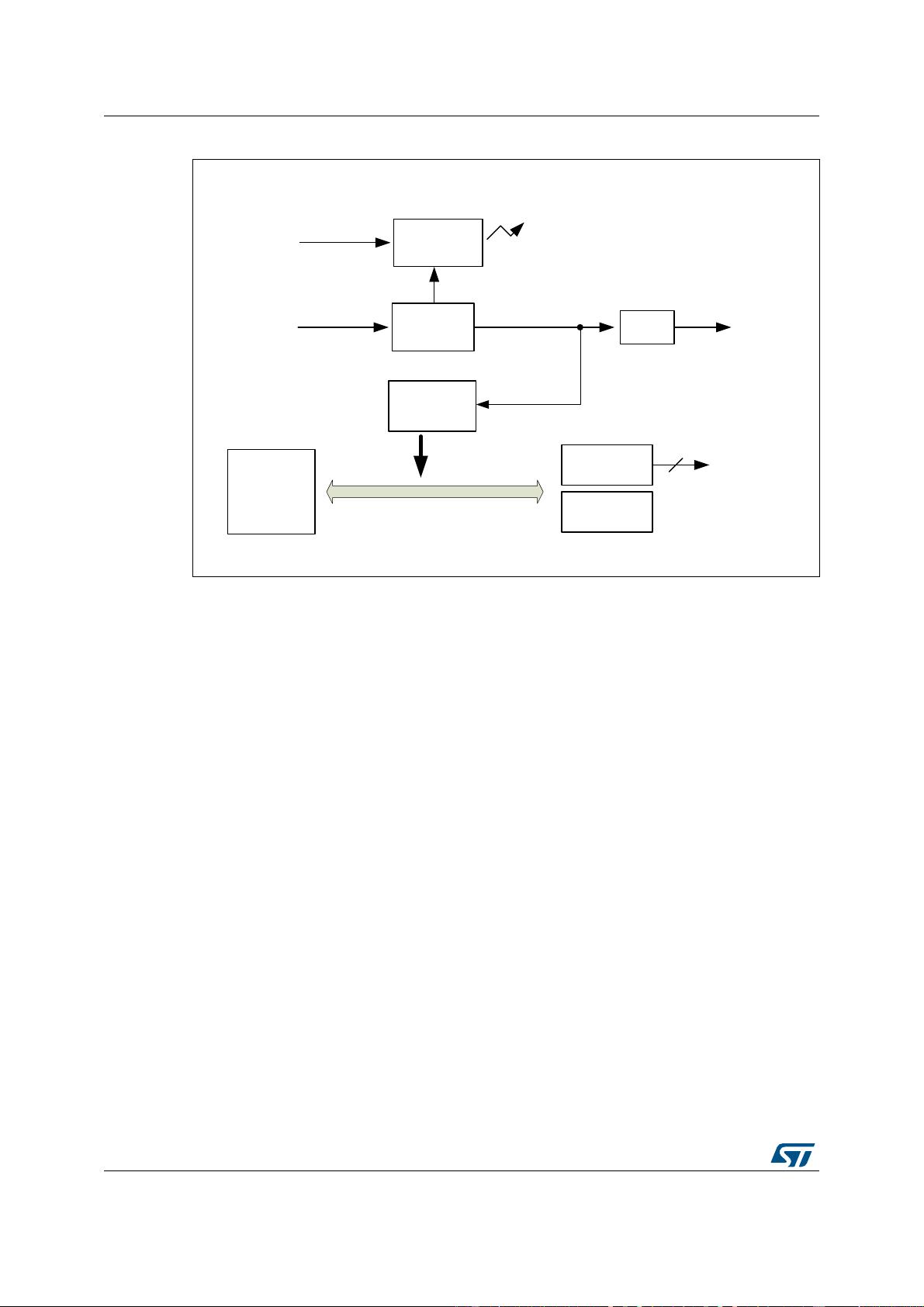

本应用笔记主要介绍了STM32微控制器如何通过通用输入/输出(GPIO)接口和嵌入式直接存储器访问(DMA)实现并行同步传输。2016年1月发布的文档(DocID027642Rev1)详细阐述了这一技术,适用于STM32F4xx系列芯片。该技术允许数据帧传输最多16位数据,同时配备一个异步数据时钟。为了进行有效的数据传输,需要用到定时器来产生数据时钟并控制传输时间和发送的数据量。

STM32微控制器可能具备不同的内置特性,如带有或不带双缓冲模式的DMA,以及具有或没有FIFO功能。此外,所使用的开发板可能包含外部存储器(如SDRAM),硬件配置的不同会影响并行同步通信的实现方式以及性能表现,比如最大数据帧长度和传输频率。本应用笔记特别关注了两种不同类型的STM32微控制器(可能是STM32L476G Discovery板,其DMA不具备双缓冲模式)和发现板,以此来展示硬件差异对设计和性能的影响,并探讨了两种可能的架构实现:

1. STM32L476G Discovery板:由于缺乏DMA的双缓冲模式,可能需要采用不同的策略来管理数据流,这可能会对传输效率有所影响。开发者需要根据此硬件特性调整代码,确保在没有这种高级功能的情况下仍能实现并行同步传输。

2. 具有双缓冲DMA的STM32版本:在这种情况下,可以利用双缓冲的优势,提高数据传输的连续性和性能。双缓冲允许在DMA完成一个数据块的同时,另一个数据块正在准备,从而减少CPU介入,提升吞吐量。

无论使用哪种硬件平台,关键步骤包括设置GPIO配置、初始化定时器以产生时钟信号、配置DMA通道以控制数据传输,并确保正确处理数据缓冲和同步。此外,还应考虑可能遇到的错误处理和性能优化策略,比如使用DMA完成时中断机制来控制传输过程。

本文提供了针对STM32F4xx系列芯片并行同步传输的实用指导,帮助开发者理解和适应不同硬件条件下的解决方案,从而最大化利用这些微控制器的能力。

点击了解资源详情

133 浏览量

点击了解资源详情

494 浏览量

157 浏览量

141 浏览量

103 浏览量

293 浏览量

274 浏览量

Huo的藏经阁

- 粉丝: 703

- 资源: 3

最新资源

- personal_website:个人网站

- css按钮过渡效果

- 解决vb6加载winsock提示“该部件的许可证信息没有找到。在设计环境中,没有合适的许可证使用该功能”的方法

- haystack_bio:草垛

- BaJie-开源

- go-gemini:Go中用于Gemini协议的客户端和服务器库

- A14-Aczel-problems-practice-1-76-1-77-

- 行业文档-设计装置-一种拉出水泥预制梁的侧边钢筋的机构.zip

- assessmentProject

- C ++ Primer(第五版)第六章练习答案.zip

- website:KubeEdge网站和文档仓库

- MATLAB project.rar_jcf_matlab project_towero6q_牛顿插值法_牛顿法求零点

- ML_Pattern:机器学习和模式识别的一些公认算法[决策树,Adaboost,感知器,聚类,神经网络等]是使用python从头开始实现的。 还包括数据集以测试算法

- matlab布朗运动代码-clustering_locally_asymtotically_self_similar_processes:项目

- 行业文档-设计装置-一种折叠钢结构雨篷.zip

- mswinsck.zip