FPGA双口RAM测试实践:实现数据传输与控制

需积分: 45 200 浏览量

更新于2024-07-17

10

收藏 917KB PDF 举报

本篇文章主要介绍了如何在FPGA中实现简单的双口RAM和真双口RAM的测试,以及它们各自的工作原理和在Altera FPGA中的具体应用。首先,简单双口RAM具有独立的读和写地址线,允许同时进行读写操作,但需注意地址线上的互斥性,即不能同时对同一地址进行读写操作。数据通过wrdata输入,wren控制写操作,而rdaddress用于读取数据,读取无需额外的请求信号。

实验过程中,通过串口通信将数据传输到FPGA,利用Quartus II软件的In-System Memory Content Editor工具监控RAM中的数据变化。当需要回传数据时,通过按键触发RAM内容的发送。实验选择了具备一个读端口和一个写端口的配置,这样可以在满足基本读写需求的同时,支持不同的数据宽度设置。

真双口RAM则更为复杂,它有两组独立的数据线和地址线,提供了四个端口(两个读端口和两个写端口)进行操作,这使得它可以同时进行两个独立的读或写操作,或者一个端口读、另一个端口写。真双口RAM的设计中,通常共享一个地址空间,因此地址线是共用的。

内存块类型的选择在实验中可能考虑了自动分配(Auto)、内部块RAM(M9K)、或内部寄存器(LCs),具体取决于设计的需求和资源可用性。对于读写操作,确保单个时钟信号用于同步所有操作,包括写入和读取。

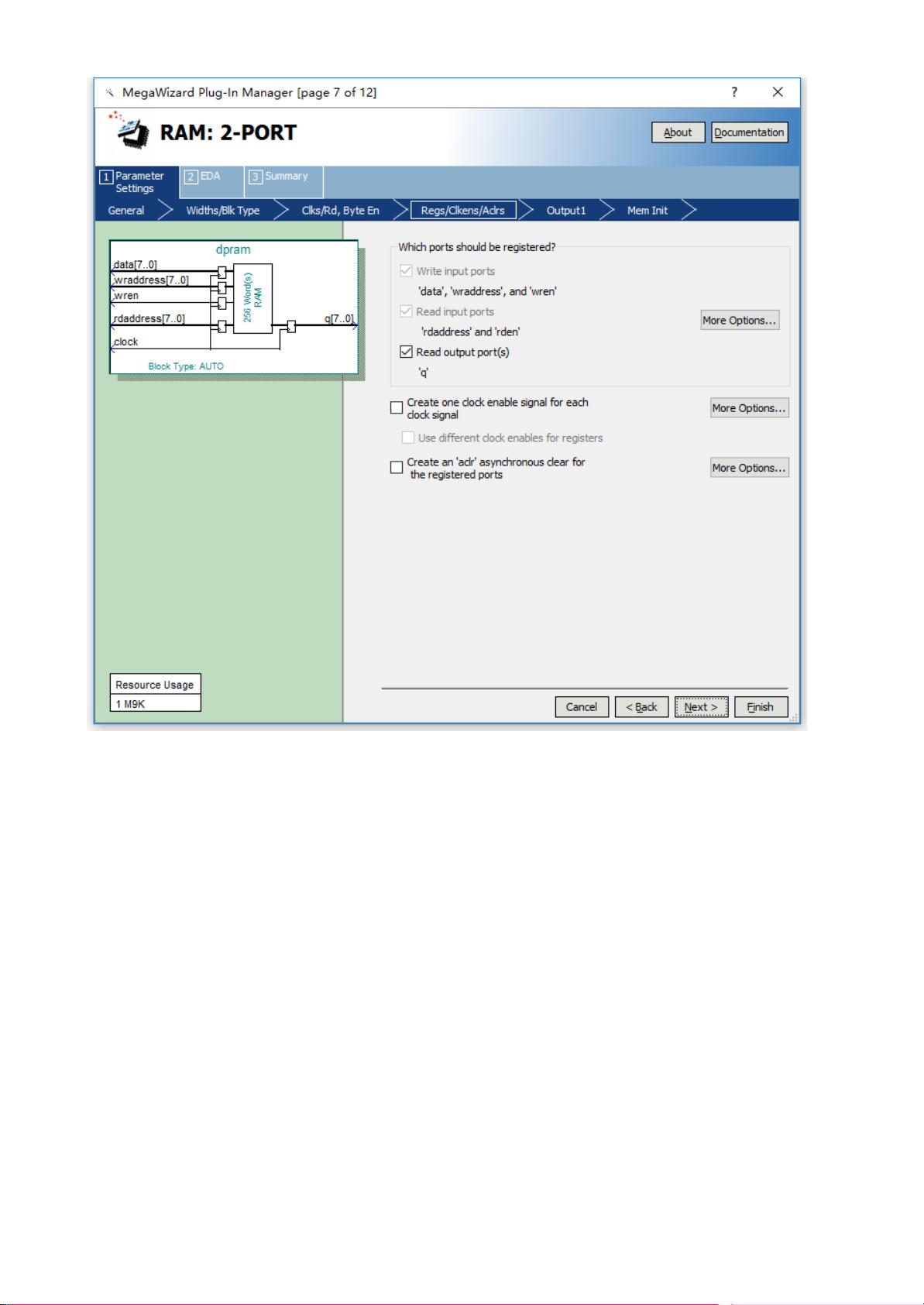

此外,文章还提到了如何创建读使能信号(ren),以及在输入输出路径中使用寄存器进行缓冲,输入寄存器是预设的,而输出寄存器可以根据需要添加或移除。为了实现更灵活的控制,还可以创建异步清零信号(aclr),只对寄存器进行清零,而不是RAM。

在实际操作中,需要注意写入和读取操作的时机,避免在写入过程中同时进行读取,以防止数据冲突。整个过程通过详细的截图和仿真代码展示,帮助读者理解并实践如何在FPGA中构建和测试这两种不同类型的RAM。通过这个实验,可以加深对FPGA硬件设计和RAM工作模式的理解。

2466 浏览量

2022-09-23 上传

105 浏览量

2022-09-20 上传

179 浏览量

548 浏览量

174 浏览量

zhubo11111111

- 粉丝: 0

- 资源: 4

最新资源

- 桃桃_信息熵函数_

- 异步操作测试.zip

- Titration: Project Tracking Application-开源

- 消费日志:SpendLogs-个人支出经理

- ApkAnalyser-apk敏感信息提取

- springbootFastdfs

- pico-snake:用于Raspberry Pi Pico的MicroPython中的Snake游戏

- 实验8 PWM输出实验(ok)_pwm_stm32_LED_

- loopback连接oracle数据的步骤总结

- BLoC-Shopping:使用“业务逻辑组件”设计模式和集团状态管理的应用

- 网站源代码前端交互 移动端转换

- Chart:基于 Highcharts.js 的图表生成器

- 人体测量学

- next-crud:使用NextJS构建的全栈CRUD应用程序

- Matrosdms:具有现实生活对象的文件管理系统-开源

- CPP程序设计实践教程_Cprogram_