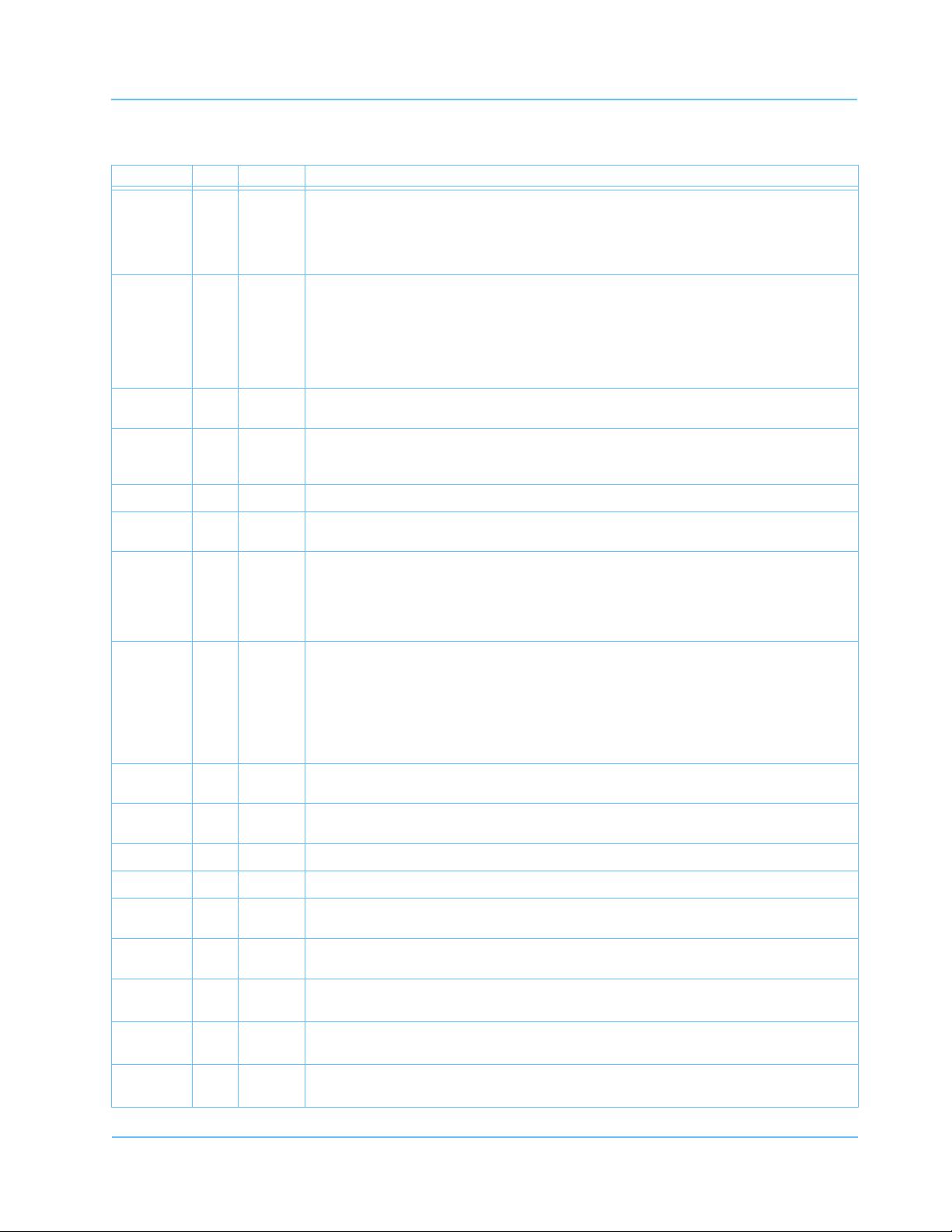

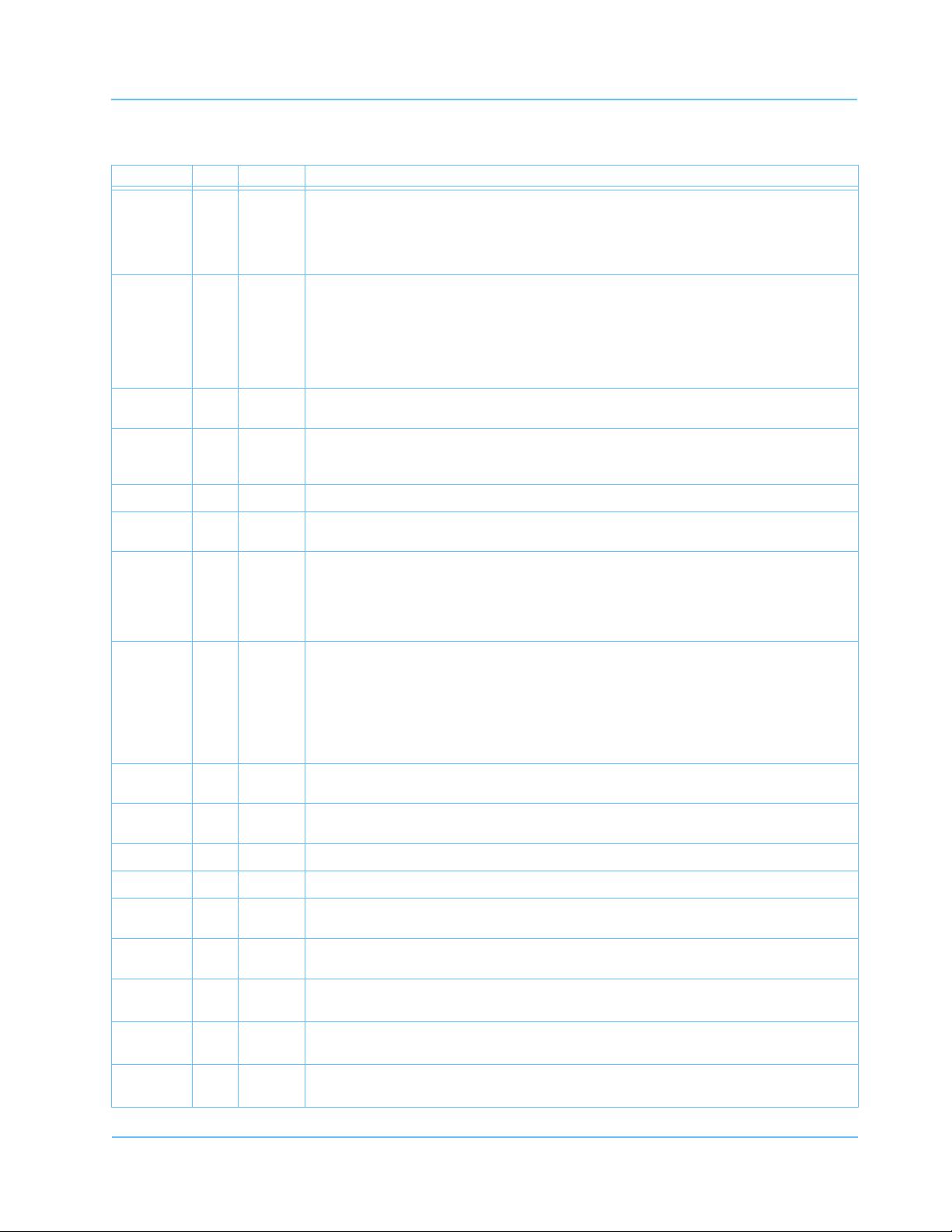

JEDED Standard No. 21C

Page 4.20.21-6

Release 22 Revision 1.0

CKE[1:0] IN

Active

High

CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and

output drivers of the SDRAMs. Taking CKE LOW provides PRECHARGE POWER-DOWN and

SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row ACTIVE in any bank).

Connected to the registering clock driver on 72b-SO-RDIMMs, connected to DRAMs on 72b-SO-

CDIMMs and 72b-SO-DIMMs.

S_n[3:0] IN

Active

Low

Enables the command decoders for the associated rank of SDRAM when low and disables

decoders when high. When decoders are disabled, new commands are ignored and previous

operations continue. Connected to SDRAMs on 72b-SO-CDIMMs and 72b-SO-DIMMs. For 72b-

SO-RDIMMs, other combinations of these input signals perform unique functions, including

disabling all outputs (except CKE and ODT) of the register(s) on the DIMM or accessing internal

control words in the register device(s). For modules with two registers, S[3:2] operate similarly to

S[1:0] for the second set of register outputs or register control words.

ODT[1:0] IN

Active

High

On-Die Termination control signals. Connected to SDRAMs on 72b-SO-CDIMMs and 72b-SO-

DIMMs, connected to the registering clock driver on 72b-SO-RDIMMs.

RAS_n,

CAS_n,

WE_n

IN

Active

Low

When sampled at the positive rising edge of the clock, CAS_n, RAS_n, and WE_n define the

operation to be executed by the SDRAM. Connected to SDRAMs on 72b-SO-CDIMMs and 72b-SO-

DIMMs, connected to the registering clock driver on 72b-SO-RDIMMs.

V

REFDQ

Supply Reference voltage for DQ0-DQ63 and CB0-CB7.

V

REFCA

Supply

Reference voltage for A0-A15, BA0-BA2, RAS_n, CAS_n, WE_n, S0_n, S1_n, CKE0, CKE1,

Par_In, ODT0 and ODT1.

BA[2:0] IN —

Selects which SDRAM bank of eight is activated.

BA0 - BA2 define to which bank an Active, Read, Write or Precharge command is being applied.

Bank address also determines mode register is to be accessed during an MRS cycle. Connected to

SDRAMs on 72b-SO-CDIMMs and 72b-SO-DIMMs, connected to the registering clock driver on

72b-SO-RDIMMs.

A[15:13,

12/BC_n,11,

10/AP,9:0]

IN —

Provided the row address for Active commands and the column address and Auto Precharge bit for

Read/Write commands to select one location out of the memory array in the respective bank. A10 is

sampled during a Precharge command to determine whether the Precharge applies to one bank

(A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by

BA. A12 is also utilized for BL 4/8 identification for ‘’BL on the fly’’ during CAS command. The

address inputs also provide the op-code during Mode Register Set commands. Connected to

SDRAMs on 72b-SO-CDIMMs and 72b-SO-DIMMs, connected to the registering clock driver on

72b-SO-RDIMMs.

DQ[63:0],

CB[7:0]

I/O — Data and Check Bit Input/Output pins

DM[8:0] IN

Active

High

Masks write data when high, issued concurrently with input data.

V

DD

, V

SS

Supply Power and ground for the DDR SDRAM input buffers and core logic.

V

TT

Supply Termination Voltage for Address/Command/Control/Clock nets.

DQS_t[17:0] I/O

Positive

Edge

Positive line of the differential data strobe for input and output data.

DQS_c[17:0] I/O

Negative

Edge

Negative line of the differential data strobe for input and output data.

SA[1:0] IN —

These signals are tied at the system planar to either V

SS

or V

DDSPD

to configure the serial SPD

EEPROM address range.

SDA I/O —

This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be

connected from the SDA bus line to V

DDSPD

on the system planar to act as a pullup.

SCL IN —

This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected

from the SCL bus time to V

DDSPD

on the system planar to act as a pullup.

Table 4 — Registered DIMM Input/Output Functional Description (Cont’d)

Symbol Type Polarity Function