0.18μm CMOS工艺下基于TDC的高性能全数字锁相环设计与仿真

版权申诉

196 浏览量

更新于2024-06-25

1

收藏 12.18MB DOCX 举报

随着集成电路技术的飞速进步,全数字锁相环(ADPLL, All-Digital Phase-Locked Loop)作为现代超大规模集成电路中的核心组成部分,因其灵活性、高精度和低功耗特性,被广泛应用于各种高速时钟同步和频率合成应用。本文主要研究和设计了一种基于时间数字转换器(TDC, Time-Digital Converter)的全数字锁相环。

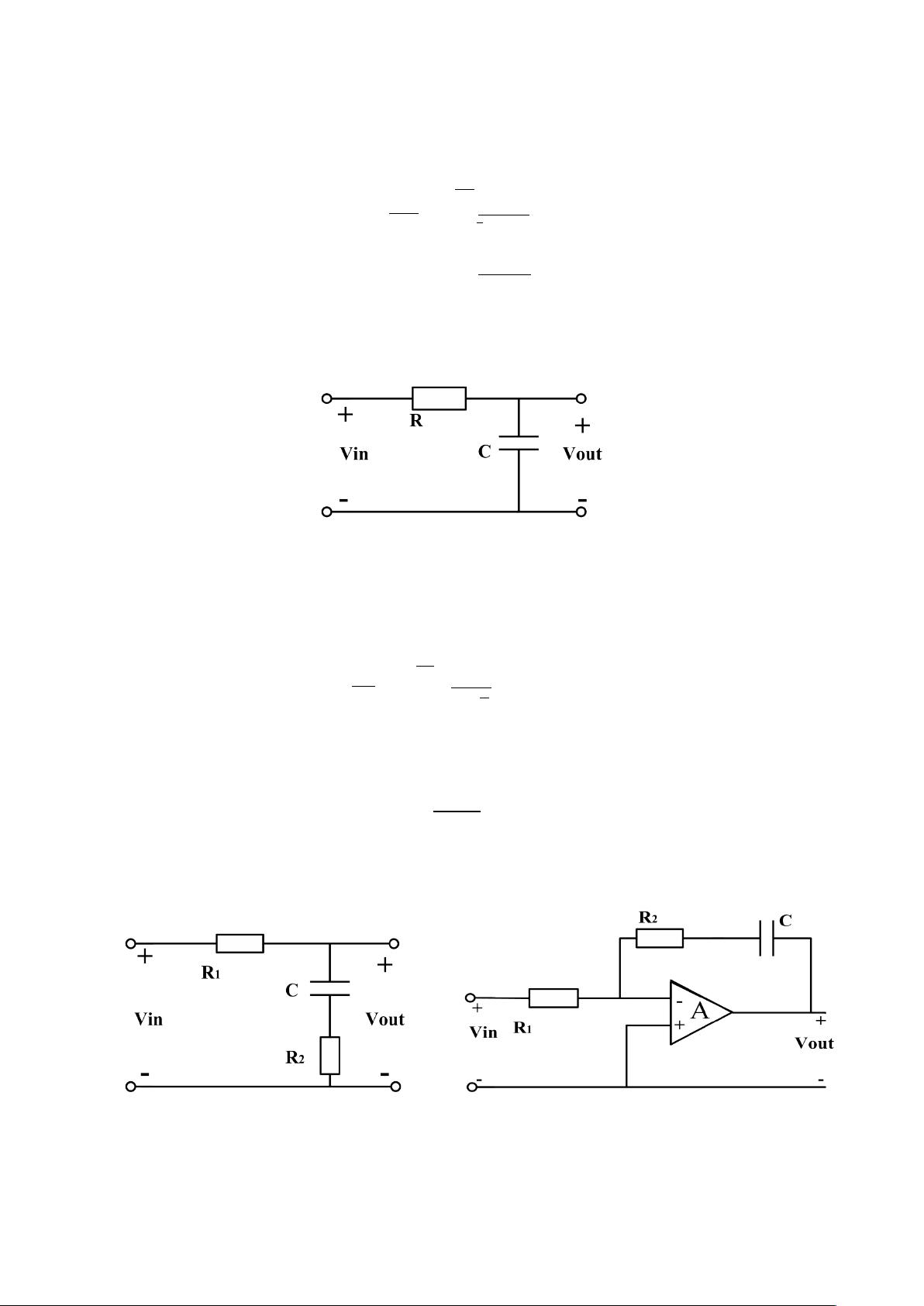

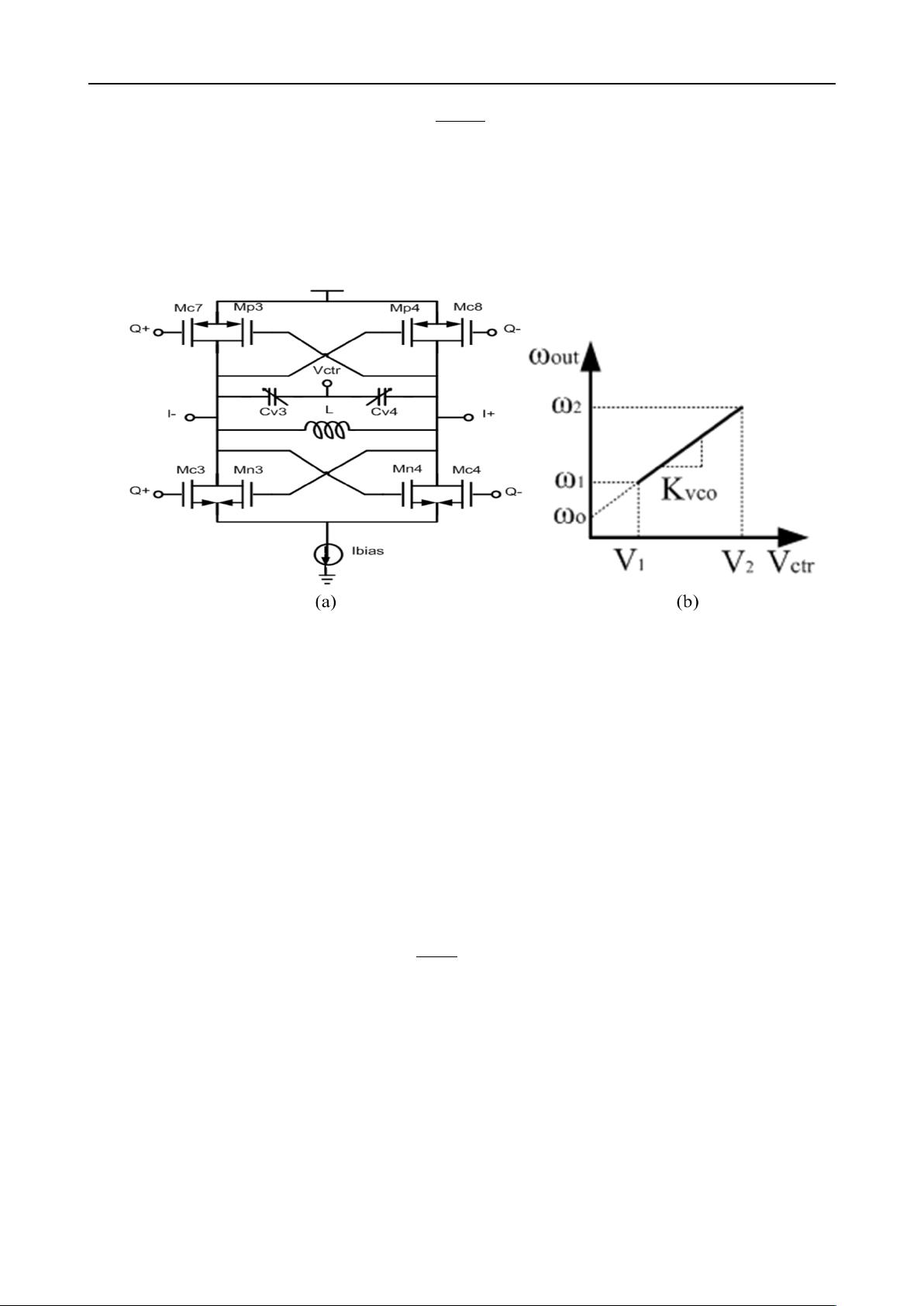

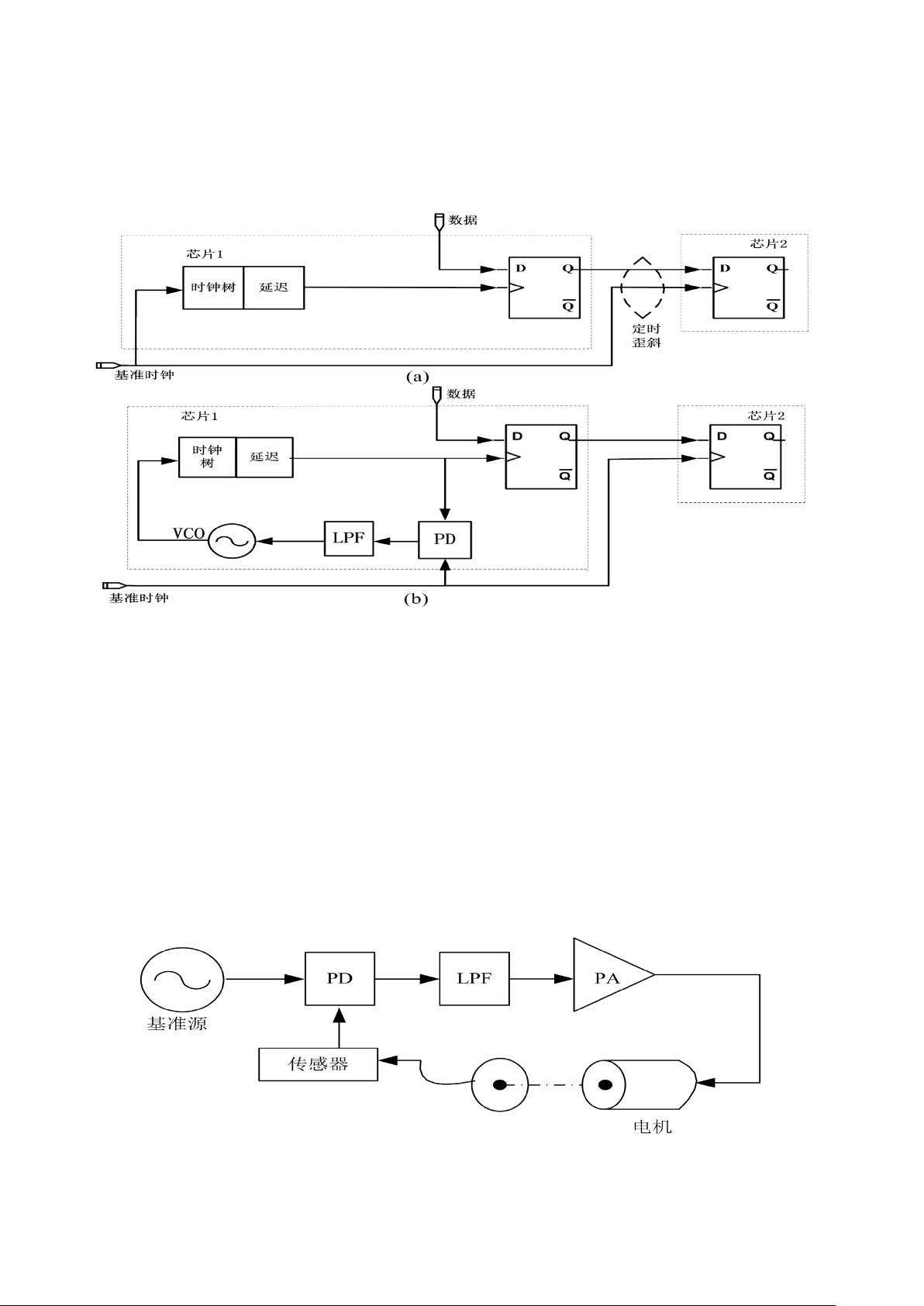

全数字锁相环的关键在于其摒弃了传统的模拟相位比较环节,而是完全依赖于数字信号处理技术。文章首先概述了锁相环的基本概念和发展历程,包括其分类和常见的应用领域,如通信系统、雷达和无线通信等。接着,着重讨论了全数字锁相环的系统架构,包括鉴相器、时间数字转换器、数控振荡器和数字分频器等子模块。鉴相器负责比较输入信号与参考信号的相位差,TDC则用来量化这个相位差并将其转化为数字信号。数控振荡器用于产生参考信号,通过与输入信号进行比较,确保输出信号与参考信号保持同步。数字分频器则可以根据需要调整输出频率,提供灵活的频率调节能力。

本文的核心创新在于针对传统TDC在时数转换准确性和测量范围上的局限,设计了一种带有上升沿检测电路的TDC,提高了时钟精度和相位测量范围。同时,通过采用一个环形振荡器提供多相参考时钟,实现了对工艺、电压和温度变化的补偿,增强了锁相环的稳定性。另外,通过简化数控振荡器结构和使用可编程任意整数分频器,优化了电路性能,保持了反馈时钟波形的50%占空比,减少了电路复杂度和面积。

设计过程中,作者遵循了从顶层设计到低级实现的自顶向下方法,使用0.18微米CMOS标准数字逻辑工艺。RTL级设计验证了锁相环在64MHz到640MHz的锁定输出频率范围内,以及27到70的分频系数范围内的稳定工作。在10MHz参考频率下,环路锁定时间保持在12微秒以内,展示了优秀的时间响应性能。

本文不仅提供了理论分析,还涉及了数字模块的具体设计实现策略,以及数字集成电路开发设计和数模混合仿真的详细流程。这项研究旨在提升全数字锁相环的性能和可靠性,为高性能时钟电路设计提供了实用的解决方案。

1481 浏览量

149 浏览量

122 浏览量

2022-12-01 上传

1424 浏览量

2023-02-23 上传

2022-12-15 上传

346 浏览量

2021-12-21 上传

老帽爬新坡

- 粉丝: 99

最新资源

- 自动生成CAD模型文件的测试流程

- 掌握JavaScript中的while循环语句

- 宜科高分辨率编码器产品手册解析

- 探索3CDaemon:FTP与TFTP的高效传输解决方案

- 高效文件对比系统:快速定位文件差异

- JavaScript密码生成器的设计与实现

- 比特彗星1.45稳定版发布:低资源占用的BT下载工具

- OpenGL光源与材质实现教程

- Tablesorter 2.0:增强表格用户体验的分页与内容筛选插件

- 设计开发者的色值图谱指南

- UYA-Grupo_8研讨会:在DCU上的培训

- 新唐NUC100芯片下载程序源代码发布

- 厂家惠新版QQ空间访客提取器v1.5发布:轻松获取访客数据

- 《Windows核心编程(第五版)》配套源码解析

- RAIDReconstructor:阵列重组与数据恢复专家

- Amargos项目网站构建与开发指南