A Low Power 1.5GHz Gm-C Filter with 0-40dB Variable Gain in

65-nm CMOS Technology

Haoyu Mei, Wei Li

State Key Laboratory of ASIC & System, Fudan University

Shanghai 201203, China

Email:

w-li@fudan.edu.cn

Abstract

Targeting to phase-array radar system, a 1.5GHz

continuous-time fifth order Chebyshev Gm-C low-pass

filter with unique gain adjustment is presented. This

paper comes up with theoretical analysis and solutions to

solve the problem existing in cascading design of high

frequency biquad filters. Methods of low-power design

and gain adjustment are also provided. The filter is

designed with TSMC 65nm process. The post simulation

results show that the filter realizes gain of 0-40dB with

1.5GHz cut-off frequency, the max gain-step smaller

than 0.5dB. The IIP3 is 1dBm and NF is about 27dB.

The chip without pads occupies 0.5 mm

2

and consumes

11mw at a 1.2-V supply voltage.

1. Introduction

In many applications such as high-speed hard disks,

communication systems, the continuous-time low-pass

filters are indispensable. As the speed requirement of

application increases, the 3-dB cut-off frequency has to

keep up with the pace. But the constraints for the

performance, like low power consumption, small area

and high linearity, as always, are strict. In comparison to

active RC filter, the Gm-C filter is more applicable for

high frequency filter design. The operational

trans-conductance amplifier (OTA) is the core part of the

Gm-C filter. In consideration of speed, linearity and

power consumption, the OTAs are all pseudo-differential

structure based on inverter.

In this paper, a 1.5GHz fifth order Chebyshev Gm-C

low-pass filter with fine-gain adjustment and low power

design is presented. The target of the filter is for

phase-array radar system, which has high requirements

for bandwidth and fine gain-step. The structure of the

paper is arranged as follows. Firstly, the circuit design

and theoretical analysis are presented. Then the post

simulation result and discussion are shown. Finally,

conclusions are addressed.

2. Circuit design and analysis

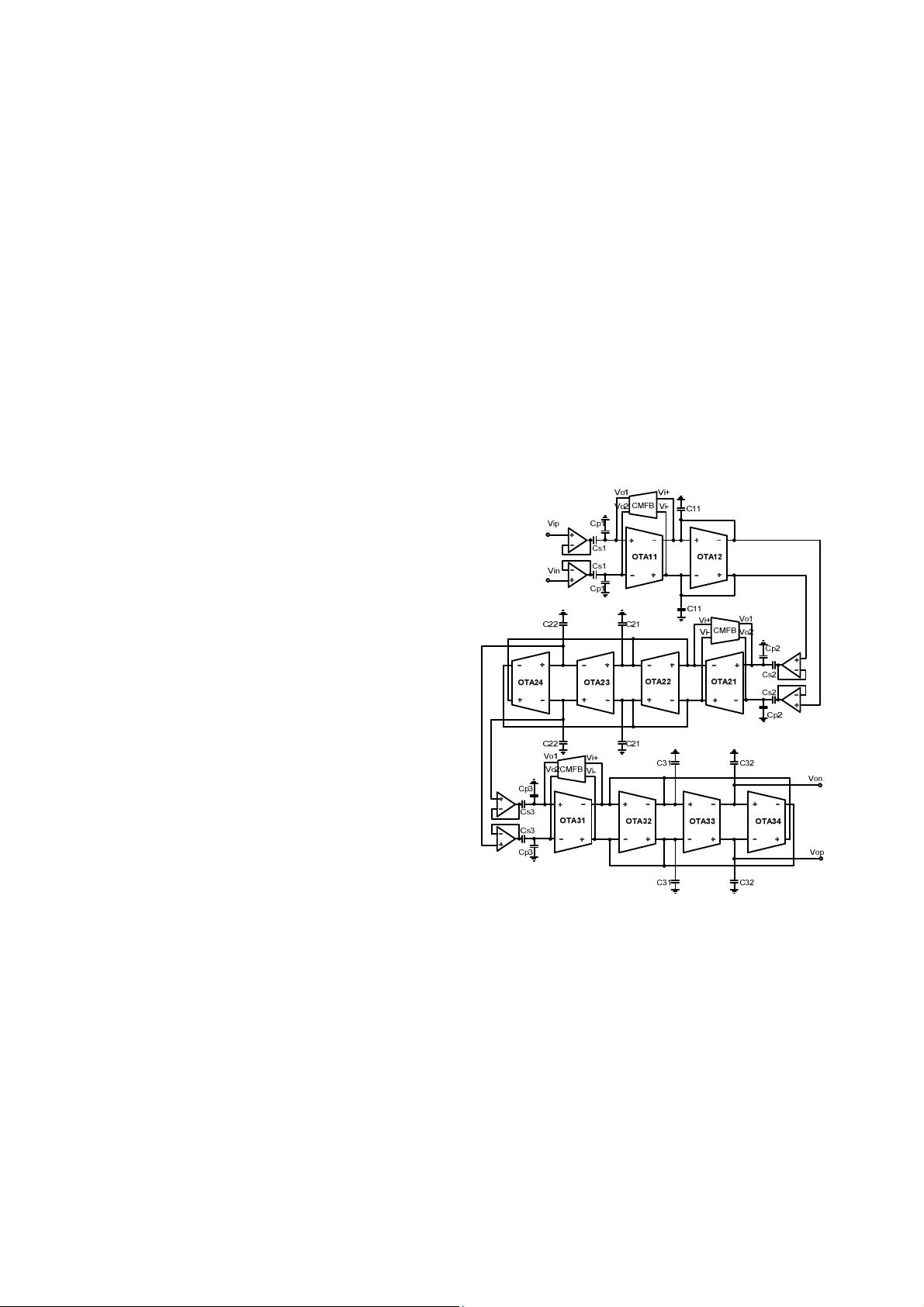

The diagram of the proposed filter is depicted in

Fig.1. The fifth order filter is realized by cascading one

first-order filter and two biquads. Unit-gain buffers are

used before the first order filter and between every two

filters in order to realize impedance isolation. In addition

to the capacitors C

ij

( i=1,2,3. j=1,2.) used for each filter

to generate poles, series capacitors(C

si

) and grounding

capacitors(C

pi

) are also used for AC coupling and gain

adjustment. The filter achieves voltage gain from 0dB to

40dB by changing the values of C

si

and C

pi

, and the

bandwidth of 1.5GHz remains the same as the buffer has

enough output driving capability.

Fig.1 The architecture of the filter

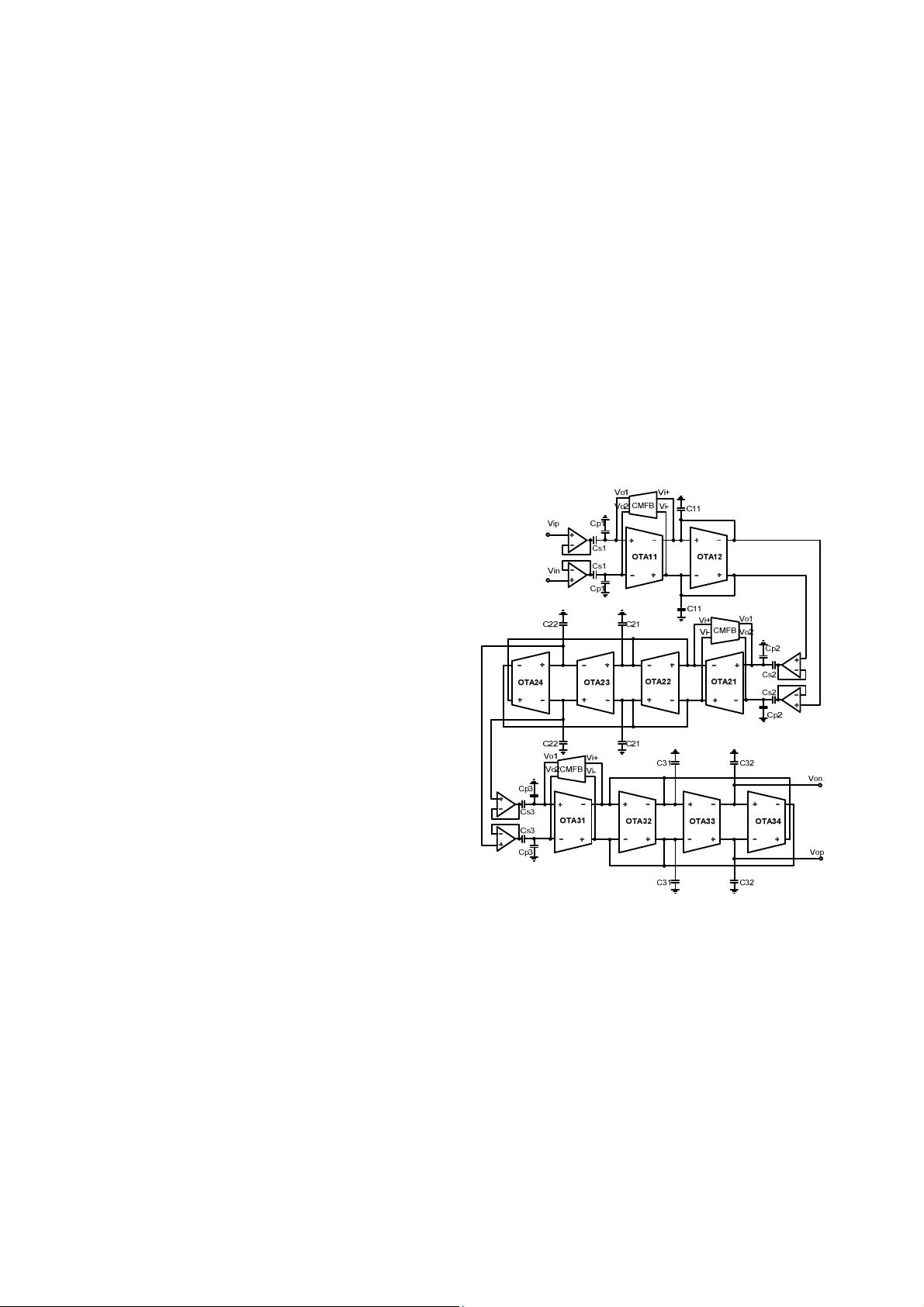

Fig.2 shows the structures of the OTAs. The last

two OTAs in a biquad are Nauta’s structures

[1]

, as shown

in Fig. 2(b). The former two OTAs’ circuit in the biquad

are chosen the same, and also the first order filter’s two

OTA’s circuits as shown in Fig. 2(a). The inverter-based

OTA shown in Fig. 2(a) has a high power efficiency for

its current-reused characteristics, but it doesn’t have the

ability of common mode rejection. The Nauta’s OTA

solves this problem but it needs four extra inverters (inv3,