DDR3 IP核初始化教程:顶层设计与s6_ddr3ip实例化

需积分: 0 43 浏览量

更新于2024-08-05

收藏 288KB PDF 举报

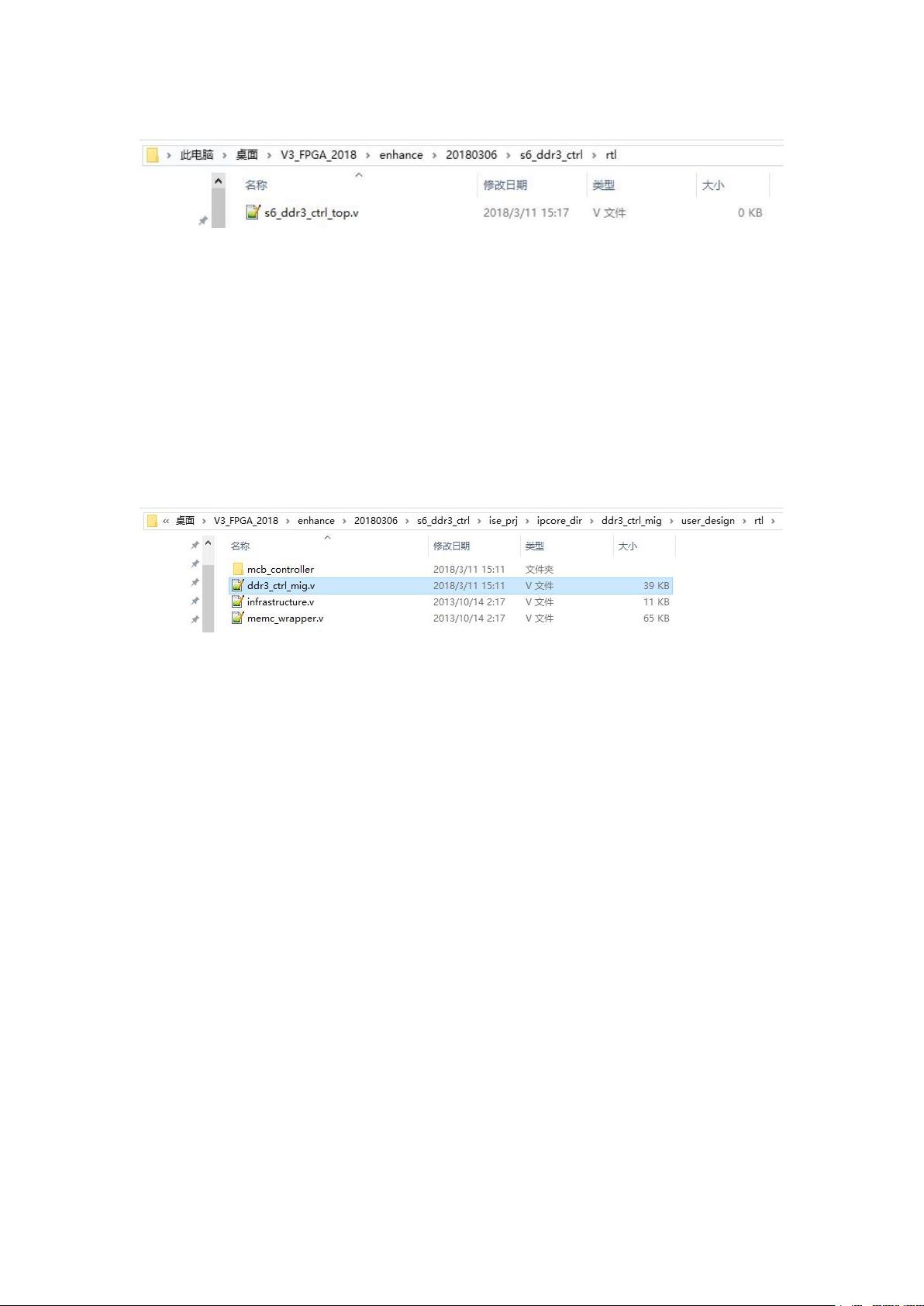

在本篇教程中,我们将深入探讨6系列DDR3 IP核的初始化过程,主要针对的是硬件设计中的高级逻辑接口(Advanced Logic Interface,ALI)和控制器模块。文章首先引导读者在新创建的顶层文件中进行操作,以便集成并管理IP核的功能。

1. 顶层文件的创建与配置:

开始设计时,首先在项目中新建一个顶层文件,这将作为整个设计的核心容器。在这个文件中,开发者需要实例化PLL(Phase-Locked Loop)模块,如`clk_333Mclk_333M_inst`。PLL是一个关键的时钟管理单元,负责生成不同频率的时钟信号,如333MHz、100MHz等,这对于DDR3内存控制器来说是必不可少的。PLl实例化时,需确保输入的系统时钟被正确连接,并输出所需的时钟信号。

2. DDR3 IP核的实例化:

接下来,作者指导如何实例化s6_ddr3ip核,这是一种预定义的DDR3内存控制器IP核。在实例化过程中,需要提供一系列配置参数,如C1_P0/M1 Mask Size、Data Port Size等,这些参数根据实际应用的需求进行设置。调试、仿真、复位控制、时钟类型、地址映射模式、数据引脚数量以及地址宽度等细节也需配置恰当,以适应芯片的具体架构。

- `C1_SIMULATION("FALSE")` 表示这是一个非模拟模式,适用于实际硬件设计,而不是仿真环境。

- `C1_RST_ACT_LOW(0)` 指定了复位信号的激活状态,通常在硬件设计中,低电平表示复位有效。

- `C1_INPUT_CLK_TYPE("SINGLE_ENDED")` 确保输入时钟是单端模式,这是DDR3接口常见的配置。

3. 接口信号连接:

在`ddr3_ctrl_mig_inst`部分,作者列举了多个接口信号,如`mcb1_dram_dq`、`mcb1_dram_a`等,这些都是与内存颗粒连接的关键信号,用于数据传输、地址译码和控制信号的交换。每个信号都对应内存控制器的不同功能,例如地址线、命令信号和片选等。

通过以上步骤,设计师可以建立起一个基本的DDR3 IP核的框架,并且了解了如何配置和连接各个组件。在实际设计过程中,可能还需要添加电源管理、错误检测与校正(ECC)、时序校准等功能。最后,鼓励读者加入QQ群450843130,与其他技术人员交流,共同学习和分享更多关于DDR3 IP核的初始化和优化经验。

2019-04-04 上传

2020-03-19 上传

点击了解资源详情

2021-08-19 上传

2018-06-01 上传

2023-04-19 上传

2011-03-15 上传

点击了解资源详情

点击了解资源详情

13572025090

- 粉丝: 344

- 资源: 313

最新资源

- 计算机二级Python真题解析与练习资料

- 无需安装即可运行的Windows版XMind 8

- 利用gif4j工具包实现GIF图片的高效裁剪与压缩

- VFH描述子在点云聚类识别中的应用案例

- SQL解释器项目资源,助力计算机专业毕业设计与课程作业

- Java实现Windows本机IP定时上报到服务器

- Windows Research Kernel源码构建指南及工具下载

- 自定义Python插件增强Sublime文本编辑器功能

- 自定义Android屏幕尺寸显示及Ydpi计算工具

- Scratch游戏编程源码合集:雷电战机与猫鼠大战

- ***网上教材管理系统设计与实现详解

- Windows环境下VSCode及Python安装与配置教程

- MinGW-64bit编译opencv库适配Qt5.14

- JavaScript API 中文离线版手册(CHM格式)

- *** 8 MVC应用多语言资源管理技巧

- 互联网+培训资料深度解析与案例分析