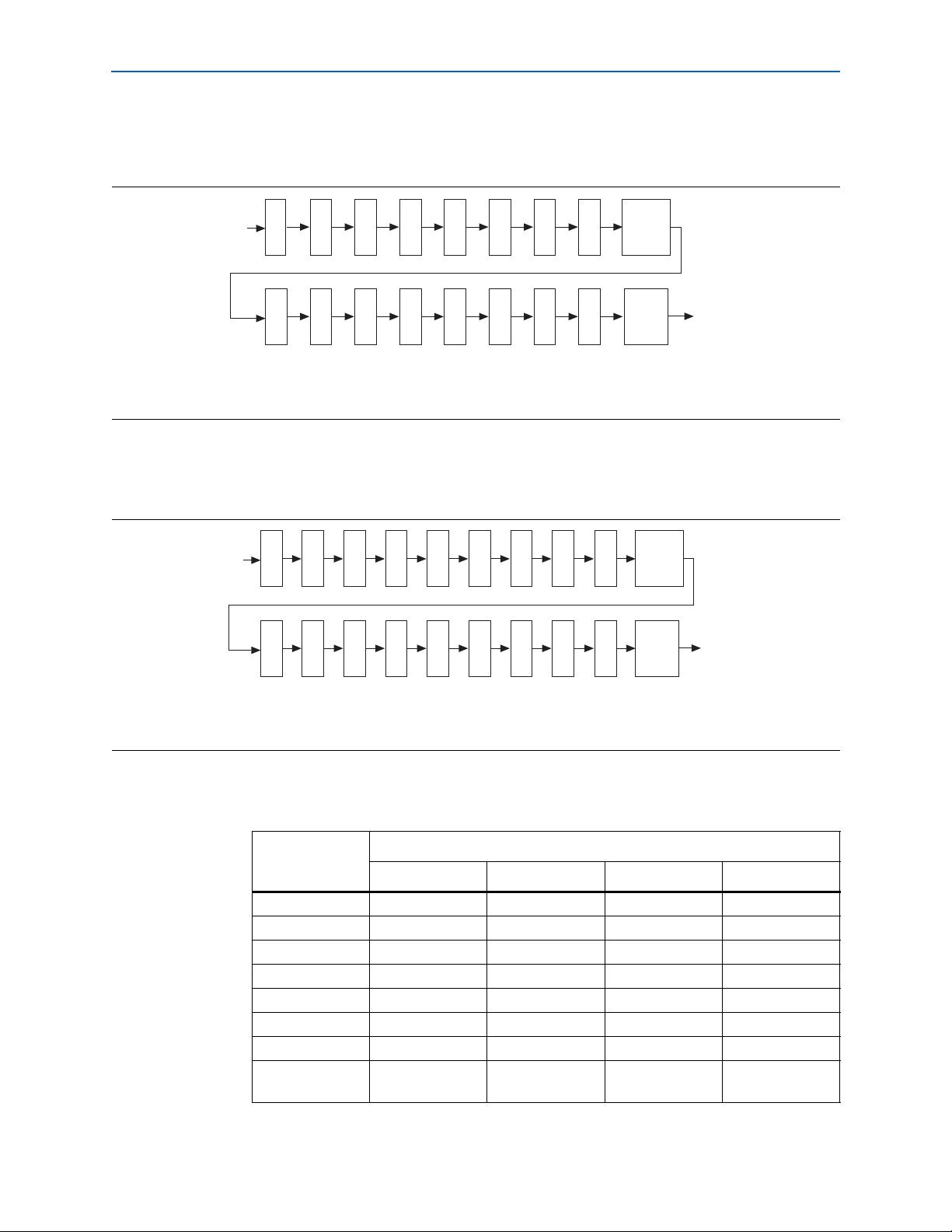

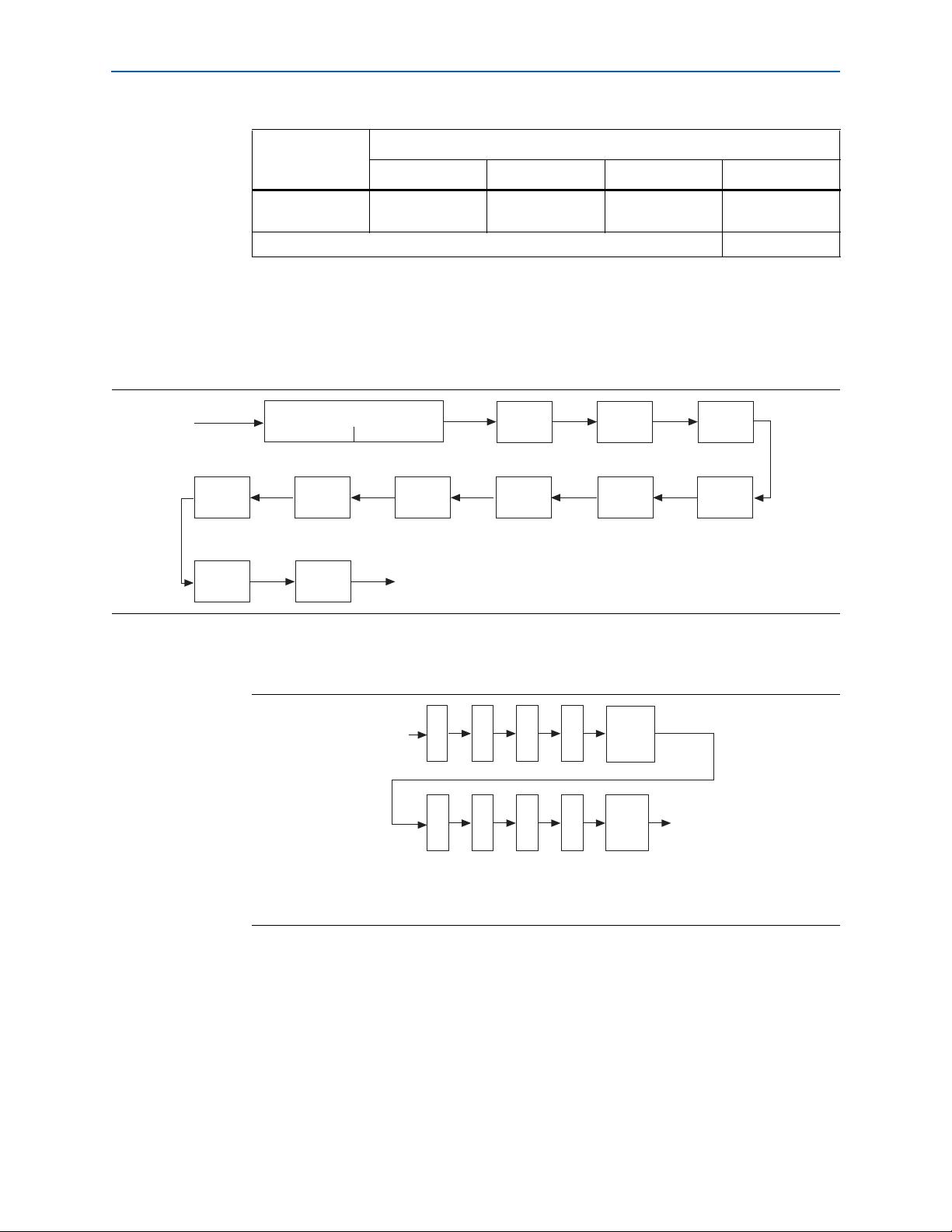

"这篇文档是Altera公司的应用笔记AN367,主要讲解在Stratix II FPGA设备中实现PLL(锁相环)的重新配置技术。内容涉及PLL的配置、使用,以及如何在FPGA环境中调整Stratix系列的时钟设定。" 在FPGA设计中,PLL(Phase-Locked Loop,锁相环)是一种重要的频率合成和相位调整器件,广泛用于生成和调整系统时钟。Altera的Stratix系列FPGA提供了增强型和快速PLL,允许用户在运行过程中实时改变计数器设置和 PLL 输出时钟的相位偏移。这种实时重新配置能力不仅包括VCO(电压控制振荡器)的相位 tap,还能够调整充电泵和环路滤波器组件,进而动态地影响PLL的带宽。 PLL的可重构性在多种应用场景中极具价值。例如,当系统需要在多个频率间切换操作时,可以无需重新配置整个FPGA就能更新输出时钟频率。此外,这在原型验证环境中也非常有用,设计者可以迅速扫频PLL的输出频率,或在运行时调整输出时钟的相位。例如,一个生成测试模式的系统可能需要在50MHz或100MHz之间切换,以适应不同的被测设备需求。 Stratix II FPGA的PLL配置包括以下几个关键方面: 1. **计数器设置**:PLL通常通过分频器产生不同频率的时钟,通过改变这些分频器的参数,可以调整输出时钟的频率。 2. **相位偏移**:PLL的相位tap允许对输出时钟进行精确的相位调整,这对于同步系统或者需要精确时钟同步的应用尤其重要。 3. **充电泵和环路滤波器**:这两个组件决定了PLL的环路响应,从而影响其带宽。改变它们的参数可以动态调整PLL的稳定性和响应速度。 4. **实时重配置**:在不重新配置整个FPGA的情况下,能够单独修改PLL的参数,这极大地提高了设计的灵活性和系统的响应能力。 5. **多频率操作**:实时重配置功能使得Stratix II FPGA能轻松适应多种工作频率,简化了多标准支持的设计流程。 6. **原型验证**:在开发阶段,实时调整PLL参数可以快速评估不同配置下的系统性能,加速设计验证过程。 AN367这份应用笔记详细介绍了如何在Stratix II FPGA中实施PLL的重新配置策略,对于理解和优化基于Stratix II FPGA的时钟系统设计具有很高的指导价值。理解并掌握这些知识,将有助于提高系统时钟的灵活性和整体性能。

剩余31页未读,继续阅读

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 深入理解23种设计模式

- 制作与调试:声控开关电路详解

- 腾讯2008年软件开发笔试题解析

- WebService开发指南:从入门到精通

- 栈数据结构实现的密码设置算法

- 提升逻辑与英语能力:揭秘IBM笔试核心词汇及题型

- SOPC技术探索:理论与实践

- 计算图中节点介数中心性的函数

- 电子元器件详解:电阻、电容、电感与传感器

- MIT经典:统计自然语言处理基础

- CMD命令大全详解与实用指南

- 数据结构复习重点:逻辑结构与存储结构

- ACM算法必读书籍推荐:权威指南与实战解析

- Ubuntu命令行与终端:从Shell到rxvt-unicode

- 深入理解VC_MFC编程:窗口、类、消息处理与绘图

- AT89S52单片机实现的温湿度智能检测与控制系统

信息提交成功

信息提交成功