TMS320F28027中断管理与PIE_Clock:原理与流程详解

需积分: 9 192 浏览量

更新于2024-07-20

收藏 6.5MB PDF 举报

本资源是一份关于TI公司的TMS320F28027处理器的课件,主要集中在第1章的内容——"Pie Clock",即片内执行单元(PIE)和时钟管理。该课件由黄灿水教授在2015年3月讲解,旨在介绍32位数字信号控制器和DSP原理中的中断系统。

首先,中断是处理器处理外部事件的重要机制,它允许CPU在遇到特定事件(如定时器到期、AD转换完成或输入引脚状态变化)时暂时停止当前任务,转而去执行相应的服务子程序。中断源包括各种硬件设备产生的事件,它们按照一定的优先级向CPU申请中断。中断优先级决定了CPU处理中断的顺序,而中断向量表则是存储所有中断服务程序入口地址的地方。

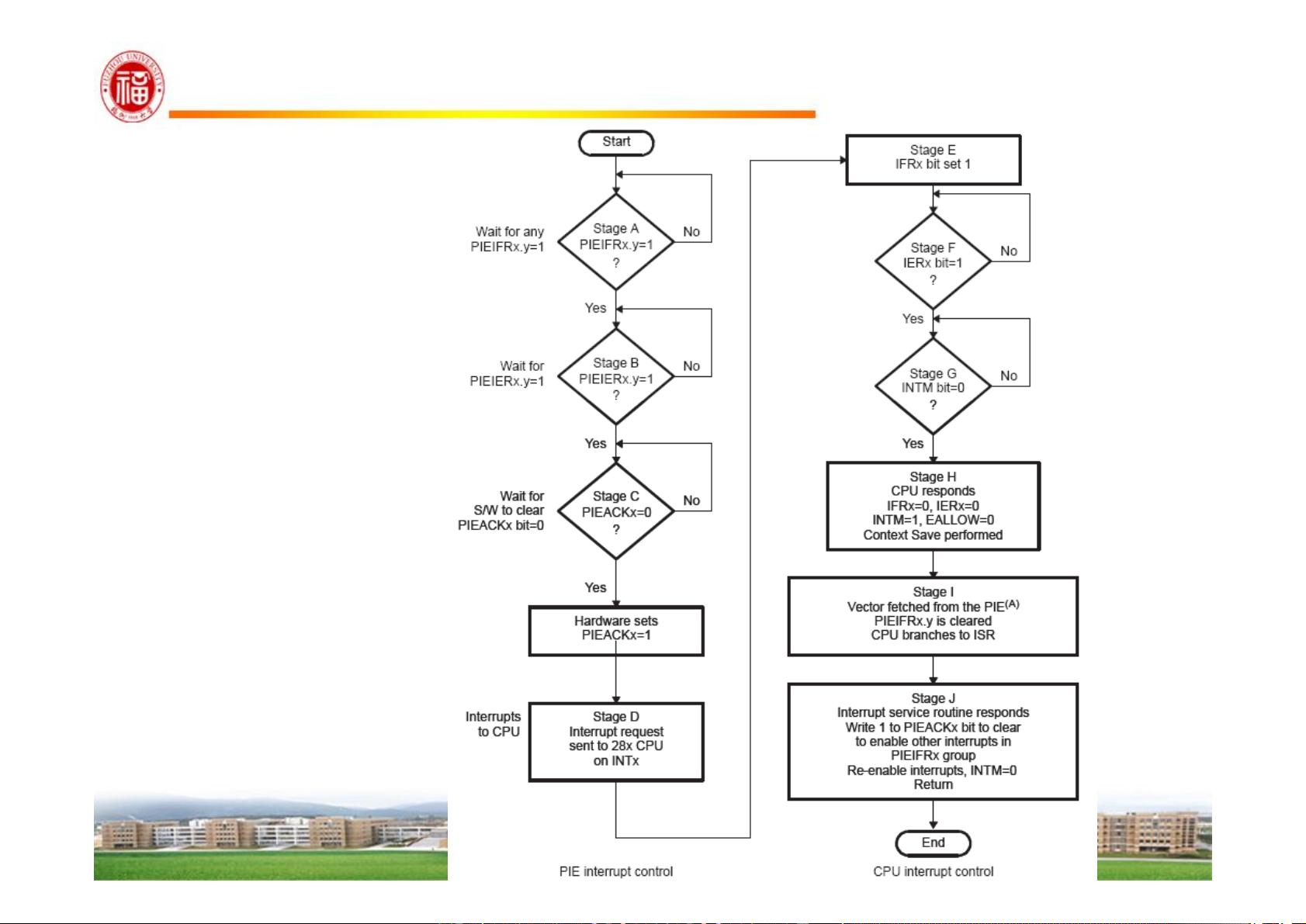

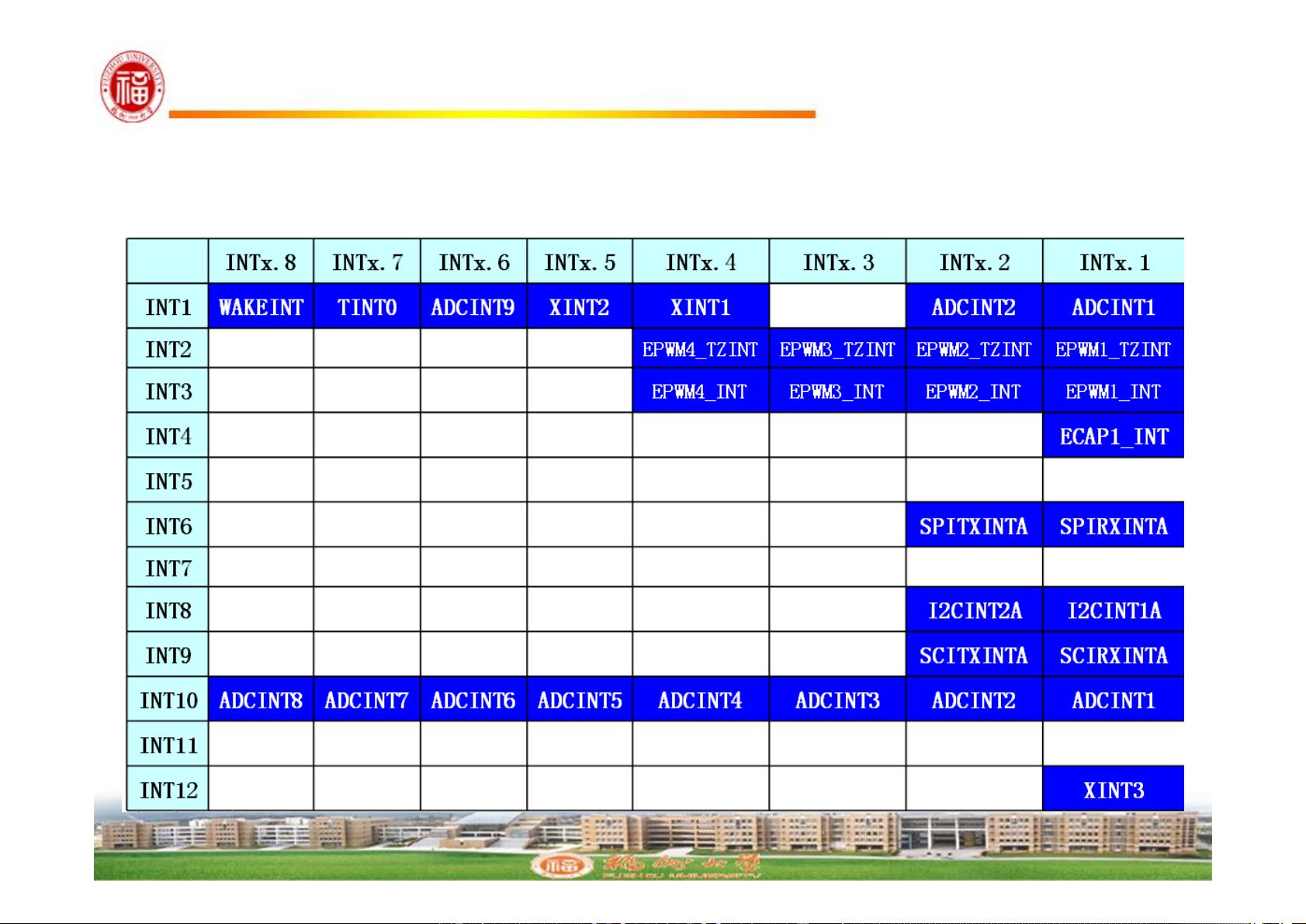

接着,课件详细解释了TMS320F28027的三级中断管理模式:外设级负责生成中断请求,如果中断没有被屏蔽,会传递到片内执行单元(PIE)级;PIE级负责中断的分组和仲裁,根据中断请求的可屏蔽性和中断使能状态决定是否将中断传递给CPU;CPU级在接收到中断请求后,会暂停当前操作,清除流水线,保存现场,然后执行中断服务子程序(ISR)。

中断简化流程包括中断请求触发、中断使能判断、PIE仲裁以及中断响应等步骤。可屏蔽中断如INT1至INT14等,需要在中断使能寄存器IER中启用;不可屏蔽中断如XRS、NMI等,则不受控制地立即响应。中断结束后,中断标志寄存器(IFR)和中断使能寄存器(EIFR)的状态会被自动更新。

中断寄存器是关键组件,其中IFR记录了中断发生的标志,一旦中断处理完毕,相应位会自动清零;IER则用于中断的控制,设置为1表示允许中断,处理后自动清零以防止重复响应。

这份课件深入浅出地阐述了TMS320F28027处理器的中断管理机制,对于理解和设计基于该处理器的实时嵌入式系统具有重要的参考价值。理解并掌握这些概念和技术,有助于开发出高效且可靠的系统应用程序。

点击了解资源详情

点击了解资源详情

393 浏览量

244 浏览量

2022-07-14 上传

2022-09-24 上传

110 浏览量

101 浏览量

125 浏览量

cshhuang

- 粉丝: 4

- 资源: 8

最新资源

- Apress.Pro.LINQ.Language.Integrated.Query.in.C#2008

- 阵列感应测井资料处理方法研究.pdf

- vb操作填空题答案看看就会

- 使用 ADOBE FLEX 3 开发 Adobe AIR 1.1 应用程序.pdf

- MFC教程课件,荣希学

- C++入门经典(3rd) .pdf

- JAVA基础。入门单词

- 数据结构课程设计 关于二叉树

- IDC机房方案,共四部分。

- cisco 4500 serial

- TCP-IP详解卷1 5.pdf

- TCP-IP详解 卷14.pdf

- EJB3.0实例教程

- OFDM-Based Broadband Wireless Networks:Design and Optimization

- C#实用书籍C# 语言规范

- 《TCP-IP详解卷1》