PS/2接口鼠标键盘通信协议详解

需积分: 49 192 浏览量

更新于2024-07-04

收藏 359KB PDF 举报

"这篇文档详细介绍了PS/2鼠标、键盘和触摸板与计算机之间的通信协议。作者是Adam Chapweske,更新日期为2003年5月9日。文章主要内容涵盖了物理接口、电气接口以及协议规范。此外,文档还提到了针对键盘和鼠标设备的更高级别的信息,如命令、数据包格式等,这些信息在专门针对这两个设备的其他文档中有更深入的讨论。"

在PS/2鼠标和键盘协议中,首先涉及的是物理接口。这种接口有两种类型:5针DIN和6针迷你 DIN(PS/2)连接器。6针连接器通常用于鼠标和键盘,而5针DIN接口在早期的AT键盘中更为常见。接口的引脚分布和功能对于理解设备如何与主机进行通信至关重要。

电气接口方面,PS/2设备通常使用单向串行通信,主机发送命令,而设备则回应数据。接口采用低电压差分信号(LVDS)技术,允许在低电压下实现高速数据传输,降低了电磁干扰的可能性。数据传输速率通常在10-12 Mbps之间,这在当时已经足够满足鼠标和键盘的需求。

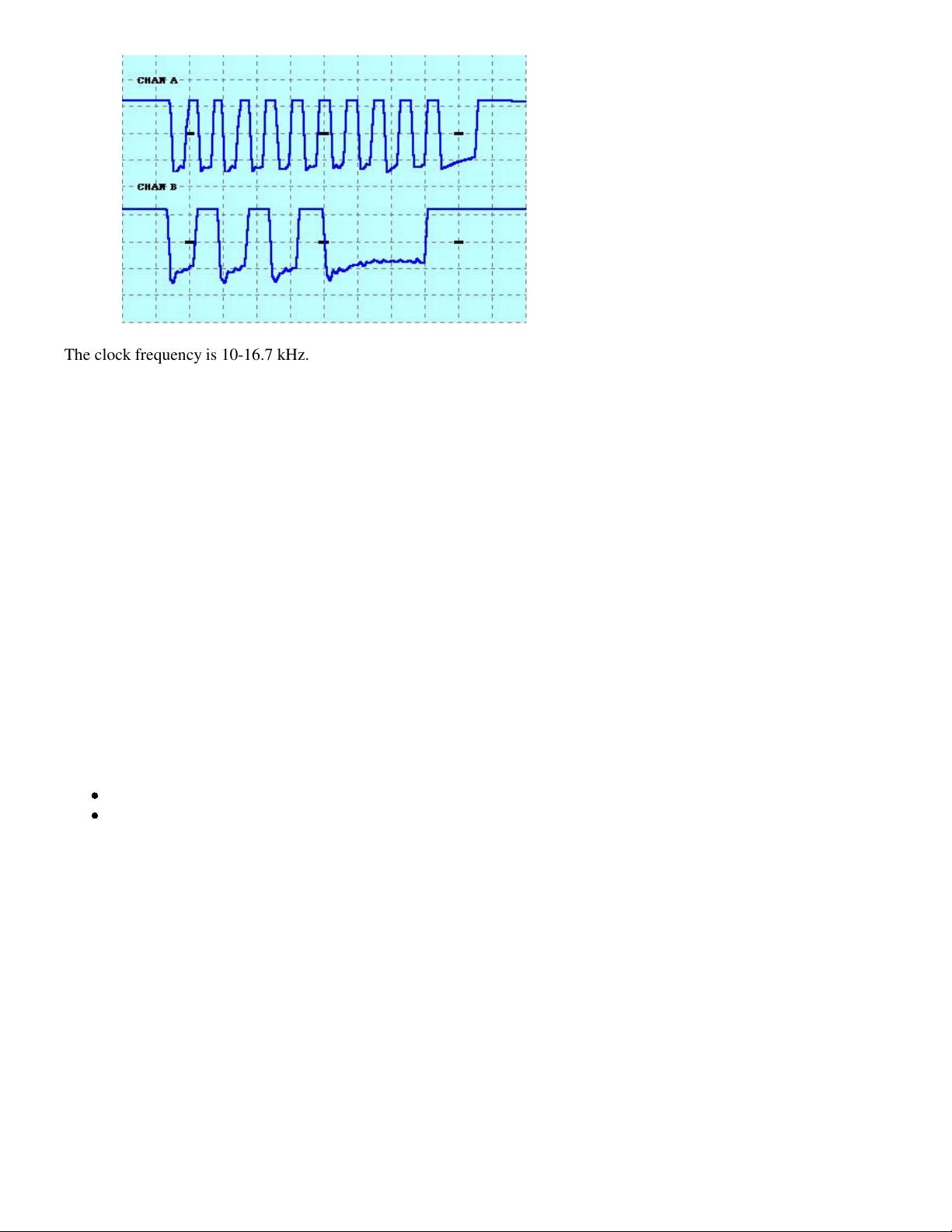

协议部分,PS/2协议基于中断请求(IRQ)和命令响应机制。主机通过发送命令来控制设备,如设置报告速率、读取设备状态等。设备则根据接收到的命令执行相应操作并返回数据。每个命令或数据包由8位组成,包括一个起始位、数据位、奇偶校验位和停止位。在通信过程中,设备会通过一根数据线发送数据,主机则通过另一根数据线接收。为了确保通信的可靠性,设备和主机都会进行错误检测,如奇偶校验,以确认数据的完整性。

PS/2键盘和鼠标设备具有特定的命令集,用于改变其工作模式或获取设备信息。例如,主机可以发送一个命令来改变鼠标的报告速率,或者查询键盘的状态。这些命令和响应格式在相关设备接口文档中有详细描述。

除了基本的通信协议,PS/2接口还支持热插拔,允许用户在不关闭计算机的情况下插入或移除设备。然而,这需要谨慎操作,因为不正确的热插拔可能会导致设备损坏或数据丢失。

"The PS/2 Mouse/Keyboard Protocol"文档是了解PS/2设备与计算机之间交互的宝贵资料,对于硬件爱好者、系统开发者和故障排查人员来说,它是不可或缺的参考材料。尽管随着USB接口的普及,PS/2接口在现代计算机中逐渐减少,但在一些老旧系统和工业应用中,PS/2接口仍然有其存在价值。

2021-09-30 上传

2011-10-25 上传

2024-01-25 上传

2023-05-19 上传

2023-05-20 上传

2023-05-22 上传

2023-05-19 上传

2023-06-12 上传

2023-06-08 上传

三哥编程分享

- 粉丝: 786

- 资源: 5

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载