ARM JTAG测试原理详解:TAP与边界扫描架构

需积分: 0 111 浏览量

更新于2024-07-22

收藏 432KB DOC 举报

本报告深入探讨了ARM JTAG测试的基本原理,特别关注于TAP(TEST ACCESS PORT)和BOUNDARY-SCAN ARCHITECTURE在ARM7TDMI平台中的应用。首先,报告从IEEE 1149.1 Test Access Port and Boundary-Scan Architecture标准出发,介绍了JTAG测试技术的起源和标准化过程。JTAG,全称JOINT TEST ACTION GROUP,由该组织提出并经IEEE标准化后,成为了业界通用的测试接口标准。

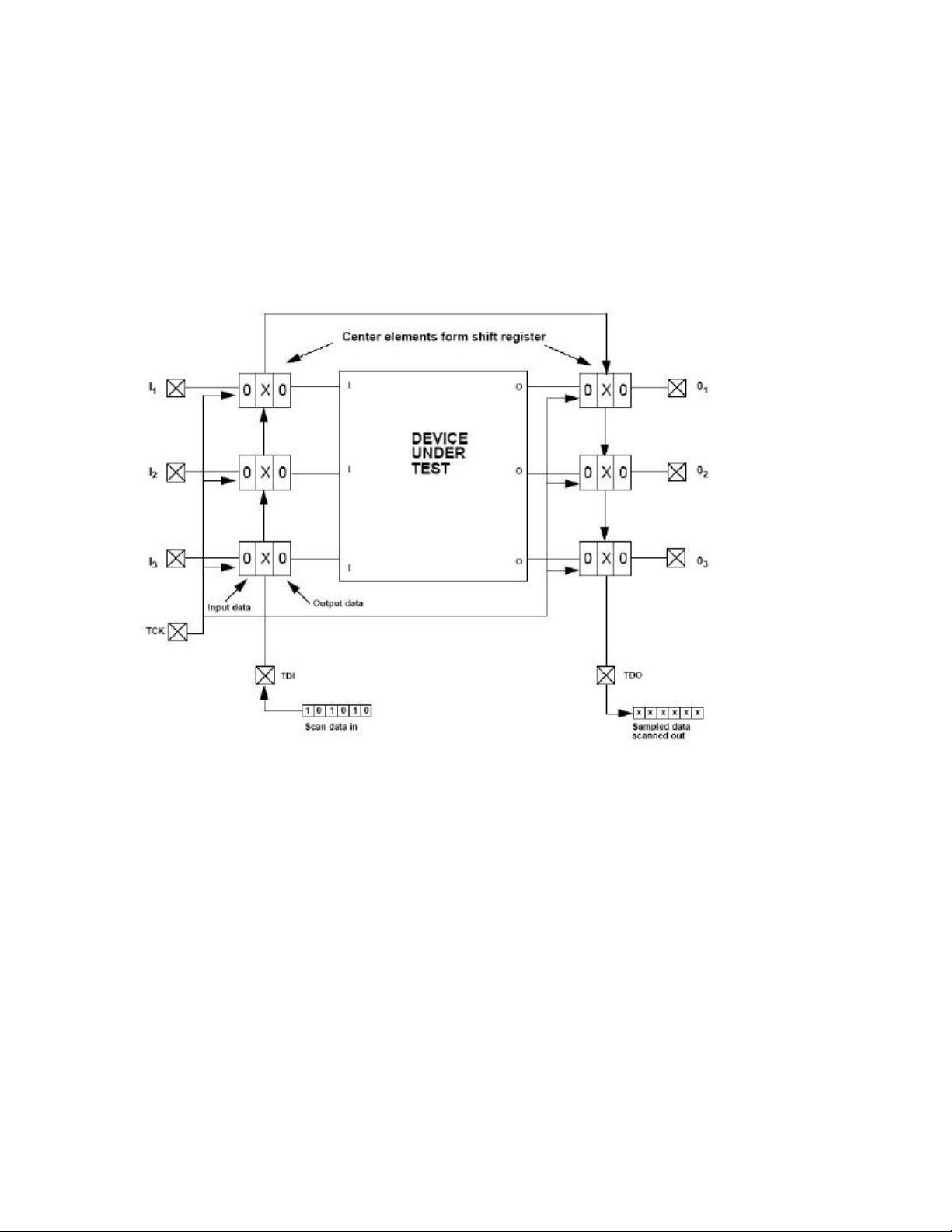

在JTAG测试中,边界扫描(Boundary-Scan)起着核心作用。这是一种技术,通过在芯片输入输出引脚附近添加移位寄存器单元,这些寄存器分布在芯片边缘,因此被称为边界扫描寄存器。在测试模式下,这些寄存器能隔离芯片与外部信号,允许对输入和输出进行观察和控制。对于输入,可以通过连接的边界扫描寄存器装载数据;对于输出,可以捕捉寄存器的内容来读取信号。在正常运行时,这些寄存器是透明的,不会影响芯片性能。

边界扫描链(Boundary-Scan Chain)是多个边界扫描寄存器单元串联形成的结构,通常由芯片本身提供,用于实现全面的测试功能。这些链可以序列地处理输入和输出信号,通过相应的时钟信号和控制信号进行操作。ARM7TDMI是一种特定的微处理器,其架构设计允许充分利用JTAG接口进行高效、精确的硬件级测试,这对于芯片的制造、调试和维护至关重要。

报告接着会详细介绍TAP的具体工作原理,包括它的组成部分如TAP控制逻辑、JTAG IDCODE、以及如何通过它来配置和控制目标系统,以便执行测试序列。此外,还会涉及如何使用TAP进行复位、内存访问和其他高级功能,这些都是理解ARM JTAG测试不可或缺的部分。

总结来说,本报告旨在为读者提供一个详尽的ARM JTAG测试理论框架,涵盖从标准定义到实际应用的各个环节,帮助读者掌握这一在嵌入式系统和集成电路设计中广泛应用的技术。

2716 浏览量

2175 浏览量

1147 浏览量