高性能异构计算:英文原版深度解析

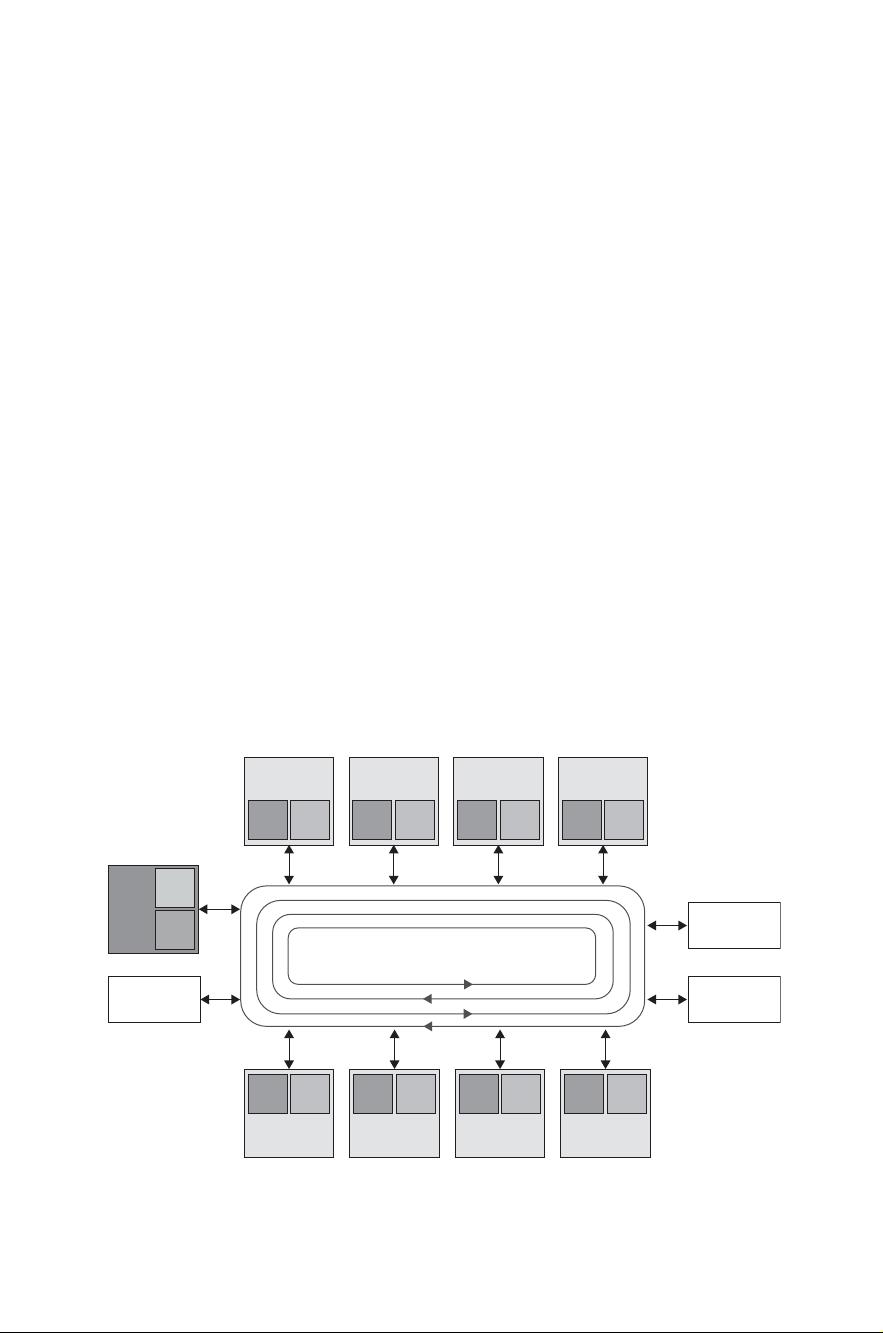

"High Performance Heterogeneous Computing" 本书是" Wiley Series on Parallel and Distributed Computing"系列中的一本,由Albert Y. Zomaya担任系列编辑。该书深入探讨了高性能异构计算的设计与实现策略,主要面向微电子领域的读者。异构计算是指在同一个系统中集成不同类型的处理器和硬件架构,如CPU、GPU、FPGA等,以实现更高效能和能效比。 在"High Performance Heterogeneous Computing"中,作者可能详细讨论了以下几个关键知识点: 1. 异构计算的基础:介绍异构计算的概念,包括其优势和挑战,以及为何在高性能计算领域越来越重要。这可能涵盖了如何通过混合使用不同处理器类型来优化特定工作负载的执行效率。 2. 系统设计:书中可能会涵盖异构系统的设计原则,包括如何分配任务给不同的处理器单元,如何构建高效的通信网络,以及如何考虑功耗和散热等因素。 3. 并行算法:高性能计算通常涉及到并行算法的使用。书中可能详细介绍了适用于异构环境的并行算法,如数据并行、任务并行和混合并行,以及如何针对特定硬件进行优化。 4. 软件框架与编程模型:可能涉及各种编程模型,如OpenMP、CUDA、OpenCL等,这些模型使得开发者能够更有效地利用异构硬件资源。此外,书中可能还讨论了跨平台编程和接口抽象的问题。 5. 性能评估与优化:书中可能包含对异构系统性能的评估方法,如基准测试和性能建模。同时,会讲解如何通过分析和调试来优化代码,提升系统的整体性能。 6. 应用案例:为了更好地理解理论概念,作者可能会提供实际应用案例,如在科学计算、图像处理、机器学习等领域中的异构计算实践。 7. 未来趋势与挑战:随着技术的不断进步,书中可能会展望异构计算的未来发展方向,如量子计算的融合、边缘计算的应用,以及在处理大数据和人工智能任务时面临的挑战。 "High Performance Heterogeneous Computing"这本书为读者提供了一个全面了解和掌握高性能异构计算的平台,无论是对于研究人员、工程师还是学生,都是一个宝贵的参考资料,帮助他们在微电子和高性能计算领域取得更深的理解和实践能力。

剩余283页未读,继续阅读

- 粉丝: 1

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++多态实现机制详解:虚函数与早期绑定

- Java多线程与异常处理详解

- 校园导游系统:无向图实现最短路径探索

- SQL2005彻底删除指南:避免重装失败

- GTD时间管理法:提升效率与组织生活的关键

- Python进制转换全攻略:从10进制到16进制

- 商丘物流业区位优势探究:发展战略与机遇

- C语言实训:简单计算器程序设计

- Oracle SQL命令大全:用户管理、权限操作与查询

- Struts2配置详解与示例

- C#编程规范与最佳实践

- C语言面试常见问题解析

- 超声波测距技术详解:电路与程序设计

- 反激开关电源设计:UC3844与TL431优化稳压

- Cisco路由器配置全攻略

- SQLServer 2005 CTE递归教程:创建员工层级结构

信息提交成功

信息提交成功