Altera IP核使用指南:官方详细资料

需积分: 0 55 浏览量

更新于2024-07-30

收藏 1MB PDF 举报

"altera公司 IP核 使用手册"

Altera公司是知名的可编程逻辑器件制造商,其产品主要包括FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)。在本使用手册中,重点介绍了Altera的IP(Intellectual Property)核,这是一种预先设计好的功能模块,可以被集成到用户的设计中,以实现特定的系统功能。IP核是现代电子设计自动化(EDA)中的重要组成部分,大大提高了设计效率和可靠性。

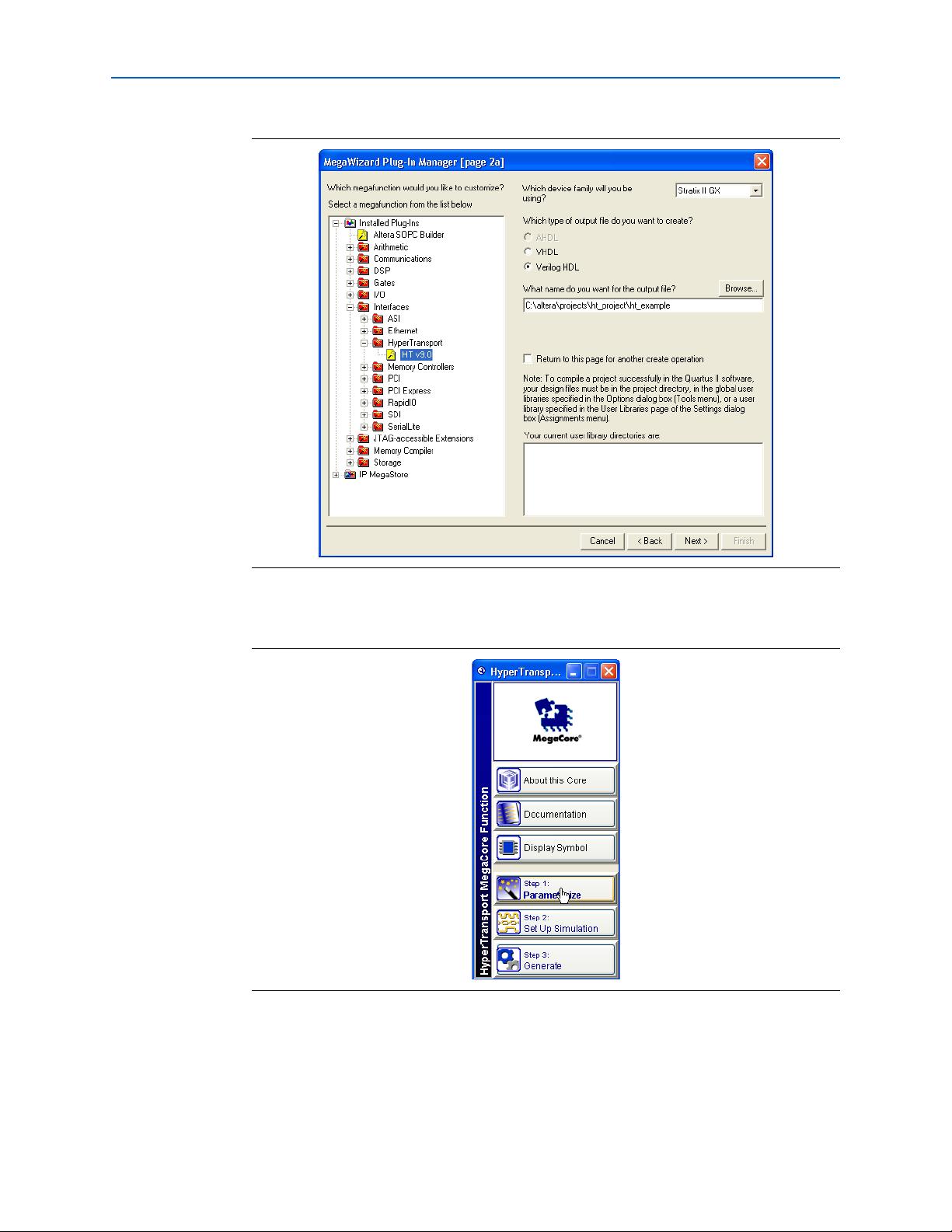

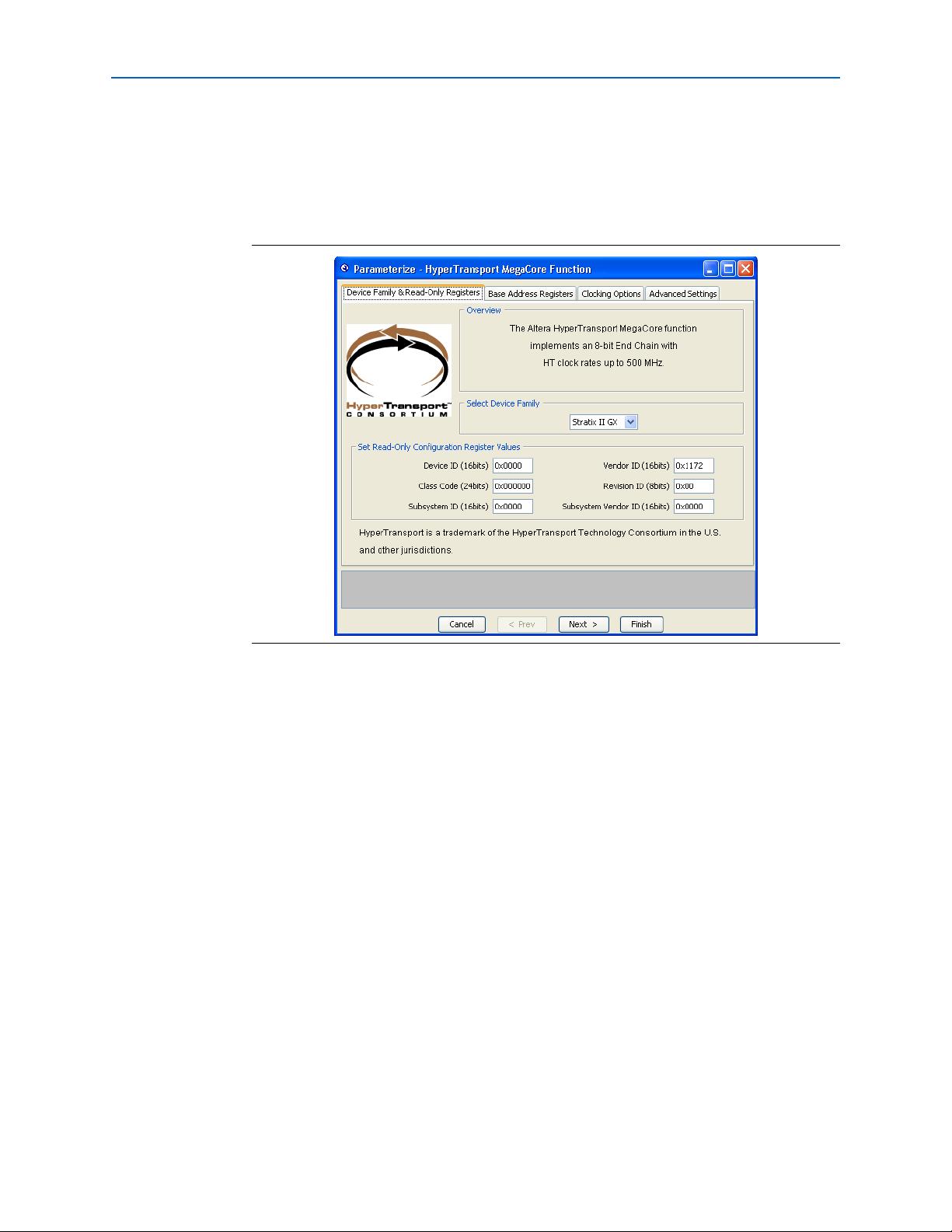

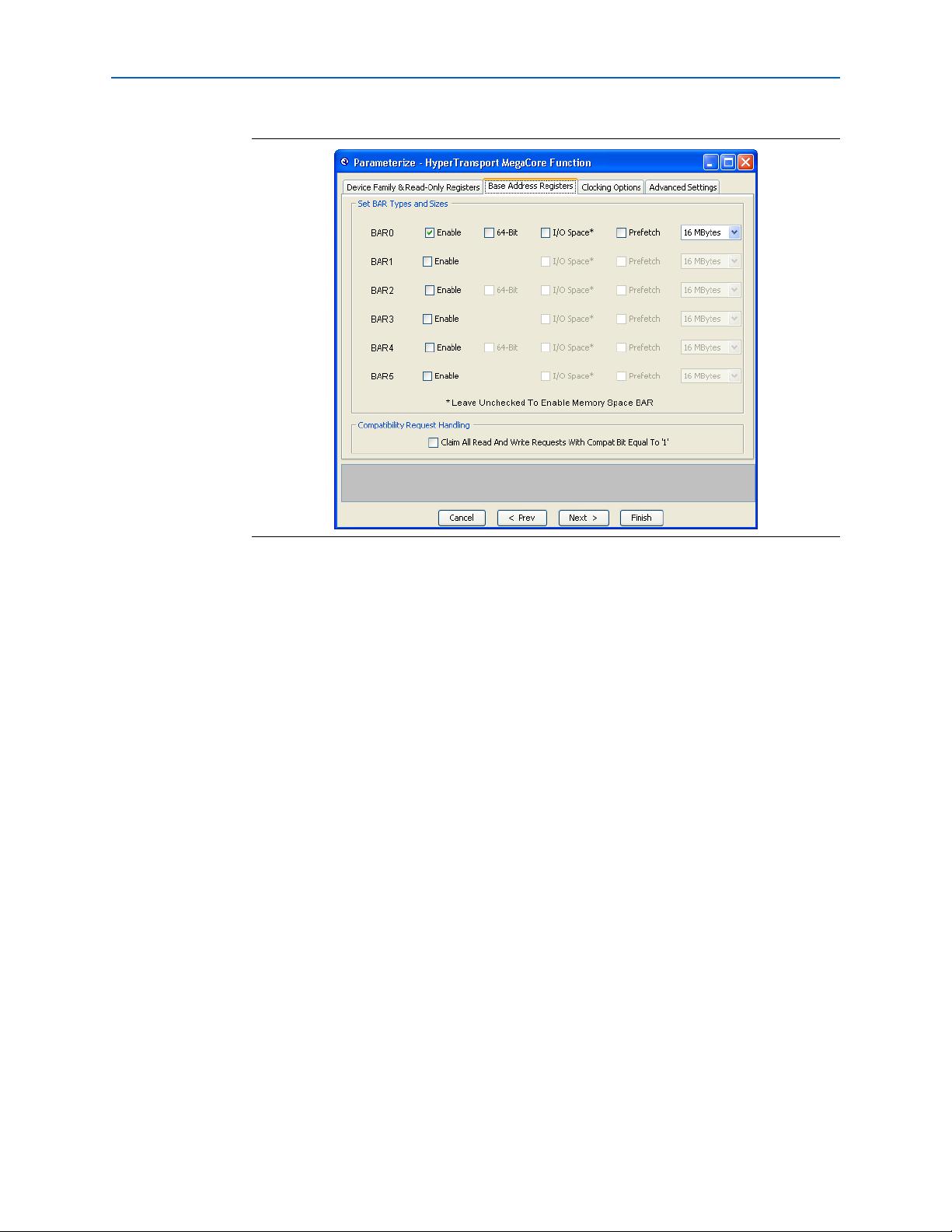

Altera的IP核库涵盖各种领域,如接口、时钟管理、数字信号处理、安全、存储器接口等。在本手册中提到的“HyperTransport MegaCore”是一个具体的IP核,它实现了HyperTransport协议,这是一种高性能、低延迟的互连技术,常用于构建高速系统总线,连接处理器、内存、I/O设备等。HyperTransport MegaCore的版本为9.0,文档日期为2009年3月,表明这是针对当时最新技术的IP核解决方案。

使用Altera的IP核,设计者能够快速集成标准协议和复杂功能,而无需从底层硬件描述语言(如Verilog或VHDL)开始编写代码。手册会详细介绍如何配置、集成以及验证这些IP核,包括设置参数、进行时序分析、综合和实现步骤。此外,手册可能还会涵盖错误处理、功耗优化和热管理等方面的内容。

值得注意的是,Altera IP核的使用需要遵守严格的知识产权(IP)保护规定,所有产品和服务名称都可能是Altera或其他公司的商标。在应用或使用手册中描述的任何信息、产品或服务时,必须遵循相应的法律条款。Altera对其半导体产品的性能按照标准保修条款进行保证,但保留随时更改产品和服务的权利,且不承担因应用或使用这些信息、产品或服务所产生的任何责任或赔偿,除非在书面协议中明确约定。

"Altera公司 IP核 使用手册" 是一份全面指导用户如何有效利用Altera IP核进行系统设计的重要参考资料,对于那些希望在 FPGA 或 CPLD 设计中集成高级功能的工程师来说,这是一份不可或缺的学习和参考材料。通过深入理解和熟练运用手册中的知识,设计师可以加速设计流程,提高设计质量,并确保项目满足最新的技术规格和行业标准。

2013-08-02 上传

2023-09-25 上传

2023-07-17 上传

2023-07-11 上传

2023-12-18 上传

2024-10-26 上传

2023-06-27 上传

wangkangzhuoyue

- 粉丝: 0

- 资源: 2

最新资源

- StarModAPI: StarMade 模组开发的Java API工具包

- PHP疫情上报管理系统开发与数据库实现详解

- 中秋节特献:明月祝福Flash动画素材

- Java GUI界面RPi-kee_Pilot:RPi-kee专用控制工具

- 电脑端APK信息提取工具APK Messenger功能介绍

- 探索矩阵连乘算法在C++中的应用

- Airflow教程:入门到工作流程创建

- MIP在Matlab中实现黑白图像处理的开源解决方案

- 图像切割感知分组框架:Matlab中的PG-framework实现

- 计算机科学中的经典算法与应用场景解析

- MiniZinc 编译器:高效解决离散优化问题

- MATLAB工具用于测量静态接触角的开源代码解析

- Python网络服务器项目合作指南

- 使用Matlab实现基础水族馆鱼类跟踪的代码解析

- vagga:基于Rust的用户空间容器化开发工具

- PPAP: 多语言支持的PHP邮政地址解析器项目