Verilog HDL设计8位二进制全加器教程

"这篇文档是关于使用Verilog HDL设计一个8位二进制全加器的教程,涉及QuartusⅡ软件的使用、时序仿真的学习以及实验步骤的详细说明。"

在计算机硬件设计中,二进制全加器是一个基本的逻辑电路,用于执行两个二进制数的加法操作,并考虑进位。在这个8位二进制全加器的设计中,主要目标是通过Verilog HDL语言实现这个功能,并通过 QuartusⅡ 工具进行编译、综合、适配和仿真,以验证设计的正确性。

Verilog HDL是一种硬件描述语言,它允许设计者以结构化的方式描述数字系统的逻辑行为。在设计8位全加器时,可以选择直接编写一个完整的8位全加器模块,或者利用例化语句(instance)调用1位全加器模块多次,以构建出8位的全加器。1位全加器可以处理两个输入位(A和B)和一个进位输入(CIN),并产生一个输出位和一个进位输出。

实验步骤包括以下几个关键部分:

1. **文件管理**:首先需要为项目创建一个文件夹,存放所有相关文件。

2. **代码编写**:在Verilog HDL环境中创建一个新的文件,编写全加器的代码。

3. **工程建立与编译**:保存文件并建立对应的工程,然后对整个设计进行编译,确保语法正确且没有错误。

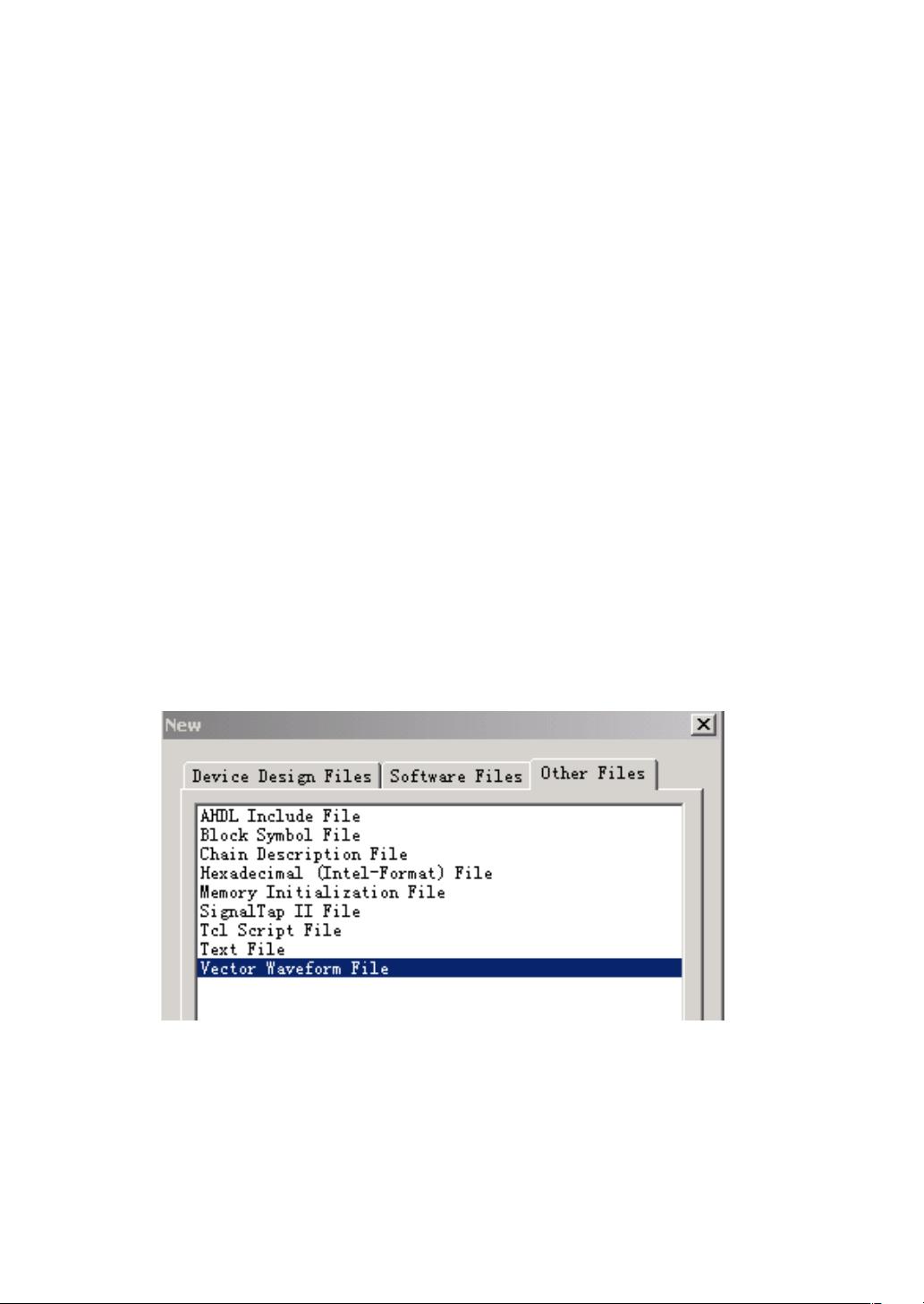

4. **时序仿真**:这一步是为了验证设计的功能。需要创建一个矢量波形文件,设置仿真时间长度,将设计的输入和输出信号添加到波形编辑器中,并编辑输入波形,设置不同的激励信号,以便观察输出响应。

5. **设置仿真参数**:在QuartusⅡ中,需要配置仿真控制设置,例如选择全时域显示,以观察整个仿真过程中的信号变化。

6. **运行仿真**:最后启动仿真,观察波形图以分析设计是否按照预期工作。此外,硬件测试也是验证设计正确性的另一种方法。

实验报告应包括设计流程的详细描述,如设计思路、代码实现和模块间的关系;同时提供仿真波形图以展示各个输入和输出信号随时间的变化;还需要进行时序分析,评估设计的速度性能和延迟特性。

参考程序中给出的`ADDER8B`模块是一个简单的8位全加器实现,它接收8位输入A和B,一个进位输入CIN,产生8位输出DOUT和一个进位输出COUT。通过直接相加A和B并加上CIN,可以得到9位的和,其中最高位作为进位输出,其余位作为输出。

这个实验不仅涵盖了二进制全加器的设计,还涉及了Verilog HDL编程、数字系统仿真以及硬件验证的基本流程,对于理解和掌握数字逻辑设计基础非常有帮助。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-05-24 上传

2023-05-02 上传

2023-05-02 上传

2023-05-02 上传

2024-09-29 上传

2024-10-19 上传