没有合适的资源?快使用搜索试试~ 我知道了~

首页"ZC706评估版介绍及开发板描述"

UG954 zc706评估版是一款由Xilinx推出的用于评估和开发项目的开发板。该开发板基于Zynq-7000系列XC7Z045 SoC芯片,具有多种功能和设计资源,可用于快速原型设计和验证。 UG954 zc706评估版用户指南提供了关于如何正确使用该开发板的详细说明。用户指南从硬件和软件方面介绍了zc706的特性和功能,并提供了配置和设置开发板的步骤。此外,用户指南还包括有关连接外部设备和扩展板的说明,并提供示例代码和项目示例,以帮助用户快速上手和了解开发板的功能。 UG954 zc706评估版具有丰富的硬件资源,包括具有高速转接器接口的FMC扩展插槽,可连接外部扩展板和设备,以满足不同的项目需求。开发板还配备了USB接口、网口、HDMI接口、音频接口等常用的接口,便于用户与外部设备进行连接和交互。此外,评估板还具有丰富的存储和扩展接口,包括DDR3 SDRAM插槽、QSPI闪存接口、SD卡插槽等,提供了灵活的存储和数据传输选项。 除了硬件资源,UG954 zc706评估版还支持多种软件开发环境,包括Xilinx的Vivado设计套件和SDK开发工具。用户可以使用Vivado设计套件进行FPGA逻辑设计和综合,使用SDK开发工具进行嵌入式软件开发和调试。评估板还提供了Linux系统的支持和相应的开发文档,方便用户进行基于Linux的软件开发和系统调试。 总之,UG954 zc706评估版是一款功能强大且灵活的开发板,适用于各种应用场景和项目需求。用户可以借助该评估板快速原型设计、验证和开发,加快项目的上市进程。通过详细的用户指南和丰富的资源支持,用户可以轻松上手并充分发挥开发板的功能。

资源详情

资源推荐

ZC706 Evaluation Board User Guide www.xilinx.com 16

UG954 (v1.8) August 6, 2019

Feature Descriptions

For additional information on Zynq-7000 SoC devices, see Zynq-7000 SoC Overview (DS190)

and Zynq-7000 SoC Technical Reference Manual (UG585

).

Device Configuration

the Zynq-7000 XC7Z045 SoC uses a multi-stage boot process that supports both a

non-secure and a secure boot. The PS is the master of the boot and configuration process.

For a secure boot, the PL must be powered on to enable the use of the security block

located within the PL, which provides 256-bit AES and SHA decryption/authentication.

The ZC706 evaluation board supports these configuration options:

• PS Configuration: Quad-SPI flash memory

• PS Configuration: Processor System Boot from SD Card (J30)

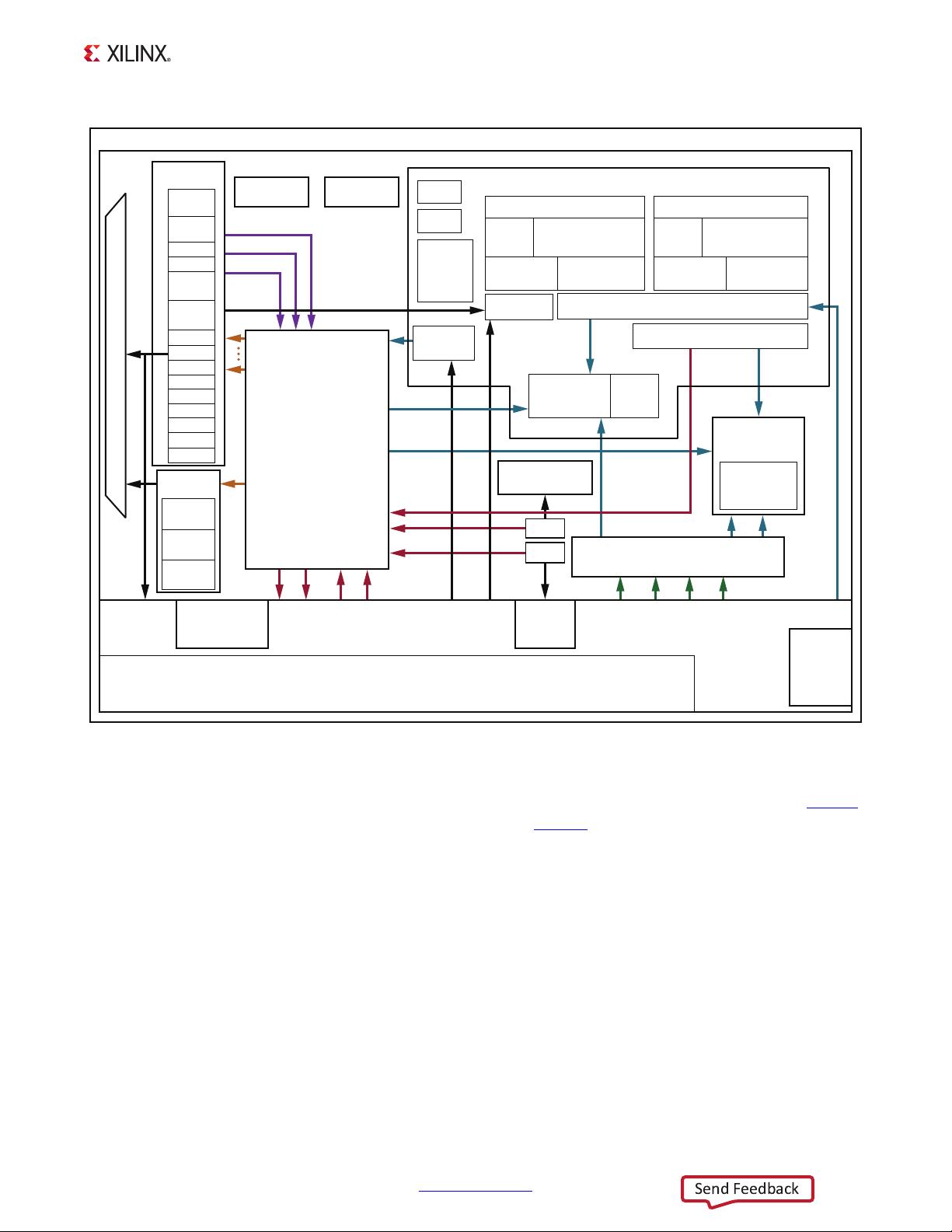

X-Ref Target - Figure 1-5

Figure 1-5: Zynq-7000 Block Diagram

2x USB

2x GigE

2x SD

Zynq-7000 AP SoC

I/O

Peripherals

IRQ

IRQ

EMIO

SelectIO

Resources

DMA 8

Channel

CoreSight

Components

Programmable Logic

DAP

DevC

SWDT

DMA

Sync

Notes:

1) Arrow direction shows control (master to slave)

2) Data flows in both directions: AXI 32-Bit/64-Bit, AXI 64-Bit, AXI 32-Bit, AHB 32-Bit, APB 32-Bit, Custom

ACP

256K

SRAM

Application Processor Unit

TTC

System-

Level

Control

Regs

GigE

CAN

SD

SDIO

UART

GPIO

UART

CAN

I2C

SRAM/

NOR

ONFI 1.0

NAND

Processing System

Memory

Interfaces

Q-SPI

CTRL

USB

GigE

I2C

USB

SD

SDIO

SPI

SPI

Programmable Logic to

Memory Interconnect

MMU

FPU and NEON Engine

Snoop Controller, AWDT, Timer

GIC

32 KB

I-Cache

ARM Cortex-A9

CPU

ARM Cortex-A9

CPU

MMU

FPU and NEON Engine

Config

AES/

SHA

XADC

12-Bit ADC

Memory

Interfaces

512 KB L2 Cache & Controller

OCM

Interconnect

DDR2/3,

LPDDR2

Controller

UG954_c1_04_100112

32 KB

D-Cache

32 KB

I-Cache

32 KB

D-Cache

MIO

Clock

Generation

Reset

Central

Interconnect

General-Purpose

Ports

High-Performance Ports

Send Feedback

ZC706 Evaluation Board User Guide www.xilinx.com 17

UG954 (v1.8) August 6, 2019

Feature Descriptions

• PL Configuration: USB JTAG configuration port (Digilent module U30)

• PL Configuration: Platform cable header J3 and flying lead header J62 JTAG

configuration ports

TIP: Designs using serial configuration based on Quad-SPI flash memory can take advantage of

low-cost commodity SPI flash memory.

The JTAG configuration option is selected by setting SW11 (PS) as shown in Table 1-2 and

SW4 (PL) as described in Programmable Logic JTAG Programming Options, page 33. SW11

is callout 29 in Figure 1-3.

For more information about Zynq-7000 SoC configuration settings, see Zynq-7000 SoC

Technical Reference Manual (UG585

).

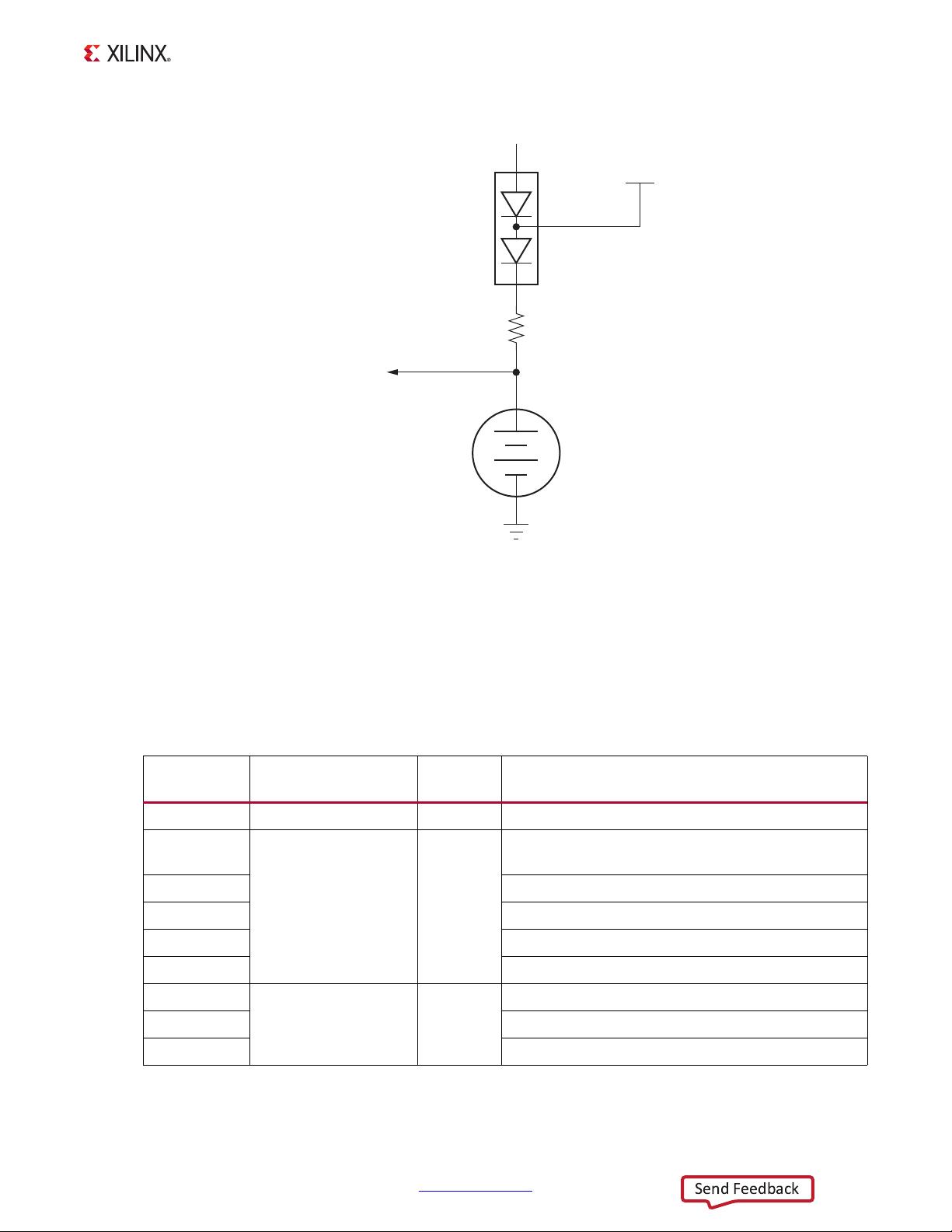

Encryption Key Backup Circuit

The XC7Z045 SoC U1 implements bitstream encryption key technology. The ZC706 board

provides the encryption key backup battery circuit shown in Figure 1-6. The Seiko TS518FE

rechargeable 1.5V lithium button-type battery B2 is soldered to the board with the positive

output connected to the XC7Z045 SoC U1 VCCBATT pin P9. The battery supply current

IBATT specification is 150 nA max when board power is off. B2 is charged from the VCCAUX

1.8V rail through a series diode with a typical forward voltage drop of 0.38V and 4.7 K

Ω

current limit resistor. The nominal charging voltage is 1.42V.

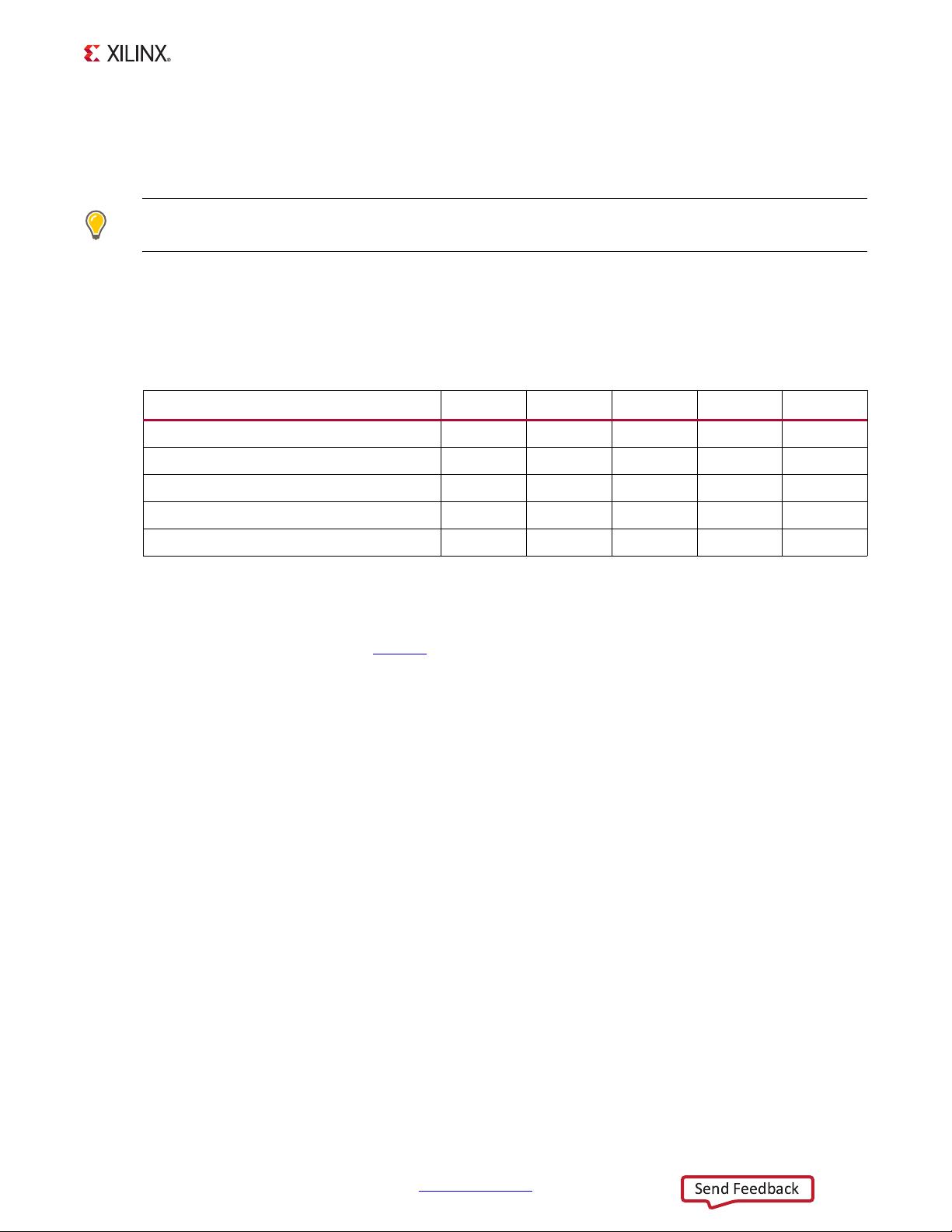

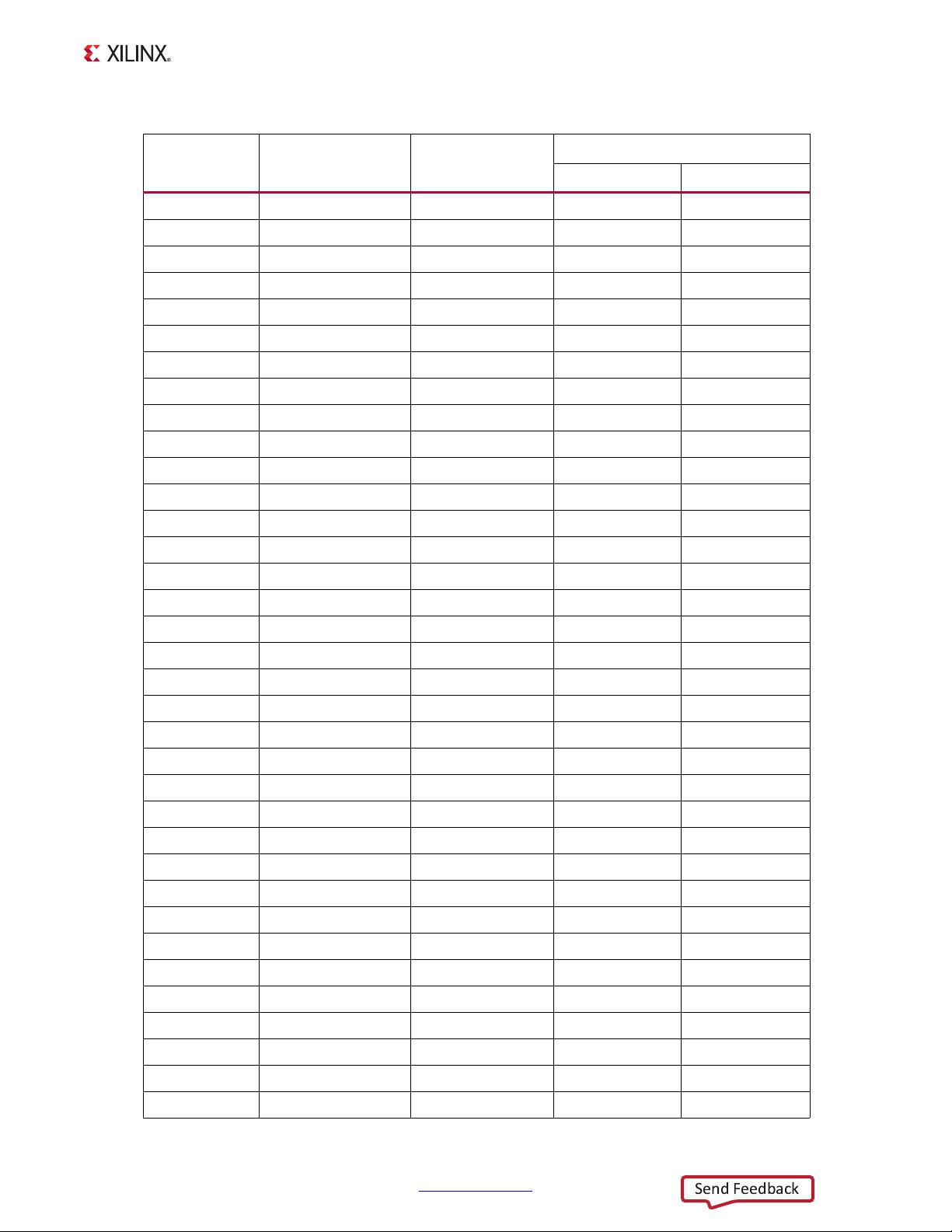

Table 1-2: Switch SW11 Configuration Option Settings

Boot Mode SW11.1 SW11.2 SW11.3 SW11.4 SW11.5

JTAG mode

(1)

00000

Independent JTAG mode

10000

QSPI mode

00010

SD mode

00110

MIO configuration pin

MIO2 MIO3 MIO4 MIO5 MIO6

Notes:

1. Default switch setting

Send Feedback

ZC706 Evaluation Board User Guide www.xilinx.com 18

UG954 (v1.8) August 6, 2019

Feature Descriptions

I/O Voltage Rails

There are eleven I/O banks available on the XC7Z045 SoC. The voltages applied to the

XC7Z045 SoC I/O banks used by the ZC706 evaluation board are listed in Table 1-3.

X-Ref Target - Figure 1-6

Figure 1-6: Encryption Key Backup Circuit

UG954_c1_05_041113

GND

2

1

B2

Lithium Battery

Seiko

TS518SE_FL35E

1.5V

2

1

3

BAS40-04

D7

40V

200 mW

NC

FPGA_VBATT

+

VCCAUX

R9

4.70K 1%

1/16W

To XC7Z045 AP SoC

U1 Pin P9

(VCCBATT)

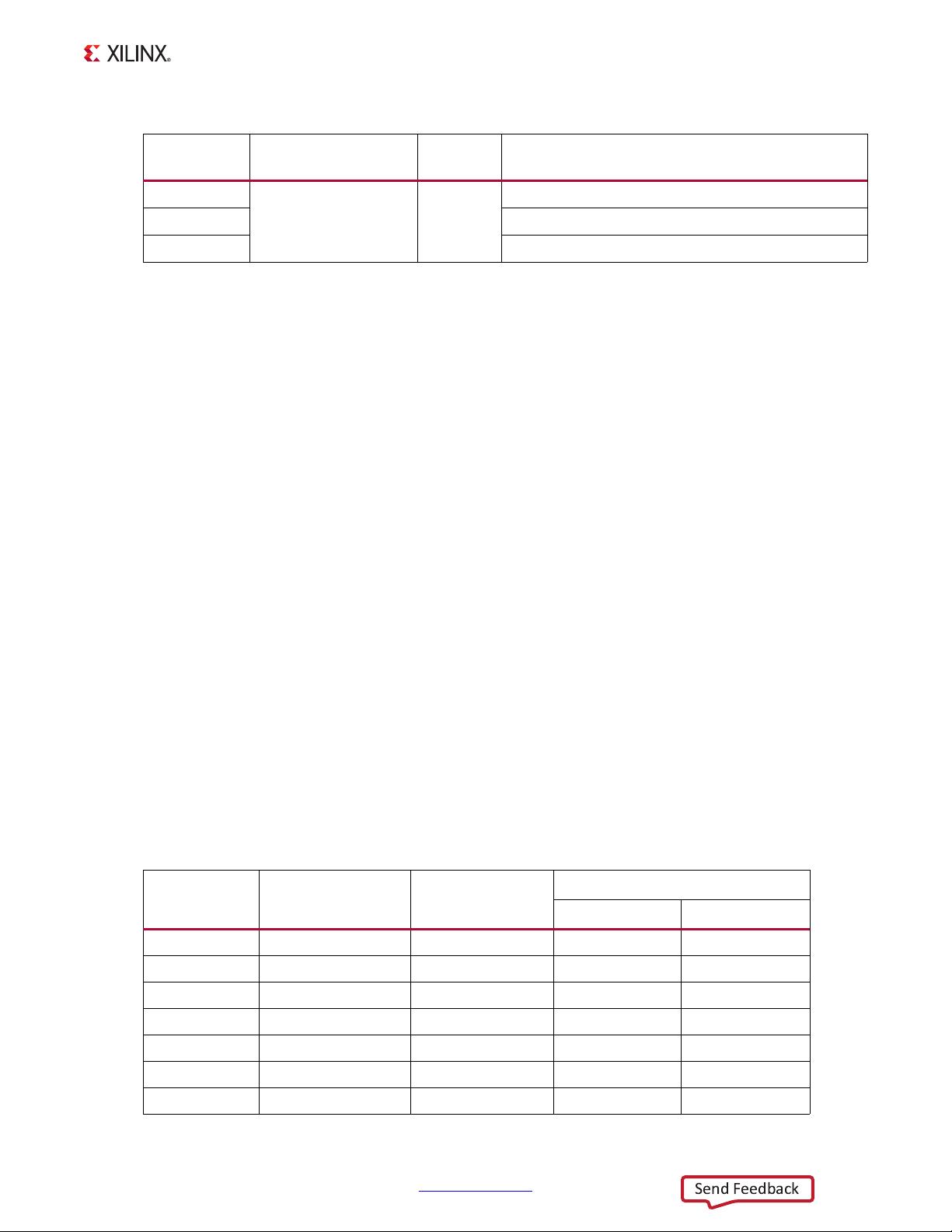

Table 1-3: I/O Voltage Rails

XC7Z045 (U1)

Bank

Net Name Voltage Connected To

PL Bank 0 VCC3V3_FPGA 3.3V SoC Configuration Bank 0

PL Bank 9

VADJ_FPGA 2.5V

PMOD, USER_SMA_CLOCK, SM_FAN, REC_CLOCK,

SFP_TX_DISABLE

PL Bank 10 FMC_LPC, PL_JTAG,GPIO

PL Bank 11 FMC_HPC, GPIO_LED, HDMI

PL Bank 12 FMC_LPC, HDMI

PL Bank 13 FMC_HPC, HDMI

PL Bank 33

VCC1V5_PL 1.5V

PL_DDR3_D[31:0]

PL Bank 34 PL_DDR3_A, SYSCLK

PL Bank 35 PL_DDR3_D[63:32], XADC

Send Feedback

ZC706 Evaluation Board User Guide www.xilinx.com 19

UG954 (v1.8) August 6, 2019

Feature Descriptions

DDR3 SODIMM Memory (PL)

[Figure 1-3, callout 2]

The memory module at J1 is a 1 GB DDR3 small outline dual-inline memory module

(SODIMM). It provides volatile synchronous dynamic random access memory (SDRAM) for

storing user code and data.

• Part number: MT8JTF12864HZ-1G6G1 (Micron Technology)

• Supply voltage: 1.5V

• Datapath width: 64 bits

• Data rate: Up to 1,600 MT/s

The ZC706 XC7Z045 SoC PL DDR interface performance is documented in the Zynq-7000

SoC (Z-7030, 035, 045, and Z-7100): DC and AC Switching Characteristics Data Sheet

(DS191)[Ref 2].

The DDR3 interface is implemented across the PL-side I/O banks. Bank 33 and bank 35 have

a dedicated DCI VRP/N resistor connection. An external 0.75V reference VTTREF_SODIMM is

provided for data interface banks. Any interface connected to these banks that requires the

VTTREF voltage must use this FPGA voltage reference. The connections between the DDR3

memory and the SoC are listed in Table 1-4.

PS Bank 500

VCCP1V8 1.8V

QSPI0,QSPI1

PS Bank 501 PHY_IF,SDIO_IF,USB_IF

PS Bank 502 PS_DDR3_IF

Notes:

1. The ZC706 evaluation board is shipped with V

ADJ

set to 2.5V.

Table 1-4: DDR3 SODIMM Socket J1 Connections to the XC7Z045 SoC

XC7Z045 (U1)

Pin

Net Name I/O Standard

DDR3 SODIMM Memory J1

Pin Number Pin Name

E10 PL_DDR3_A0 SSTL15 98 A0

B9 PL_DDR3_A1 SSTL15 97 A1

E11 PL_DDR3_A2 SSTL15 96 A2

A9 PL_DDR3_A3 SSTL15 95 A3

D11 PL_DDR3_A4 SSTL15 92 A4

B6 PL_DDR3_A5 SSTL15 91 A5

F9 PL_DDR3_A6 SSTL15 90 A6

Table 1-3: I/O Voltage Rails (Cont’d)

XC7Z045 (U1)

Bank

Net Name Voltage Connected To

Send Feedback

ZC706 Evaluation Board User Guide www.xilinx.com 20

UG954 (v1.8) August 6, 2019

Feature Descriptions

E8 PL_DDR3_A7 SSTL15 86 A7

B10 PL_DDR3_A8 SSTL15 89 A8

J8 PL_DDR3_A9 SSTL15 85 A9

D6 PL_DDR3_A10 SSTL15 107 A10/AP

B7 PL_DDR3_A11 SSTL15 84 A11

H12 PL_DDR3_A12 SSTL15 83 A12_BC_N

A10 PL_DDR3_A13 SSTL15 119 A13

G11 PL_DDR3_A14 SSTL15 80 A14

C6 PL_DDR3_A15 SSTL15 78 A15

F8 PL_DDR3_BA0 SSTL15 109 BA0

H7 PL_DDR3_BA1 SSTL15 108 BA1

A7 PL_DDR3_BA2 SSTL15 79 BA2

L1 PL_DDR3_D0 SSTL15 5 DQ0

L2 PL_DDR3_D1 SSTL15 7 DQ1

K5 PL_DDR3_D2 SSTL15 15 DQ2

J4 PL_DDR3_D3 SSTL15 17 DQ3

K1 PL_DDR3_D4 SSTL15 4 DQ4

L3 PL_DDR3_D5 SSTL15 6 DQ5

J5 PL_DDR3_D6 SSTL15 16 DQ6

K6 PL_DDR3_D7 SSTL15 18 DQ7

G6 PL_DDR3_D8 SSTL15 21 DQ8

H4 PL_DDR3_D9 SSTL15 23 DQ9

H6 PL_DDR3_D10 SSTL15 33 DQ10

H3 PL_DDR3_D11 SSTL15 35 DQ11

G1 PL_DDR3_D12 SSTL15 22 DQ12

H2 PL_DDR3_D13 SSTL15 24 DQ13

G5 PL_DDR3_D14 SSTL15 34 DQ14

G4 PL_DDR3_D15 SSTL15 36 DQ15

E2 PL_DDR3_D16 SSTL15 39 DQ16

E3 PL_DDR3_D17 SSTL15 41 DQ17

D4 PL_DDR3_D18 SSTL15 51 DQ18

E5 PL_DDR3_D19 SSTL15 53 DQ19

F4 PL_DDR3_D20 SSTL15 40 DQ20

F3 PL_DDR3_D21 SSTL15 42 DQ21

D1 PL_DDR3_D22 SSTL15 50 DQ22

Table 1-4: DDR3 SODIMM Socket J1 Connections to the XC7Z045 SoC (Cont ’d)

XC7Z045 (U1)

Pin

Net Name I/O Standard

DDR3 SODIMM Memory J1

Pin Number Pin Name

Send Feedback

剩余102页未读,继续阅读

Flowers、Flow

- 粉丝: 1

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++多态实现机制详解:虚函数与早期绑定

- Java多线程与异常处理详解

- 校园导游系统:无向图实现最短路径探索

- SQL2005彻底删除指南:避免重装失败

- GTD时间管理法:提升效率与组织生活的关键

- Python进制转换全攻略:从10进制到16进制

- 商丘物流业区位优势探究:发展战略与机遇

- C语言实训:简单计算器程序设计

- Oracle SQL命令大全:用户管理、权限操作与查询

- Struts2配置详解与示例

- C#编程规范与最佳实践

- C语言面试常见问题解析

- 超声波测距技术详解:电路与程序设计

- 反激开关电源设计:UC3844与TL431优化稳压

- Cisco路由器配置全攻略

- SQLServer 2005 CTE递归教程:创建员工层级结构

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功