VHDL实现的80C186XL DRAM控制器设计

120 浏览量

更新于2024-09-03

收藏 186KB PDF 举报

"基于VHDL的DRAM控制器设计,利用80C186XL的时序特征,采用CPLD技术实现"

在嵌入式系统设计中,存储器的选择和管理是一个关键环节。动态随机存取内存(DRAM)由于其大容量和低成本的优势,常被用于需要大量存储空间的场合。然而,DRAM的复杂时序要求使得设计一个有效的控制器成为挑战。本文介绍了一种创新的方法,通过使用VHDL语言和复杂可编程逻辑器件(CPLD)来设计一个DRAM控制器,以适应80C186XL 16位嵌入式微处理器。

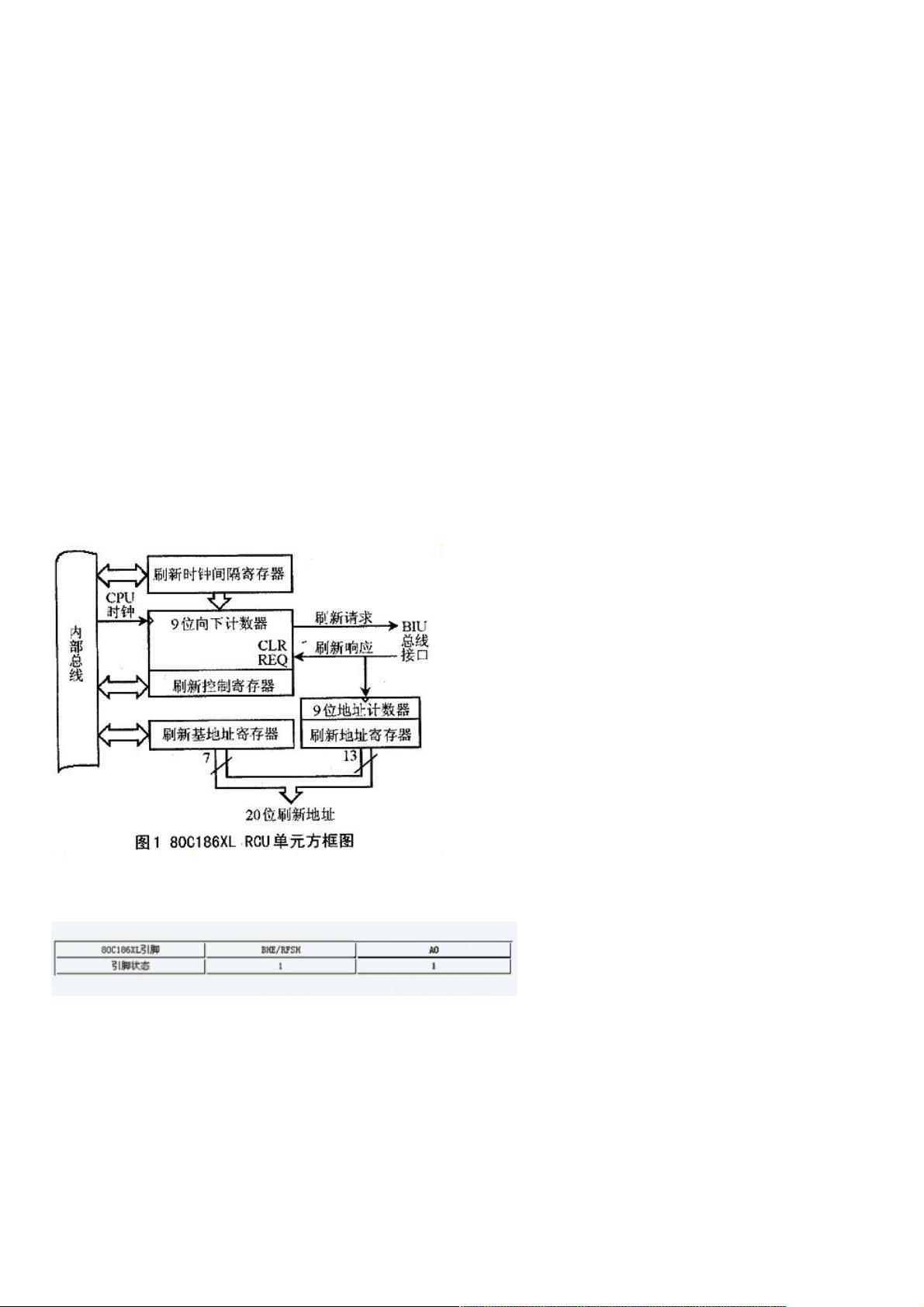

80C186XL是一款广泛应用的嵌入式微处理器,其内部集成了DRAM刷新控制单元(RCU),能自动产生刷新总线周期,工作在处理器的增益模式下。用户可以通过编程设置RCU,使其向总线接口单元(BIU)发送存储器读请求,对特定的存储器范围执行刷新操作。BIU在接收到指令后,会在合适的时机执行刷新周期,选择相应的DRAM存储器片。

在设计DRAM控制器时,考虑了80C186XL的时序特性。RCU单元包括一个9位递减定时计数器、一个9位地址计数器、三个控制寄存器和接口逻辑。当RCU被激活时,定时计数器每经过一个CLKOUT周期减1,直到计数为1时,触发刷新总线请求,然后重新加载并继续计数。刷新周期具有高优先级,只要80C186XL的总线空闲,就会执行刷新操作。

设计过程中,刷新总线周期被视为“伪读”周期,它在总线上的表现与普通读周期类似,区别在于没有数据传输。通过BHE/RFSH和A0引脚的状态,可以区分出刷新周期。表1提供了刷新周期引脚状态的详细信息,而图2则描绘了刷新总线周期的时序要求。

在80C186XL的DRAM控制器设计中,关键在于理解和满足DRAM的访问时间、等待状态和刷新方法等时序要求。例如,访问时间是指从发出读/写命令到数据有效的时间间隔;等待状态可能需要在某些操作前插入额外的时钟周期;而刷新方法则涉及如何定期刷新DRAM以保持数据完整性。控制器必须确保这些时序条件得到满足,否则可能会导致数据丢失或系统不稳定。

VHDL作为一种硬件描述语言,允许设计师以更接近自然语言的方式描述硬件逻辑,便于实现复杂的时序控制逻辑。CPLD则提供了灵活且可扩展的硬件平台,可以快速原型化和测试设计。通过VHDL编程和CPLD实现,可以精确控制DRAM的刷新过程,确保系统稳定运行,同时降低了设计复杂性和成本。

本文提出的基于VHDL的DRAM控制器设计方法,结合80C186XL的特性,利用CPLD技术,提供了一种高效、经济的解决策略,使得嵌入式系统能够更好地管理和使用DRAM存储器,满足大容量存储需求的同时,保证了系统的可靠性和性能。

2020-11-14 上传

2020-10-21 上传

2020-08-31 上传

2020-08-09 上传

2022-09-24 上传

点击了解资源详情

点击了解资源详情

2020-08-27 上传

2010-01-05 上传

weixin_38611388

- 粉丝: 10

- 资源: 971

最新资源

- Haskell编写的C-Minus编译器针对TM架构实现

- 水电模拟工具HydroElectric开发使用Matlab

- Vue与antd结合的后台管理系统分模块打包技术解析

- 微信小游戏开发新框架:SFramework_LayaAir

- AFO算法与GA/PSO在多式联运路径优化中的应用研究

- MapleLeaflet:Ruby中构建Leaflet.js地图的简易工具

- FontForge安装包下载指南

- 个人博客系统开发:设计、安全与管理功能解析

- SmartWiki-AmazeUI风格:自定义Markdown Wiki系统

- USB虚拟串口驱动助力刻字机高效运行

- 加拿大早期种子投资通用条款清单详解

- SSM与Layui结合的汽车租赁系统

- 探索混沌与精英引导结合的鲸鱼优化算法

- Scala教程详解:代码实例与实践操作指南

- Rails 4.0+ 资产管道集成 Handlebars.js 实例解析

- Python实现Spark计算矩阵向量的余弦相似度