实时嵌入式系统讲解:内存层次与模型

需积分: 15 3 浏览量

更新于2024-07-23

收藏 3.31MB PDF 举报

"Real-time embedded system - Stevens Institute of Technology CPE555A课程讲座"

在实时嵌入式系统这个主题中,我们关注的是在Stevens Institute of Technology的CPE555A课程中讨论的相关概念。这门课程可能涉及了实时嵌入式系统的各个方面,包括但不限于系统设计、性能优化以及实时性要求。

1. **行政事务**

课程中提到了已发布的作业和中期考试安排。这意味着学生需要关注课程进度,并在指定日期前完成作业,而中期考试则是在10月15日进行。

2. **转发机制**

转发机制是处理器内部的一种策略,用于处理数据流中的延迟问题。在多级流水线CPU中,如果一个指令的结果需要立即被后续指令使用,而不是等待常规的数据写回周期,转发机制会将结果直接传递给后续阶段,以减少延迟并提高执行效率。

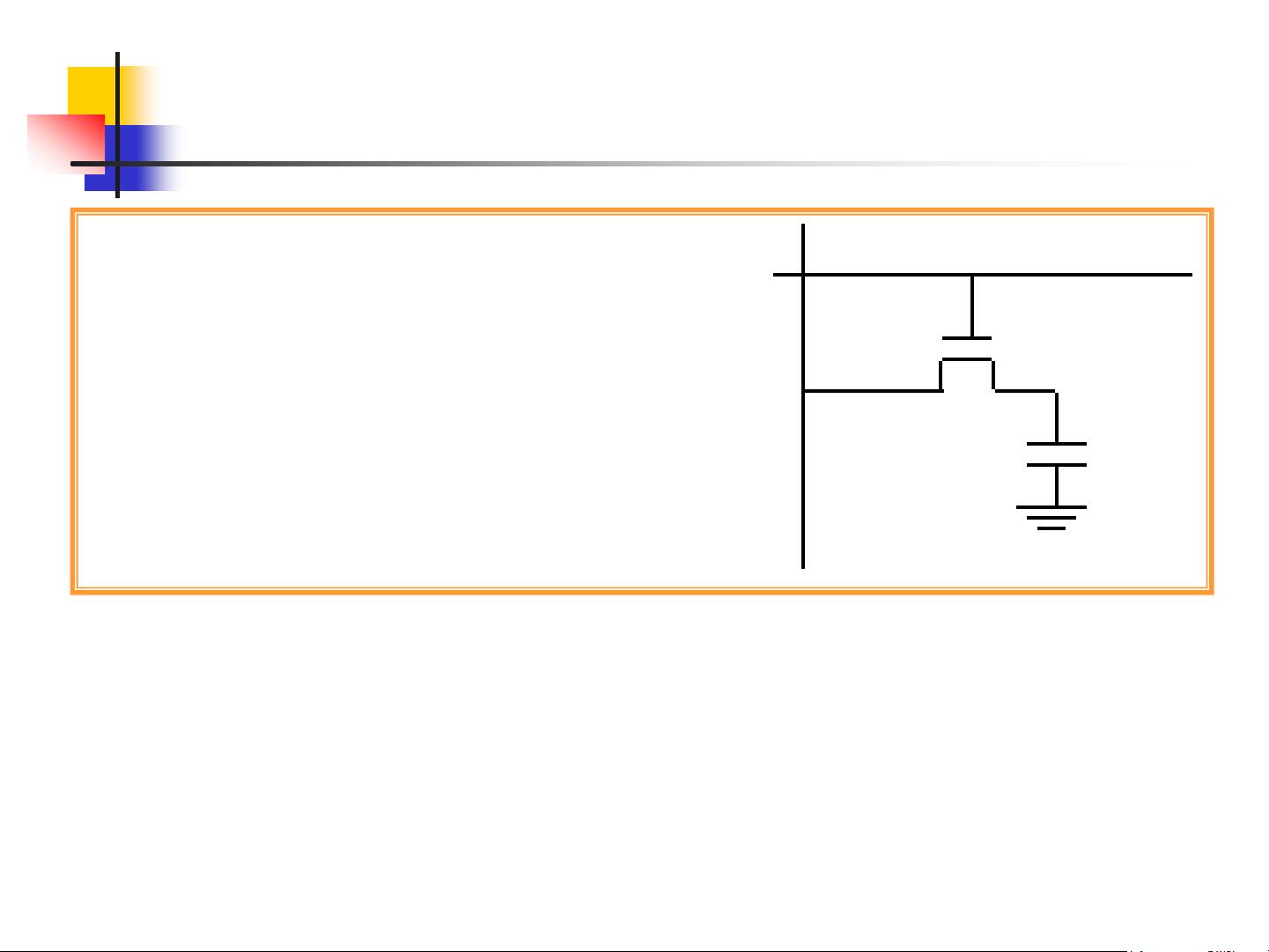

3. **内存层次结构**

讨论了内存层次结构,这是计算机系统设计的关键部分,包括缓存(Cache)、主内存(RAM)和外部存储器等。内存层次结构旨在通过将频繁访问的数据放在快速但昂贵的存储器中,减少访问时间,提高整体性能。

4. **内存模型**

内存模型描述了程序如何访问和管理内存,包括读取、写入和同步操作。在实时嵌入式系统中,内存模型的选择和实现对系统的响应时间和确定性有着重要影响。

5. **数据冲突(Data Hazard)**

数据冲突,特别是RAW(Read-After-Write)冲突,是处理器执行时可能出现的问题。例如,一个指令正在写入寄存器R1,而后续的指令需要在写回之前使用R1的值。这种情况可能导致指令执行的延迟,因为必须等待写回周期完成。课程中可能讲解了解决此类冲突的策略,如硬件预测和分支目标缓冲区(BTB)等。

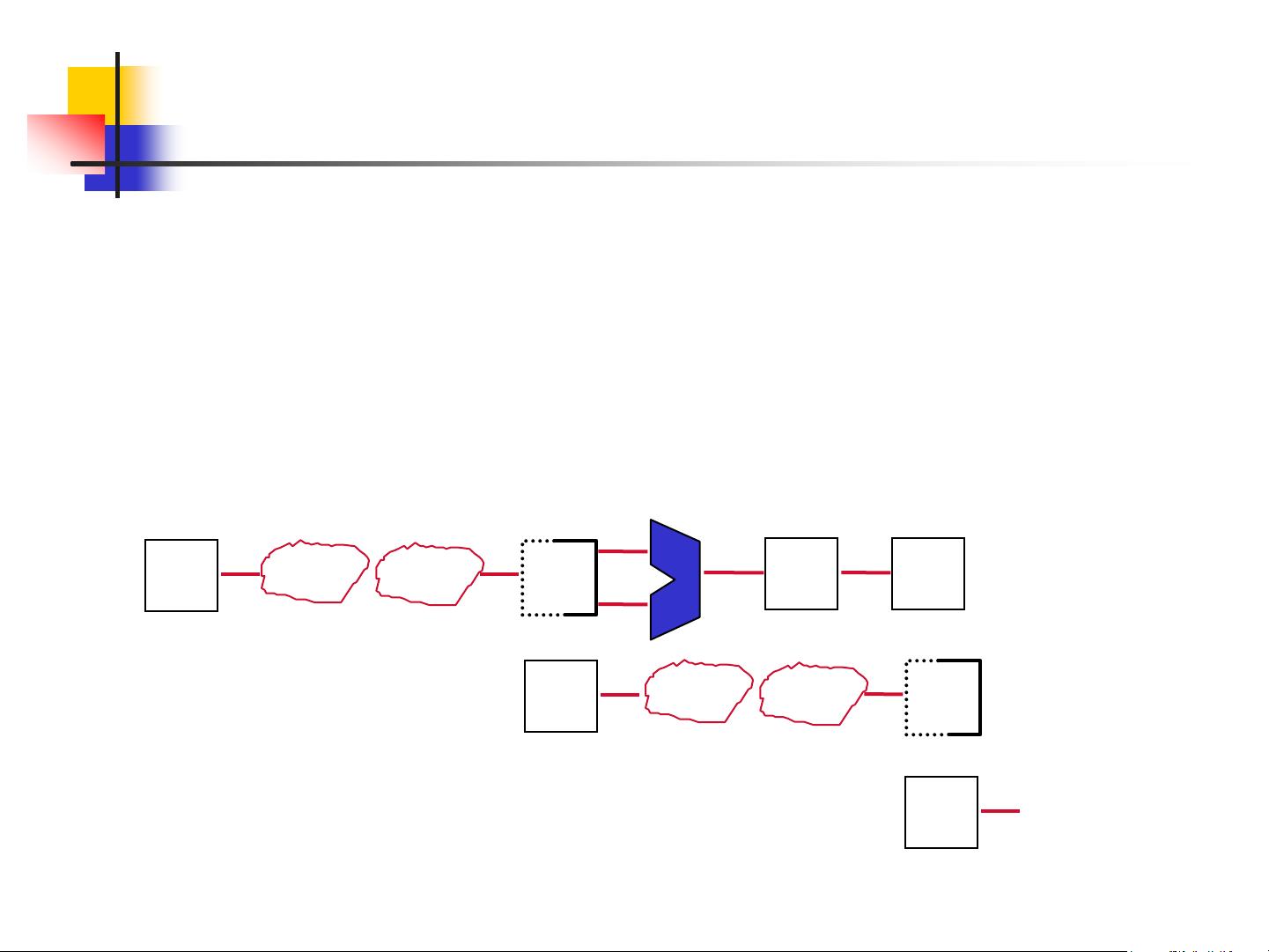

6. **处理器流水线**

图片展示了经典的五级流水线架构(IF/ID、ID/EX、EX/MEM、MEM/WB),每个阶段对应指令处理的不同步骤。数据冲突可能会导致流水线暂停或“阻塞”,影响吞吐量。讲师可能详细解释了如何通过各种技术如转发和预取来优化流水线性能。

7. **实时性**

在实时嵌入式系统中,系统必须在预定的时间内完成任务,否则可能会造成严重后果。因此,理解和解决这些数据冲突对于满足严格的实时约束至关重要。

通过这门课程,学生可以深入理解实时嵌入式系统的内部工作原理,学习如何设计和优化系统以满足严格的实时性能需求。这包括了硬件层面的微架构优化,以及软件层面的任务调度和内存管理策略。

2018-09-11 上传

2017-12-30 上传

2009-09-07 上传

2023-05-24 上传

2023-05-10 上传

2023-04-02 上传

2023-04-30 上传

2023-03-30 上传

2024-07-20 上传

慕容羽倩

- 粉丝: 1

- 资源: 1

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析