Section 1.2 Issues in Digital Integrated Circuit Design 17

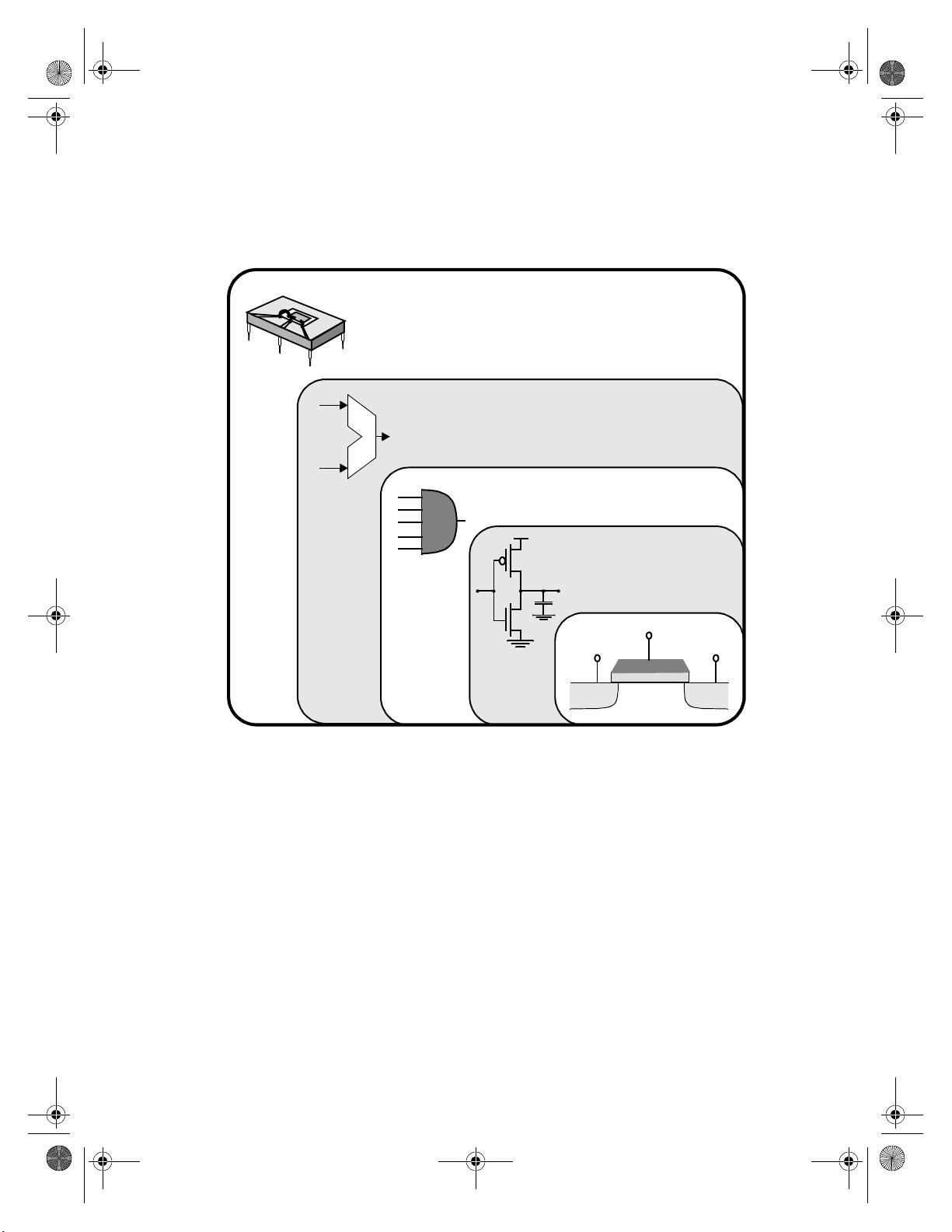

instance, apparent in the layout of the Pentium ® 4 processor (Figure 1.5b). The integer

and floating-point unit, just to name a few, contain large sections designed using the so-

called standard cell approach. In this approach, logic gates are placed in rows of cells of

equal height and interconnected using routing channels. The layout of such a block can be

generated automatically given that a library of cells is available.

The preceding analysis demonstrates that design automation and modular design

practices have effectively addressed some of the complexity issues incurred in contempo-

rary digital design. This leads to the following pertinent question. If design automation

solves all our design problems, why should we be concerned with digital circuit design at

all? Will the next-generation digital designer ever have to worry about transistors or para-

sitics, or is the smallest design entity he will ever consider the gate and the module?

The truth is that the reality is more complex, and various reasons exist as to why an

insight into digital circuits and their intricacies will still be an important asset for a long

time to come.

• First of all, someone still has to design and implement the module libraries. Semi-

conductor technologies continue to advance from year to year. Until one has devel-

oped a fool-proof approach towards “porting” a cell from one technology to another,

each change in technology—which happens approximately every two

years—requires a redesign of the library.

• Creating an adequate model of a cell or module requires an in-depth understanding

of its internal operation. For instance, to identify the dominant performance parame-

ters of a given design, one has to recognize the critical timing path first.

• The library-based approach works fine when the design constraints (speed, cost or

power) are not stringent. This is the case for a large number of application-specific

designs, where the main goal is to provide a more integrated system solution, and

performance requirements are easily within the capabilities of the technology.

Unfortunately for a large number of other products such as microprocessors, success

hinges on high performance, and designers therefore tend to push technology to its

limits. At that point, the hierarchical approach tends to become somewhat less

attractive. To resort to our previous analogy to software methodologies, a program-

mer tends to “customize” software routines when execution speed is crucial; com-

pilers—or design tools—are not yet to the level of what human sweat or ingenuity

can deliver.

• Even more important is the observation that the abstraction-based approach is only

correct to a certain degree. The performance of, for instance, an adder can be sub-

stantially influenced by the way it is connected to its environment. The interconnec-

tion wires themselves contribute to delay as they introduce parasitic capacitances,

resistances and even inductances. The impact of the interconnect parasitics is bound

to increase in the years to come with the scaling of the technology.

• Scaling tends to emphasize some other deficiencies of the abstraction-based model.

Some design entities tend to be global or external (to resort anew to the software

analogy). Examples of global factors are the clock signals, used for synchronization

in a digital design, and the supply lines. Increasing the size of a digital design has a

chapter1.fm Page 17 Friday, January 18, 2002 8:58 AM